Verilog HDL硬件基本描述单位模块

描述

模块是Verilog 的基本描述单位,用于描述某个设计的功能或结构及其与其他模块通信的外部端口。一个设计的结构可使用开关级原语、门级原语和用户定义的原语方式描述; 设计的数据流行为使用连续赋值语句进行描述; 时序行为使用过程结构描述。一个模块可以在另一个模块中使用。

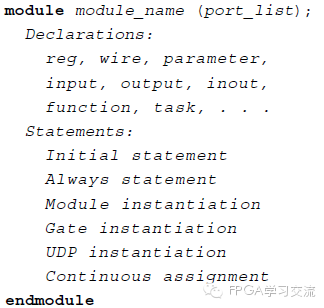

一个模块的基本语法如下:

说明部分用于定义不同的项,例如模块描述中使用的寄存器和参数。语句定义设计的功能和结构。说明部分和语句可以散布在模块中的任何地方;但是变量、寄存器、线网和参数等的说明部分必须在使用前出现。为了使模块描述清晰和具有良好的可读性, 最好将所有的说明部分放在语句前。本书中的所有实例都遵守这一规范。

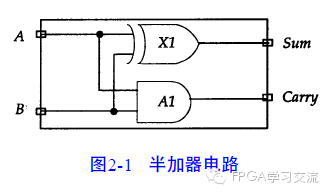

图2 - 1为建模一个半加器电路的模块的简单实例。

模块的名字是H a l f A d d e r。模块有4个端口: 两个输入端口A和B,两个输出端口S u m和C a rry。由于没有定义端口的位数, 所有端口大小都为1位;同时, 由于没有各端口的数据类型说明, 这四个端口都是线网数据类型。模块包含两条描述半加器数据流行为的连续赋值语句。从这种意义上讲,这些语句在模块中出现的顺序无关紧要,这些语句是并发的。每条语句的执行顺序依赖于发生在变量A和B上的事件。

在模块中,可用下述方式描述一个设计:

1) 数据流方式;

2) 行为方式;

3) 结构方式;

4) 上述描述方式的混合。

原文标题:Verilog HDL硬件描述语言-模块

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

二十进制编码器及Verilog HDL描述 Verilog HDL程序的基本结构及特点2023-08-28 5643

-

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计2022-08-31 3130

-

Verilog HDL verilog hdl和vhdl的区别2021-07-23 12311

-

如何使用Verilog HDL描述可综合电路?2021-04-04 5171

-

Verilog教程之Verilog HDL程序设计语句和描述方式2020-12-09 1349

-

Verilog HDL硬件描述语言_行为建模2016-04-25 758

-

verilog+hdl硬件描述语言2013-08-12 2442

-

Verilog_HDL硬件描述语言2013-02-26 4808

-

Verilog HDL硬件描述语言2013-01-13 4667

-

Verilog HDL语言简介2010-02-09 4193

-

什么是Verilog HDL?2009-01-18 4626

全部0条评论

快来发表一下你的评论吧 !