FPGA有哪些主要配置方式?

描述

最近完成了Arria10的原理图设计,想做一些记录,下面是关于FPGA配置的一些方式。

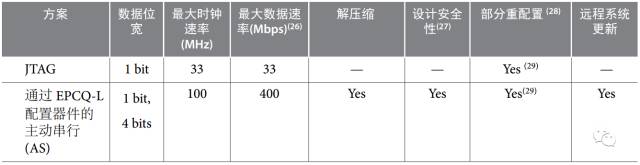

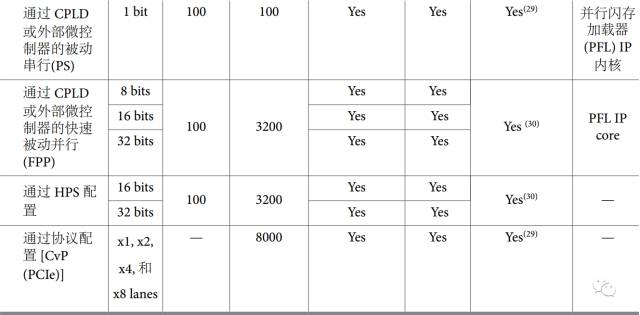

MSEL

将 MSEL 管脚直接连接到VCCPGM 或 GND,不需使用任何的上拉或下拉电阻,即可选择出所需的

配置方案

• 不要通过微处理器或其他器件驱动 MSEL 管脚。

• 对“通过 HPS 的配置”(Configurationvia HPS)使用 PS 或 FPP MSEL 管脚设置。

三种主要的配置方式

1、主动配置方式(AS)

2、被动配置方式(PS)

3、JTAG方式

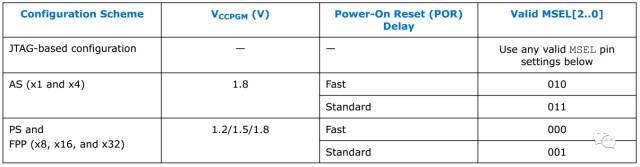

1、AS模式(active serial configuration mode):FPGA器件每次上电时作为控制器,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,对配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程配置数据通过DATA0引脚送入FPGA,配置数据被同步在DCLK输入上,1个时钟周期传送1位或者数据。AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里。

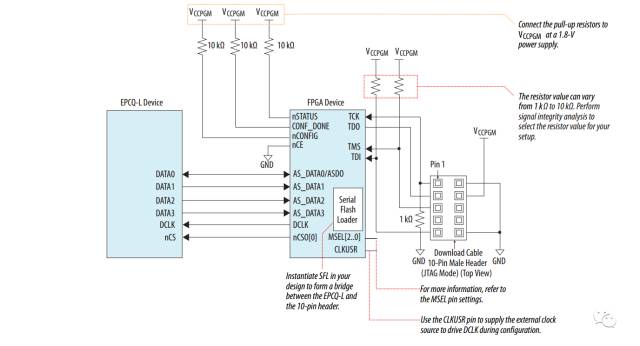

(1)AS programming interface

当编程 EPCQ-L 器件时,下载电缆通过驱动 nCE 管脚为高电平而禁用对 AS 接口的访问。nCONFIG线也被拉低以保持 Arria 10 器件处于复位阶段。编程完成后,下载电缆释放 nCE 和 nCONFIG,从而使得 下拉和 上拉电阻能够分别驱动 GND 和 VCCPGM 的管脚。使用下载电缆进行 EPCQ-L 编程期间,DATA0 将编程数据、操作指令和地址信息从下载电缆传输到 EPCQ-L。使用下载电缆进行 EPCQ-L 验证期间,DATA1 将编程数据返回到下载电缆。

(2)JTAG interface

使用 AS 编程接口时, 配置数据通过 Quartus Prime 或任何支持的第三方软件被编程到 EPCQ-L。使用 JTAG 接口时,称为 SFL IP core 的 Altera IP 必须被下载到 Arria 10 器件以形成 JTAG 接口和 EPCQ-L 之间的桥接。这样就能够使用 JTAG 接口直接编程 EPCQ-L。这种方式的烧写文件是.JIC。

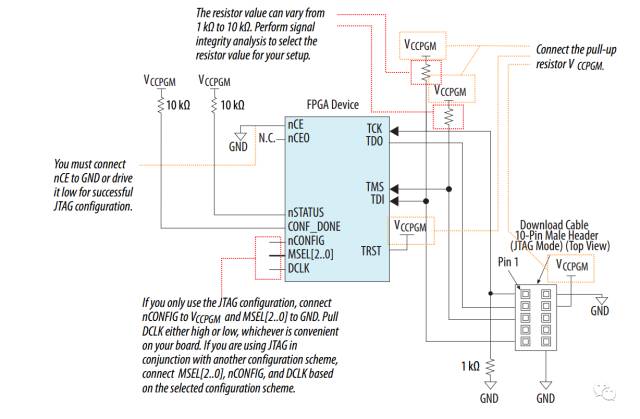

2、JTAG模式

JTAG:JTAG是直接配置到FPGA里面的,由于是SRAM,断电后要重烧;JTAG烧写的时SRAM对象文件(.sof)

JTAG配置的时间只与目标芯片的型号有关,而与具体应用无关。

JTAG Configuration of a Single Device Using a Download Cable

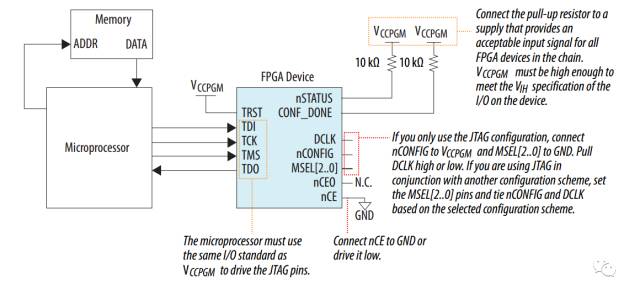

JTAG Configuration of a Single Device Using a Microprocessor

对于这种连接方式,是把数据写入到存储器中,每次上电时由控制器去配置FPGA。

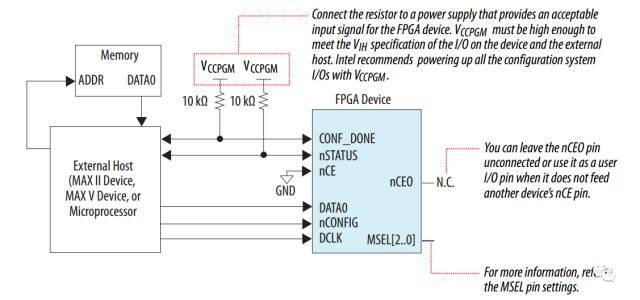

3、被动配置方式(PS)

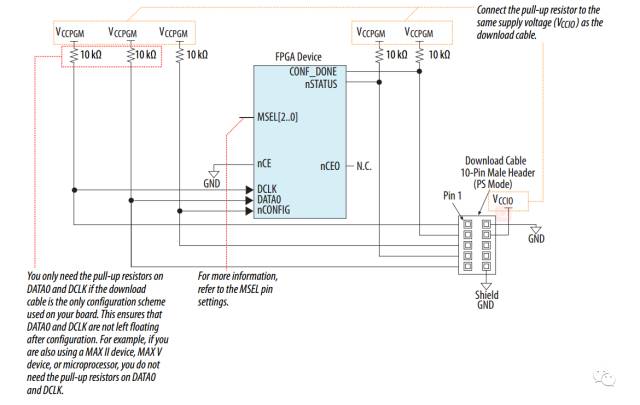

PS模式(passive serial configuration mode):由外部计算机或控制器读取外部存储器的配置数据写入到FPGA的配置过程。控制配置过程的操作是在外部处理器上实现的,对于MAX V和MAX II可以通过PFL IP来实现这个过程,对于PC主机可以通过下载线来实现该过程。被动配置模式又分为串行被动模式和并行被动模式。该模式可以实现对FPGA在线可编程。

Single Device PS Configuration Using an External Host

Single Device PS Configuration Using an Intel FPGA Download Cable

这种方式我是没有实现过的,所以了解的可能不是很正确。

原文标题:FPGA配置的三种主要方式

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

勇敢的芯伴你玩转Altera FPGA连载51:Altera FPGA配置方式概述2018-03-04 3763

-

FPGA器件有哪些配置下载方式?2021-04-15 1264

-

今日说“法”:FPGA的三种配置方式2023-04-24 846

-

SPI方式FPGA配置和SPI flash编程2011-05-16 1138

-

FPGA配置模式2011-09-08 2263

-

FPGA芯片配置方式及常见配置方法2016-10-26 13233

-

FPGA开发板使用和配置方式2017-11-22 7680

-

FPGA的配置/加载方式2018-10-05 19383

-

SF-EP1C开发板之AS和JTAG配置方式2019-03-07 4425

-

FPGA配置方式的特点与区别(1)2019-11-25 6130

-

FPGA的三种配置方式详解2020-07-09 9087

-

FPGA芯片配置分类及配置方式2021-09-06 7811

-

FPGA数据配置模式解析2022-11-21 2273

-

串行配置和并行配置模式下的多片FPGA配置数据流加载方式2023-02-20 8477

-

固化FPGA配置芯片的方式2024-10-24 2397

全部0条评论

快来发表一下你的评论吧 !