5G毫米波集成天线一体化技术的发展趋势

电子说

描述

作为5G大规模多输入/多输出( MIMO) 的技术支持,毫米波天线集成技术是实现高分辨数据流、移动分布式计算等应用场景的关键技术。讨论了封装天线( AiP) 、片上天线( AoC) 、混合集成等毫米波天线集成技术发展状况、关键技术及其解决方案,剖析了几种典型集成天线技术,分析了技术发展脉络,总结了5G毫米波集成天线一体化技术的发展趋势。

比如:针对生命体征监测和姿势识别,IMEC开发了一款带有片上天线的140GHz FMCW雷达收发器。雷达的工作范围为0.15米至10米,分辨率为11毫米,射频带宽为13GHz,中心频率为145GHz,收发器IC采用28nm模块CMOS技术制造,可实现低成本的解决方案。

引 言

毫米波半导体是第五代移动通信技术( 5G ) 的基础器件,采用毫米波频率进行定向通信的技术是5G预期配置的关键技术之一。毫米波的频率范围为30~300 GHz。目前研究的波段范围有28 GHz频段、 38 GHz频段、 60 GHz频段和E频段( 71 ~ 76 GHz、 81~86 GHz) 。5G技术将通信频段移向比第四代移动通信技术(4G) 高得多的毫米波频率。5G的频谱带宽较4G会有10倍至20倍的提升,最高数据传输速率可以提高20倍,且天线阵列和基站设备的尺寸更小、成本更低。在毫米波频段中, 28 GHz频段、 60 GHz频段是最有希望应用于5G的两个频段。

作为收发RF信号的无源器件,天线决定了通信质量、信号功率、信号带宽、连接速度等通信指标,是通信系统的核心。如何增加频谱数据吞吐量是从4G 到5G的重大挑战。5G的关键技术为大规模多输入、多输出( MIMO )的集成毫米波天线技术。每一个MIMO信道有着自身的从接收天线、发射天线到微处理器的信号通路。接收信道的作用是实现从天线接收RF 信号到输入采样基带频率的下变频, 以及模数信号转换等功能。发射信道的功能是将上变频后的数字信号转换为模拟RF信号。缩小尺寸是5G天线的一个重要挑战。最小的基站天线尺寸将缩小到信用卡大小,这会增大毫米波天线及电路在集成度、低功耗和连接方面的要求。提升功率密度是5G天线的另一个重要挑战。

多天线系统集成是应对5G系统 MIMO 、缩小尺寸、提升功率密度等挑战的重点技术之一。由于SiGe和 CMOS RF集成电路已经达到高的fT、 fmax和高的集成密度,能采用CMOS、 SOI和SiGe工艺来设计大规模全集成硅毫米波相控阵电路。基于全RF结构、 8~32元的发射( Tx ) 、接收( Rx ) 或收/发( T/ R) 模式已成功用于45~110 GHz频段。硅集成方案可以在同一芯片上集成多个元件。与GaAs和InP等 Ⅲ-Ⅴ族半导体技术相比较,硅基技术具有更高的集成度和更低的成本。硅相控阵芯片在毫米波领域中应用广泛。该项技术所面临的挑战是,在信号链单元上的RF功率放大器、低噪声接收机放大器、 A/D转换器或D/A转换器都需要很大的效率提升。

无线通信和传感器系统均可以通过RF系统提高集成度和采用新封装技术的方法来提高性能。目前实现前端电路和集成天线的方案有三种。第一种为天线封装( AiP ) 技术,天线采用IC封装工艺制作。第二种为芯片上天线( AoC) 技术,天线直接在 硅衬底上制作。第三种为AiP和AoC的混合技术,天线馈电点制作在芯片上,辐射元件在片外实现。AiP技术中,芯片和天线的互连在某个频率范围内应该达到信号传输的有效效率,其主要的封装工艺有引线键合工艺和倒装芯片工艺。但是,器件在高频时的损耗较大,成本将升高。

1、相控阵接收机的结构

硅毫米波相控阵技术在5G通信中的应用范围不断扩大。多家公司采用SiGe 和CMOS工艺来制作IC,其工作频率已达60~100GHz。例如,北美丰田研究所研制了一种具有RF波束形成能力的SiGe单芯片汽车相控阵接收机[1],如图1所示。

汽车相控阵接收机采用低成本的键合线技术进行封装,并与16元线性微带阵列连接。该天线在77~ 81 GHz频率的指向性为29. 3 dB,增益为28 dB,每步( 1°) 在方位角平面中能扫描到±50°。该芯片中,平面相控阵天线阵列间距只有0.5λ( λ=3. 75 mm,频率80 GHz 以下) ,这个参数对于可用面积很小的毫米波电路尤其重要。这种相阵列需要尽可能多地在SiGe或者CMOS芯片上集成更多电路,不仅包括移相器和VGA,而且包括全部的发射/接收电路、功率合成网络、数字与SPI控制、偏置电路,某些情况下还包括完整的上/下转换器。

图1毫米波汽车相控阵接收机

2、天线集成技术

目前, 60 GHz封装的天线和片上天线均使用商用电磁仿真软件进行设计。对于混合解决方案,已开发出补充标准IC设计工具的建模方法,以实现引线键合与 IC 的协调集成。AiP技术需要确保整体性能的IC与天线间的宽带低损耗互连设计。AoC技术需要先进的后处理步骤或封装工艺,以减少严重的介电损耗。混合天线集成技术则融合了AiP和AoC的优势,可实现高辐射效率,无需芯片与封装的低损耗互连设计。但是,该方案的设计灵活性不高,且在宽侧方向上呈现辐射零点,阻止了其在某些场合的应用。

2. 1 AiP技术

2. 1. 1结构

AiP技术是将一元或多元天线集成到RF封装内的关键技术,其典型方案是采用集成电路封装工艺。在硅毫米波收发器中,封装内集成了天线阵列,有助于提供足够的信号增益,实现尺寸最小化。这种工艺是毫米波RF集成方案规模应用的关键技 术。例如,30 GHz天线元的尺寸为毫米量级,在单个封装内需要采用新类型的天线阵列集成技术。具有光束转向功能的微小相控阵天线是毫米波无线电的关键器件[2]。为了在收发器封装内集成天线阵列,需要考虑芯片组装方案、阵列元和馈电网络、芯片与封装互连、封装材料等。如果收发器采用多层封装,需要在芯片与天线之间采用先进的互连技术,满足天线馈电插入损耗最小的要求。芯片可以放置 在封装正面,也可以放置在封装底部。

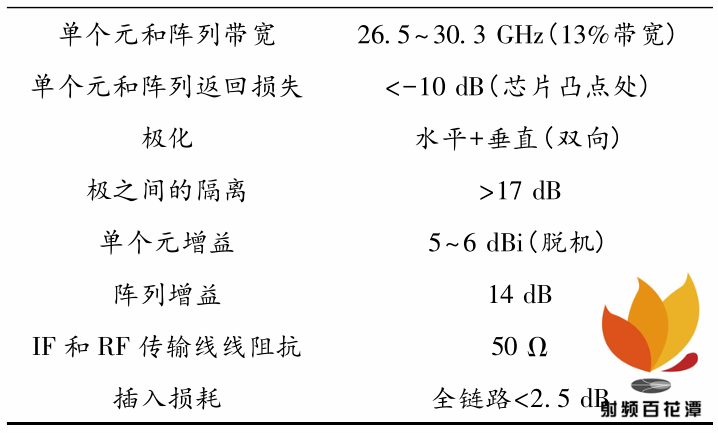

将芯片放置在封装底部的方案对芯片接收和发射的影响最小。一种可用于5G无线通信的有机芯片封装中的相控阵毫米波天线如 图2所示。为了提高天线带宽、增益和辐射效率,在一个厚的覆板上放置了一个寄生平面结构,构成一个双贴片天线叠层。为了达到优化RF设计和制造的目标,对封装层叠片和低介电常数材料的参数作了优化选择,如表1所示。

图2有机芯片封装中的相控阵毫米波天线

表1天线阵列设计要求

2. 1. 2设计与制造

在AiP设计中,除了波束形成、信号放大和具有频率转换功能的相控阵IC外,具有极化特性的天线也是天线阵列的关键器件。在最早的硅基毫米波IC设计发展阶段,天线设计采用衬底、形状和成本与硅基毫米波IC兼容的技术[3]。目前,已有多种频率的硅衬底片上毫米波天线,但由于面积较大、发射效率有限,在100 GHz以上的天线才有研究价值。在60 GHz频率内,在液晶聚合物( LCP) 、有机高密度互连衬底、玻璃衬底、高/低温共烧陶瓷衬底、硅衬底和模制物料基晶圆级衬底等材料上制作的硅相控阵天线阵列已被报道。通常需要对AiP阵列的增益、带宽和辐射图形进行优化。同时,需要考虑衬底材料、阵列尺寸(即元件和贴片的数量) 、互连灵活性(如连接电源和控制信号) 、热性能与机械性能的相容性、 IC组装和板集成等因素。

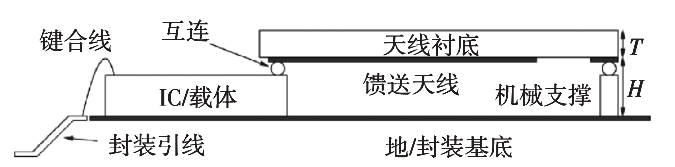

一种新的天线与 IC/载体结构如图3所示[4]。天线结构通过PCB板制作于厚度为T的介质衬底上,并悬空倒置,翻转在IC/载体之上。IC封装基的地也作为天线的镜像地,天线与地的间距为H。该结构中,天线与地板之间具有非常低的介电常数,天线结构之上有一层具有较高介电常数的覆板材料。在保持高天线效率的前提下,相比于标准PCB天线结构,这种堆叠结构具有更高的带宽。一个带有焊球的垫片可以放置在天线覆板的另一端,作为支撑。

图3天线与IC/载体结构

AiP设计中通常采用集成电路封装工艺进行封装,需要将天线与片上电路进行物理连接。低温共烧陶瓷( LTCC) 工艺可实现任意数量层的安装结构, 具有跨层过孔、层间形成开放腔或密闭腔(IC 可集成于此) 等灵活性。采用该工艺封装的毫米波天线越来越受到关注[5]。有些方案采用传统的键合线、 倒装芯片和C4焊接等工艺。例如, 60 GHz硅相控阵芯片封装需要有芯片与天线间低损耗分布网络的多层毫米波衬底,必须是多层低损耗的Teflon基或 LTCC 基,成本昂贵。因此,典型的硅相控阵AiP可以达到30 ~ 60 GHz频率[6],达到80 GHz的难度更大。

较之LTCC封装方案,印刷电路板( PCB) 封装方案可以降低成本。有采用PCB等较低成本高频电路材料制成多层安装结构的封装方案,如RO3000系列和RO4000系列[7-8]的封装。还有采用液晶聚合物作为基板的低成本方案。但由于使用盲孔或埋孔,层的数量增多,会导致PCB技术的机械制造成本升高。另外, PCB工艺在极高频段实现高密度化的难度增加,这将严重影响系统性能,导致效率降低。因此, LTCC工艺是大多数多层结构阵列的选择,采用该工艺方案的天线性能有改善。

2. 2 AoC技术

2. 2. 1片上天线

片上天线是采用片上金属化连线工艺集成制作的天线。在芯片上直接集成和组合天线的制作方法是太赫兹通信器件研究最少的领域之一。在当前技术条件下,由于衬底吸收和传导电流等原因,消除RF电路与天线间所有的连接会使得设计成本大幅 降低,设计更加灵活。传统观念认为,由于没有介电镜( Dielectric Lenses) 补偿结构,片上天线对于消费类的小功率器件并不是最佳结构。虽然典型片上天线的效率只能达到10%,但如果能在片上设计并制造出亚毫米天线( 采用选频性质的表面[9]或者Yagi高方向性的天线[10]) ,则会带来成本大幅降低和设计灵活性大幅增加的优势,这会超过使用效率更高、但昂贵且复杂的片下天线的优势,从而增加了应用的可能性。

随着载波频率和带宽移向亚太赫兹,高宽带和高载波频率使得金属引线变得不稳定,片上天线被认为是替代印刷板上芯片金属互连的方法之一。除了片上天线,片上波导和硅穿孔( TSV) 波导也是亚太赫兹频段大带宽应用中替代金属连线的有前景的技术。片上天线的成功实现将会使得高集成度收发器、60 GHz 空间电源组合和更高频率毫米波系统等众多应用受益。频率从0. 9GHz[11]到77 GHz[12的多种频率片上天线已有不少报道。德国高性能微电子研究所( IHP) 采用标准SiGe BiCMOS工艺,设计并制作了一种130 GHz的片上天线,峰值增益达到8. 4 dBi。

2. 2. 2 CMOS片上天线

CMOS工艺是 RF IC 的一条重要发展途径。随着CMOS管特征频率( fT) 接近400 GHz[14], CMOS工艺在毫米波 IC 中得到进一步应用。文献[ 15]提 出了一种在CMOS芯片上集成人工磁导体和宽带窄槽天线的新方法,采用标准CMOS工艺实现了60 GHz下2 dBi的增益和大于126%的阻抗带宽。文献[ 16]采用0. 18 μm CMOS工艺,制作了一种60 GHz的圆极化环形天线,具有覆盖57~67 GHz的模拟和测量的轴向比( axial ratio, AR<3) 带宽,增益达4. 4dBi。文献[ 17]采用能制作阻抗带宽为25 GHz ( 45~70 GHz) 的器件的Si CMOS工艺,制作了一种60 GHz宽带的单极子天线,在60 GHz下实现了- 4. 96 dB的增益。文献[18]提出了一种高增益( 8 dBi 最大增益) 和高效率( 96. 7%峰值天线效率) 的片上天线,采用CMOS 0. 18 μm工艺制作,天线的- 10 dB带宽为4 GHz。文献[19]采用0. 18 μm CMOS工艺,制作了一种60 GHz带宽的CPW馈电环形单极子天线。

通常,制作在掺杂硅衬底上的片上天线只有约10%的低效率。但若采用成本较高的封装天线,可实现比片上天线更高的效率。可采用容性耦合等先进连接技术,将成熟、低成本、较少掺杂的衬底上制作的天线芯片与有源60 GHz毫米波RF芯片连接起来,以实现比采用标准键合工艺的器件高得多的工作频率范围。天线可以用低成本的工艺( 如0. 18或0. 35 μm) 和较低掺杂的衬底来制作,再通过容性耦合,连接到含60 GHz 功率放大器等有源元件上,而不采用更先进工艺[20]。一种通过容性耦合将天线芯片与有源60 GHz RF芯片连接的毫米波集成天线如图4所示。该天线不仅具有旧工艺的低掺杂浓度、高电阻率所致的低电导性、低损失衬底,而且具有更高效率。制作天线阵列时,低速有源开关( 如二极管) 可以集成到芯片上,采用分相位无源馈线来执行元件调谐、移相和波速控制。

图4通过容性耦合将天线芯片与有源60 GHz RF芯片 连接的毫米波集成天线

2. 3混合集成毫米波天线

混合集成毫米波天线就是采用专用工艺,将天线与前端 IC 集成在同一封装中。这种制作技术是纯AiP和AoC的替代技术。混合集成天线的示意图如图5所示[21]。熔融石英衬底上的偶极天线的 一半安装在片上,另一半安装在片下。这种结构的天线可以直接连接到片上电子器件。在60 GHz全频段内,当增益为6~8 dBi时,芯片最大辐射效率可达90%。

图5混合集成天线概念示意图

3、毫米波天线集成技术进展

3. 1学术界发展情况

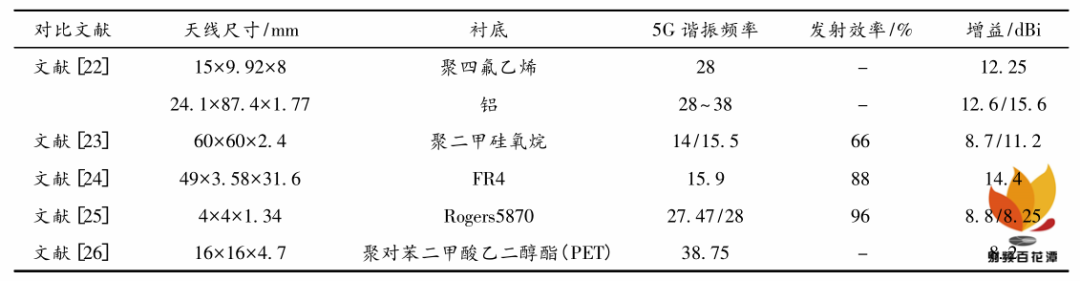

物联网( IoT) 和5G要实现全面互联的目标,就需要开发不同毫米波频段的天线,并实现商业化量产。表2总结了用于广域IoT和5G无线通信的近期文献中毫米波天线及其性能比较。可以看出,实用的解决方案仍然较少,多数方案仍然需要解决结构复杂、增益减少、效率低和功耗高等问题。

60 GHz毫米波段器件将应用5G并量产化。片上系统或片上前端小型化系统集成的发展趋势要求在不牺牲辐射效率、带宽、增益的前提下,AoC器件、AiP器件的成本、尺寸和功耗必须向更小化方向发展。使用硅IC工艺提供了最大的集成度、低成本和低功耗,表明GaAs等Ⅲ-Ⅴ族化合物工艺并不一定是最佳选择,尤其是考虑封装、集成和互连问题时。

表2近期文献中5G毫米波天线及其性能比较

天线元件通常制作于片下,也可以被完整地集成在单个芯片上。硅衬底由于介电常数高、电阻率低,片上集成天线的增益很小、辐射效率很低,可以通过提高衬底的电阻率来改善性能。例如制作高性能低成本的SoC时,将天线和IC集成到高电阻率绝缘层上硅( HR SOI) 上。在AiP方案中,为解决毫米波频率下硅衬底上天线阵列的平面馈电器件插入损耗过大的问题,可采用将天线集成在附加基板上的混合集成创新技术,充分利用封装和在这种有限空间内的耦合可能性。该方案显现出较高的设计灵活性。

IBM公司在过去的14年中发展了RFIC和AiP系列: 成像和通信应用的具有波束形成和波束扫描能力的性能驱动相控阵( 如60 GHz、 94 GHz和28 GHz相控阵) ,支持便携装置的V-波段、W波段和Ka波段毫米波模块( 如60 GHz单元件、开关波束模块)[27]。

文献[ 28]提出一种多层LTCC基板上构建的线性极化6 GHz天线阵列。这些阵列使用4×4微带贴片辐射元件,分别由四分之一波长匹配的T型接头网络和Wilkinson功率分配器网络馈电。测量结果表明,由前者馈电的阵列比由后者馈电的阵列表现更好。对于带有和不带有嵌入式腔的阵列,测量的阻抗带宽分别为9. 5%和5. 8%,最大增益分别为18. 2 dBi和15. 7 dBi。

文献[ 29]报道了一种在熔融石英基板上构建的线性极化60 GHz天线阵列。该阵列使用由馈电网络馈电的2×4微带贴片辐射元件,馈电网络使用了共面条带和共面条波导。通过金属腔增强的阵列实现了大于9 GHz的测量阻抗带宽和约15 dBi的最大增益。

文献[ 30]提出一种采用LTCC工艺、具有2×2微带贴片辐射元件的天线阵列,制作出具有线性极化的60 GHz发射器模块。

文献[ 31]分别使用1×8和2×5微带贴片辐射元件,制作出两个有源线性极化60 GHz天线阵列。

文献[ 32]提出了一种具有由波后波导网络馈电的槽辐射元件、线性极化60 GHz的天线阵列。

文献[ 33]提出了一种圆极化60 GHz的天线阵列,该阵列通过对原始天线元件、叠层波导、调整圆极化轴比进行精细设计,实现了宽带宽。

文献[ 34]提出了一种在 LCP 基板上制作的圆极化 60 GHz 天线阵列。该阵列采用了新的槽辐射元件和新颖的开腔反射器。测量结果表明, 2×4辐射元件阵列的峰值增益为15. 6 dBic。

3. 2 商业化发展态势

据Gartner 预测,到2021年,市场将有9%的智能手机支持5G网络。5G采用波束成形技术,必须采用多天线阵列系统( Massive MIMO) 。这将导致天线呈量级增长,并推动天线向高度集成化、复杂化的方向发展,工艺技术不断升级,新材料不断应用。例如,新型材料液晶高分子聚合物( LCP) 材料具有低损耗、高灵活性、高密封性等优点,非常适用于制作微波、毫米波器件。苹果公司推出的毫米波天线解决方案中包含采用LCP材料制作的天线,这是5G天线大规模商用化的一个重要方向[35]。

高通公司QTM052毫米波天线模组系列支持紧凑封装尺寸,适合于移动终端集成。配置QTM052的毫米波天线模组的终端将于2019年上半年推向市场,显示出在5G中集成天线和RF前端等元器件的发展趋势。意法半导体公司、 STATS ChipPAC和英飞凌科技公司在英飞凌第一代嵌入式晶圆级球栅阵列 ( eWLB) 技术的基础上,合作开发了下一代的eWLB半导体产品封装技术。目前已开发出具有8 mm×8 mm封装的集成天线制作的四通道收发器。该天线采用RDL层中的金属结构,并集成于封装中,为在5G等毫米波领域应用的雷达系统封装提供了解决方案[36]。近期,中芯长电公司发布了SmartAiPTM工艺平台制作的世界首个超宽频双极化的5G毫米波天线芯片的晶圆级集成封装,具有集成度高、散热性好、工艺简练的特点,能够实现24~43 GHz的超宽频信号收发,达到 12. 5 dB的超高天线增益。

4、结束语

在未来的较长时间里, 5G架构将继续在网络、 无线访问和物理层不断发展,需要在RF/ 毫米波集成电路、毫米波天线阵列技术等方面拥有多种创新型产品组合,从而推动5G无线电和产业化发展。例如, 5G中功率放大器、天线、滤波器和匹配电路的数量可以高达64个或更多。这些组件在效率和集成度方面的提升对无线电的总体能效和性能十分重要。具有大量天线、频率为27 GHz及以上的高集成度MIMO无线电是5G系统的关键技术。上述三种集成方案可用于毫米波天线设计。以60 GHz频段为例, AoC器件的辐射效率和增益指标落后于AiP器件和混合方案。AiP器件和混合器件实现了最佳辐射效率,因此可以认为选用AiP技术比选用AoC技术更合适。

AiP技术具有设计灵活性和印刷天线结构的优势,但对于复杂的多层封装结构,可能不具备与AoC技术和混合方案同等成本竞争的条件。此外, AiP方案芯片到芯片的互连会导致热损失、延迟和设计量增加。混合方案似乎是最好的方案。但是,当频率超过60 GHz时,典型的混合技术、 AiP都是不够成熟的方案。而AoC方案会更加完善,且已在THz波段进行了测试。据预期,AoC方案在高频具有更大发展空间。

天线集成的一个根本解决方案是将一个相控阵所需的所有东西集成到一个芯片上,这是硅基毫米波天线系统的优势所在。不仅集成电子器件,而且集成通向晶圆级实现的高效率天线。晶圆级相控阵就可放置在输入/输出数据信号高达Gbit/s、布置有控制器件和电源器件的低成本印刷电路板上。整个毫米波功能均集成于同一芯片上,这种晶圆规模的实现是一个完全自包含的解决方案。(参考文献略)

原文标题:毫米波天线集成技术研究进展

文章出处:【微信公众号:电磁兼容之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

5G毫米波频段的特点、应用场景、技术挑战和发展趋势2023-12-27 4910

-

哪些毫米波频率会被5G采用呢?2023-05-05 1356

-

5G毫米波天线设计及集成天线一体化技术的发展趋势2022-11-09 4841

-

5G毫米波集成天线一体化技术的发展趋势2022-07-12 5403

-

什么是5G毫米波和OTA测试?2021-11-19 5328

-

5G干货|全面认识毫米波频谱与技术2020-03-12 3006

-

紫光展锐完成基于AiP的5G毫米波测试,可支持多个毫米波频段2020-03-03 4065

-

光载毫米波无线电通信技术的发展趋势2019-06-19 2166

-

5G毫米波天线的最优技术选择2019-06-12 1993

-

5G原型演示系统,毫米波MIMO技术要哪些特性?2019-02-15 4341

-

探一探毫米波雷达技术的发展趋势2018-08-03 7669

-

5G时代的挑战,毫米波解决方案的测试和验证设计2018-07-23 3744

-

浅析机电一体化的发展趋势2012-10-21 3563

-

谈谈机电一体化技术的现状及发展趋势2012-10-16 5284

全部0条评论

快来发表一下你的评论吧 !