深入学习基于FPGA的数码管动态扫描驱动设计

电子说

描述

基于 FPGA 的数码管动态扫描驱动设计

1. 实验引言

在电子系统中,通常都需要有输出设备来输出或显示一定的信息,以指示当前系统运行的状态。在以单片机和 ARM 为主的电子系统中,液晶屏是理想的输出设备。而 FPGA 则因为其独特的硬件结构,如果用 RTL 级电路来驱动彩色液晶屏来显示一定的数据,势必是非常不划算的选择,而且驱动也极为复杂。数码管作为一种能够直观显示一定数据信息的输出设备,具有驱动简单、显示直观的特点,尤其适合作为 FPGA 系统的输出设备。本节,我们就将和大家一起进行数码管驱动的开发。

2. 实验目的

实现 6 位 7 段数码管的驱动,待显示数据以 BCD 格式输入。数码管刷新时钟为 1KHz。实验使用了 4 个独立按键作为输入,通过按键来改变需要数码管显示的数据,以验证数码管驱动的正确性,同时也可检验独立按键消抖模块的可靠性。

3. 实验内容

本实验的内容是数码管动态扫描驱动的设计,通过外部四位按键的不同操作来驱动数码管显示不同的值。

4. 实验原理

数码管所谓的动态扫描,就是利用人眼的视觉暂留特性,在人眼能分辨的变化速度以外,快速分时的点亮各个数码管及其对应的段。因为分别点亮所有数码管一次所用时间小于人眼的视觉暂留,因此,在人们眼里看来,这些数码管都是同时持续点亮的,并不会有闪烁的感觉。

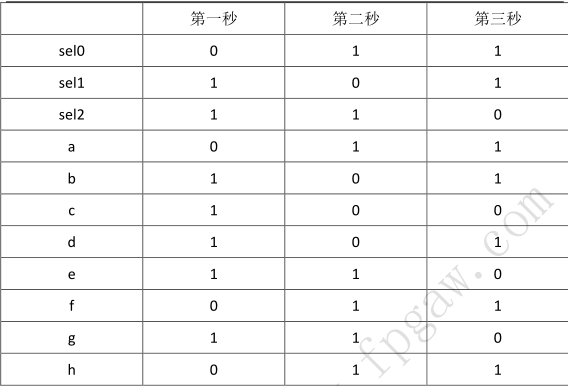

图 1 为 3 位 7 段数码管的等效电路图,在这个图中,可以明显的看到 24个发光二极管被分为了三组,每一组的 8 个发光二极管正极被接在了一起,通过一个三极管与 VCC 相连。三极管的基极连接到了 FPGA 的 IO 上,因此,只需要 FPGA 对应的 IO 上给出低电平,三极管便会导通。而三组 LED 中所有的相同编号的 LED 的负极被连接在了一起,并接到了 FPGA 的 IO 上。如果我们希望将最左边一组的 led0、led5、led7 三个编号的 led 灯点亮,其它 led 不亮,则只需要给 Q0 的基极(sel0)连接上低电平,并将 led0、led5、led7 的负极(a、f、h)连接上低电平,其它所有端口都输出高电平,则最左边一组的对应的三个 led 灯就会被点亮,而其它 led 则会处于熄灭状态。 假如我们需要在三秒时间内,完成以下三次操作:第一次操作,点亮最左边一组 led 灯的 led0、led5、led7;第二次操作,点亮中间一组 led 灯的 led1、led2、led3;第三次操作,点亮最右边一组 led 灯的 led2、led4、led6;那么我们只需要按照如下表格中列出的真值表操作即可:

按照以上表格,我们就能知道该如何操作了,只需要在不同的时间给各个 IO 不同的电平,便能实现我们想要的亮灭组合。以上我们是以 1 秒为单位进行 led 组的切换的,假如我们将切换速度加快,变为 1 毫秒一切换,会是什么情况呢?在 1 毫秒一切换的速度下,完成所有操作所需时间为 3ms,远远超出了我们人眼所能辨识的变化速度范围。如果我们让以上三个操作永远循环的进行下去,那么我们将看见三组 led 灯中,我们点亮的那几个 led 是同时且一直处于亮着的状态的,这便是动态扫描的原理,假如我们把每个 led做成一个长条型的,并按照如下形状摆放,便就是我们常见的数码管了。

5. 硬件设计

在这个图中,共有 6 位数码管,每个数码管的正极被接在一个驱动三极管上,三极管的基极连接到三八译码器的 Y 端,则 FPGA 只需要三个引脚就可最多控制 8 个数码管的位选。数码管的段选在串接了 470 欧姆的电阻后与FPGA 的 IO 相连。这里 470 欧姆的电阻主要起到限流的作用,保证流过数码管的电流在正常范围内。

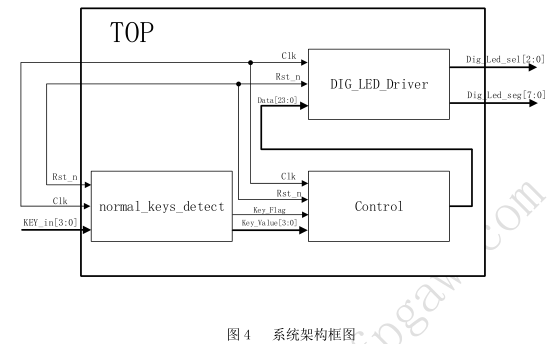

6. 系统结构框图

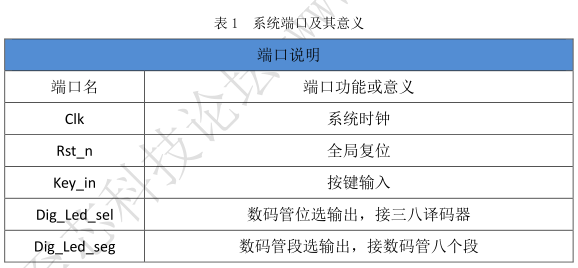

系统端口及其意义如下:

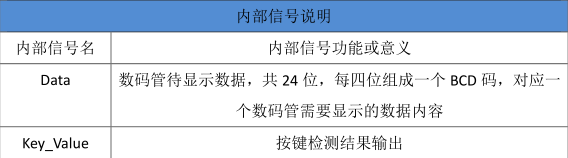

内部信号及其意义如下:

7. 代码解释

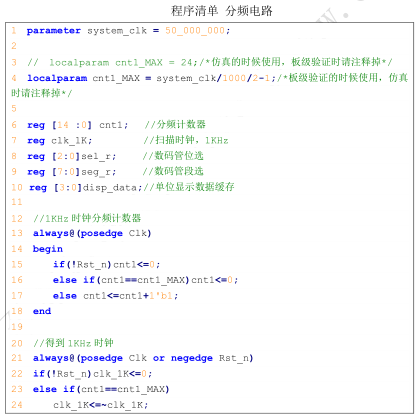

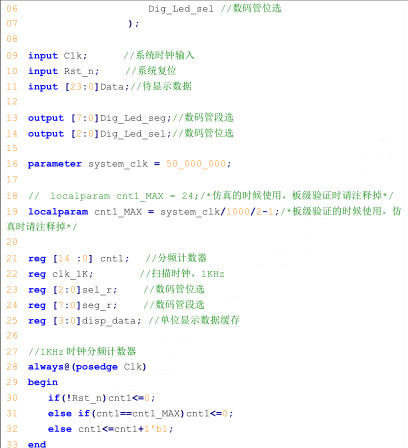

因为数码管属于低速设备,其正常的扫描频率为 500~10KHz,扫描频率太快,会导致系统功耗增加,显示效果变暗。扫描频率太慢,会有明显的闪烁感。本实验通过调试观察,选择以 1KHz 作为扫描频率,实际显示效果非常好。 因此本实验首先就需要产生一个 1KHz 的扫描时钟,该时钟由系统时钟分频得到。产生 1KHz 扫描时钟的代码如下:

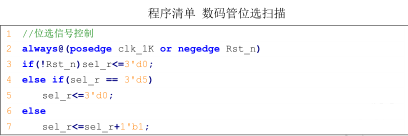

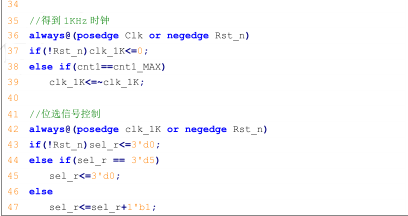

其中,定义了一个全局参数 system_clk,该参数为 Clk 的频率,不同的时钟频率,只需要更改该参数,就可改变分频计数器的最大计数值,以保证 1KHz分频的精准性。 在驱动中,数码管的位选以扫描时钟的速率进行切换,因为只有 6 位数码管,因此当位选计数到 6-1 后必须清零从头开始计数。相关代码如下:

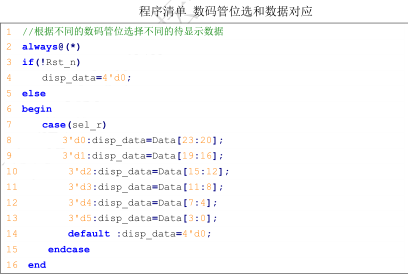

每个数码管需要显示的内容都不相同,由 Data 中相应的位指定,Data中各位与数码管的位对应关系如下:

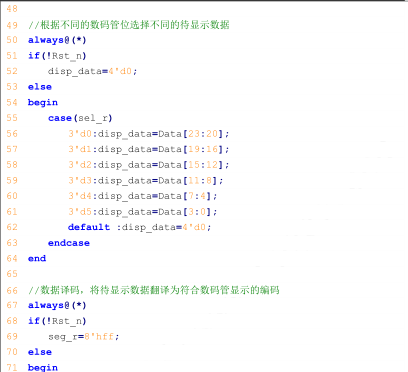

因此需要从 Data 中将每个数码管被选中时需要显示的数据提取出来,提取数据的代码如下所示:

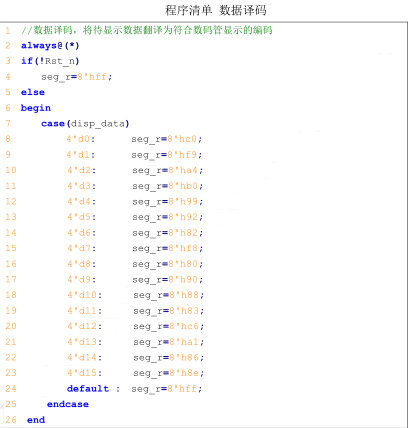

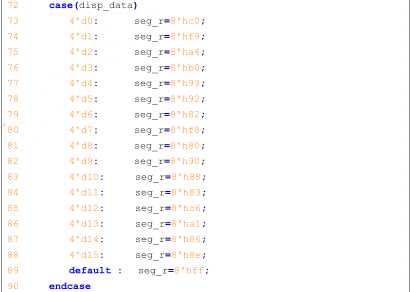

因为提取出来的数据还是 BCD 码的形式,还需要将 BCD 码对应的数据翻译成为数码管显示对应字符时应该点亮或熄灭的对应的 LED 的控制信号,因此必须还有一个 BCD 码译码的过程,该过程代码如下所示:

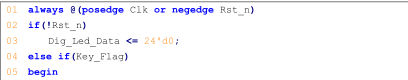

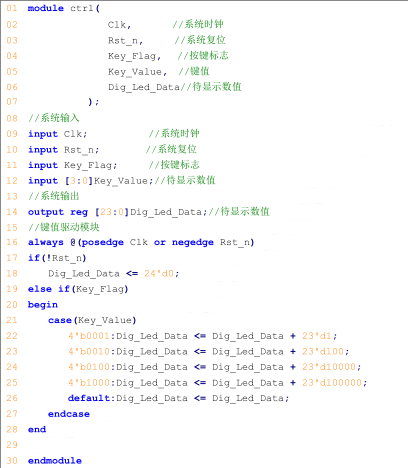

控制部分相对简单,只需要根据对应的 按键信息,给待显示的数据加上一个对应的值,该部分代码如下所示:

8. 程序清单

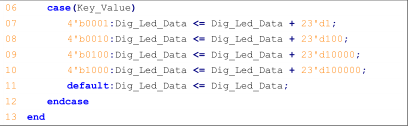

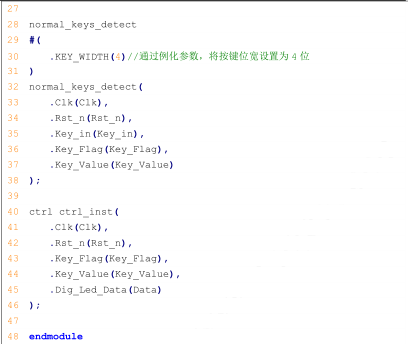

(1)工程顶层模块(文件名 top.v) 该模块为工程顶层模块,负责将按键检测模块(normal_keys_detect.v)、显示控制模块(ctrl.v)、数码管驱动模块(DIG_LED_DRIVE.v)按照逻辑关系级联。

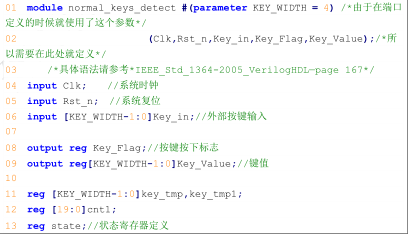

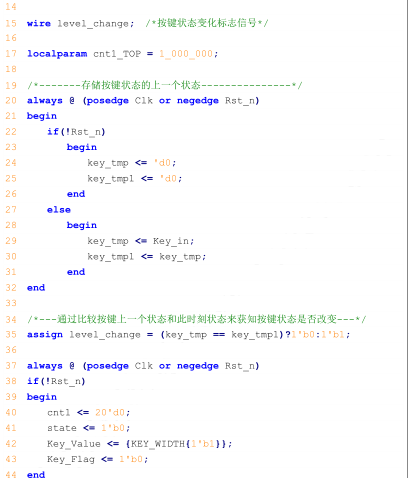

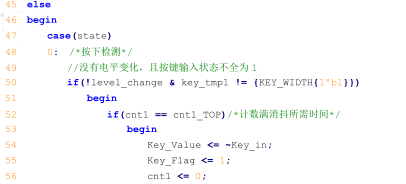

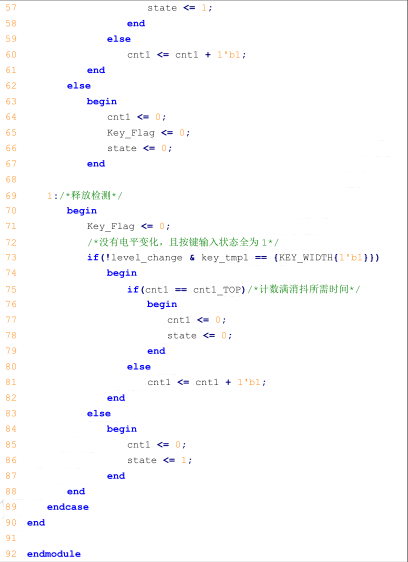

(2) 按键检测模块(文件名 normal_keys_detect.v) 该模块为按键检测模块,负责检测外部按键值,并完成按键消抖,输出按键检测标志。

(3) 控制模块(文件名 ctrl.v) 该模块为数码管显示控制模块,通过检测到的键值驱动数码管显示出不同的值。

(4) 数码管显示驱动模块(文件名 DIG_LED_DRIVE.v) 该模块为数码管显示驱动模块,负责将输入的数据正确显示到数码管对应位。

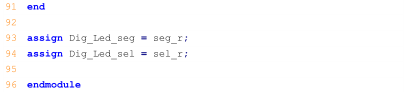

(5) 测试仿真模块(文件名 DIG_LED_DRIVE_tb.v) 该模块为数码管显示驱动测试模块,用于仿真查看数码管驱动逻辑是否正确。

责任编辑:lq6

-

FPGA数码管动态扫描2019-08-07 1676

-

数码管动态扫描显示驱动实现的资料概述和程序免费下载2019-07-09 1502

-

FPGA数码管动态扫描详解2019-04-29 5508

-

小梅哥和你一起深入学习FPGA之数码管动态扫描(下)2018-10-01 595

-

FPGA数码管动态扫描附件详细讲解2018-09-29 3276

-

fpga数码管动态扫描程序分享2018-07-03 2436

-

HL开发板的数码管动态扫描学习程序2017-09-01 863

-

【小梅哥FPGA进阶教程】第四章 数码管动态扫描驱动设计与验证2017-01-12 4777

-

数码管动态扫描2016-03-21 476

-

LESSON4_数码管动态扫描显示2016-02-18 579

-

小梅哥和你一起深入学习FPGA汇总帖(2月2日更新)2015-01-13 34172

-

小梅哥和你一起深入学习FPGA之数码管动态扫描2014-12-30 14067

-

数码管动态扫描原理2008-05-22 2805

全部0条评论

快来发表一下你的评论吧 !