你眼中简单的IIC,其实并不简单

电子说

描述

01我们习以为常的IIC通常是什么样子?

在我们研发/应用工程师眼中,IIC的形象通常是如图这样的吧?(你们说是不是?)

是的,对于理想的硬件调程序,这个层面已经基本够用。(我是已经get到了)

02IIC还可以是这样的

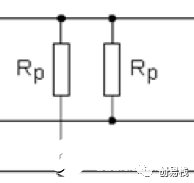

简单实用的IIC电平匹配电路,原理很简单、也很巧妙。

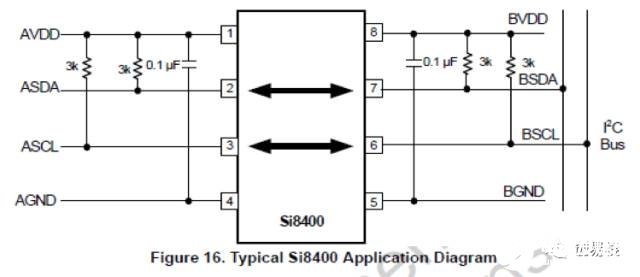

Si8400芯片,做UART或者IIC隔离是很不错的。做隔离也有实际意义的:

比如涉及强电的板子,需要隔离后的UART口打印调试信息,方便debug;电容式触摸按键调试中,某些产品采用隔离的IIC接口(如Azoteq,Cypress等芯片大部分采用IIC)调试能得到更准确的数据(原理上涉及到人体大地等构成的寄生电容,挺有意思,可以看创易栈的触摸按键相关内容)。

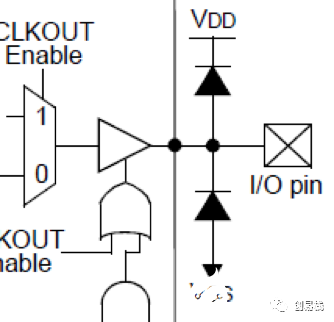

有朋友会问,我见过5V芯片和3V芯片,直接把IIC接在一起的,不需要做电压匹配呀?

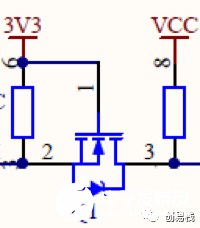

这个不建议用。需要仔细看数据手册的:一般来说3V芯片的I/O都有如图的保护结构,导致SCL、SDA信号高电平被限制在3V+0.3V,5V芯片经常不能正确识别的。

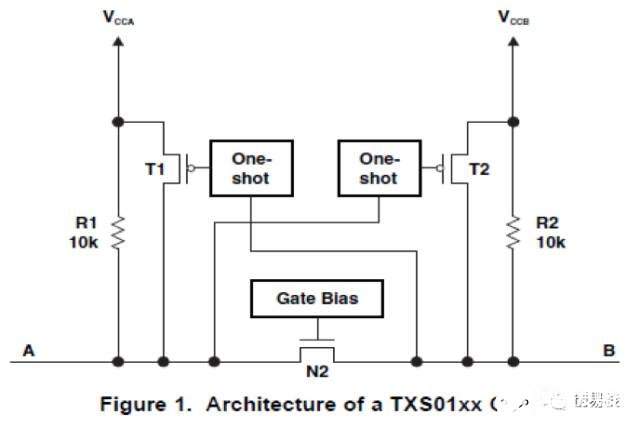

03支持双电压的高速IIC接口

TI的TXS0102带OE功能的高速IIC接口芯片。

这个有什么好处呢?

当然有,除了支持电平匹配;从它的MOS结构也可以看出,对SCL和SDA的上升边缘有个加速过程,速度可以支持到2Mbps喔。

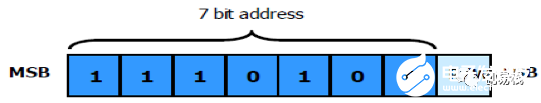

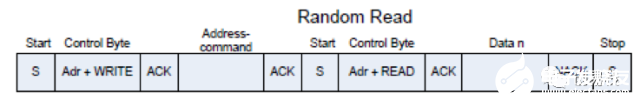

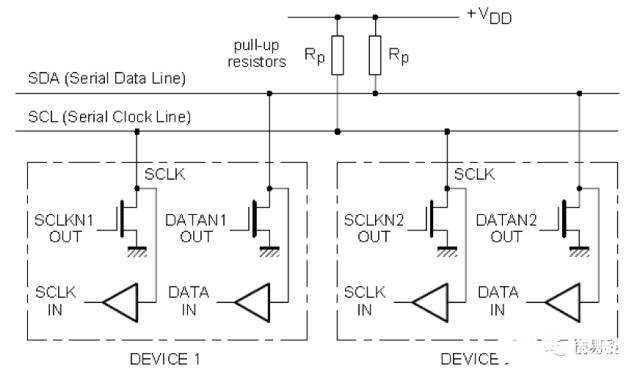

04触碰IIC的核心

每一个IIC总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管、输入缓冲为一只高输入阻抗的同相器[1]。这种电路具有两个特点:

①由于SDA、SCL为漏极开路结构,借助于外部的上拉电阻实现了信号的“线与”逻辑;

②引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致。为 “时钟拉伸”和“总线仲裁”提供硬件基础。

I2C总线接口内部结构

IIC设备对总线的操作仅有“把线路拉到地”——输出逻辑0。基于IIC总线的设计,线路上不可能出现电平冲突现象。如果一设备发送逻辑0,其他发送逻辑1,那么线路看到的只有逻辑0。也就是说,如果出现电平冲突,发送逻辑0的始终是“赢家”。总线的物理接法允许主设备往总线写数据的同事读取数据。这样两主设备争总线的时候“赢家”并不知道竞争的发生,只有“输家”发现了冲突——当写一个逻辑1,却读到了0——而退出竞争。

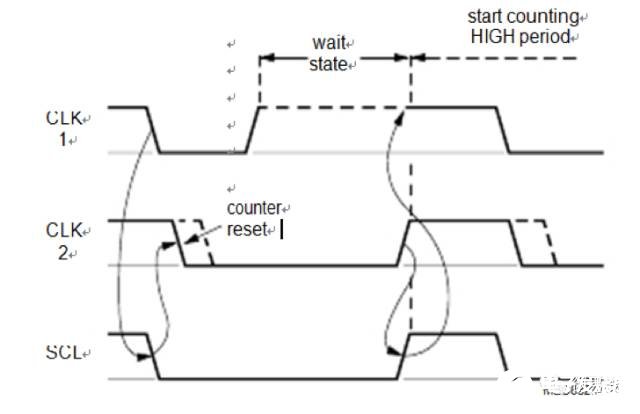

时钟拉伸(Clock stretching)

如果被控器希望主控器降低传送速度可以通过将SCL主动拉低延长其低电平时间的方法来通知主控器,当主控器在准备下一次传送发现SCL的电平被拉低时就进行等待,直至被控器完成操作并释放SCL线的控制控制权。这样以来,主控器实际上受到被控器的时钟同步控制。可见SCL线上的低电平是由时钟低电平最长的器件决定;高电平的时间由高电平时间最短的器件决定。这就是时钟拉伸,它解决了I2C总线的速度同步。

总线仲裁

假设主控器1要发送的数据DATA1为“101 ……”;主控器2要发送的数据DATA2为“1001 ……”总线被启动后两个主控器在每发送一个数据位时都要对自己的输出电平进行检测,只要检测的电平与自己发出的电平一致,他们就会继续占用总线。在这种情况下总线还是得不到仲裁。当主控器1发送第3位数据“1”时(主控器2发送“0” ),由于“线与”的结果SDA上的电平为“0”,这样当主控器1检测自己的输出电平时,就会测到一个与自身不相符的“0”电平。这时主控器1只好放弃对总线的控制权;因此主控器2就成为总线的唯一主宰者。

总结

① 对于整个仲裁过程主控器1和主控器2都不会丢失数据;

② 各个主控器没有对总线实施控制的优先级别;

③总线控制随即而定,他们遵循“低电平优先”的原则,即谁先发送低电平谁就会掌握对总线的控制权。

根据上面的描述,“时钟拉伸”与“总线仲裁”可以总结如下规律:

①主控器通过检测SCL上的电平来调节与从器件的速度同步问题——时钟拉伸;

②主控器通过检测SDA上自身发送的电平来判断是否发生总线“冲突”——总线仲裁。因此,I2C总线的“时钟同步”与“总线仲裁”是靠器件自身接口的特殊结构得以实现的。

编辑:lyn

-

【labview我来告诉你】labview编程可以很简单2011-11-11 354890

-

其实并不简单——智能手机流畅的秘密2014-05-12 1093

-

五个超实用的Windows隐藏技能 学会两个就不简单2017-05-22 1009

-

《别怕!WEBENCH其实很简单》,EEWORLD独家原创2017-09-08 854

-

这10个Excel小秘技你知道吗简单教学2018-12-23 4452

-

51单片机IIC总线通信原理及其简单应用资料免费下载2019-06-20 1328

-

FPGA其实很简单?看完这篇文章你就明白了2023-02-02 5063

-

简约而不简单的真空断路器,它有哪些应用优势2021-01-11 755

-

华为鸿蒙发布会:简单的控制,不简单的体验2021-06-02 3480

-

IIC 简单介绍2021-11-30 1350

-

那个简单的电流检测电阻一点也不简单2022-07-24 2831

-

【社区之星】保研,其实很简单——贺文杰2022-10-13 2507

-

ACTBOX恒温恒湿试验箱:选择温度湿度其实很简单2023-11-14 1076

-

连接器端子压接:看似简单,其实其中有门道……2023-12-06 2189

-

压榨辊轴颈磨损修复其实很简单2024-03-13 455

全部0条评论

快来发表一下你的评论吧 !