基于EP3C55F484C8和解码器实现高清视频数据压缩系统的应用方案

描述

作者:刘春风,王惠平,潘利明

随着社会信息量的增大,人们对多媒体视频压缩的要求越来越高,“高压缩、低比特速率”的高清视频压缩已广泛应用于家用电器、医疗设备、军事侦察、卫星遥感等领域。ADI公司最新推出的ADV212是一款具有实时压缩/解压缩标准(SD)视频信号和高清晰度(HDTV)视频信号功能的器件,具有可靠性好、配置灵活、支持视频格式多样等优点,适用于多种视频格式的数据处理。本文介绍了基于ADV212高清视频压缩系统的设计方案,该系统可支持SMPTE274M(1080i)视频实时编码。

1 ADV212的编解码原理

图l所示为ADV212的功能图,主要由像素接口、小波变换引擎、熵编/解码器、嵌入式RISC处理器、存储器系统和内外部DMA等组成。操作的基本流程是视频或像素数据通过ADV212像素接口输入,有效采样值则经过隔行扫描传输到小波变换引擎中(小波变换引擎,可以对码块进行高达6级的小波分解)。进入小波变换引擎的数据被分瓦片或帧,每个瓦片或帧将通过5/3定点运算或9/7浮点运算滤波器分解成许多子带,并生成相对应的小波系数,然后写入内部寄存器中。3个熵编/解码器用来对小波系数的编码块进行背景建模和算术编码,并在压缩过程中计算最佳速率和失真度。熵编码形成的JPEG2000标准的数据码流被存入代码FIFO中。代码FIFO主要缓冲内部高速总线和低速主机接口。码流数据可通过共用的读写存取协议(

,ADDR)从主机接口输出,或者通过DREQ/DACK协议由外部DMA控制器协调下的外部DMA引擎输出。内部DMA引擎完成存储器之间以及各模块和存储器之间的高带宽、高性能传输。RISC处理器具有每一个程序和数据存储器、中断控制器、标准总线接口及定时器计数器所对应的ROM和RAM。

2 统硬件设计

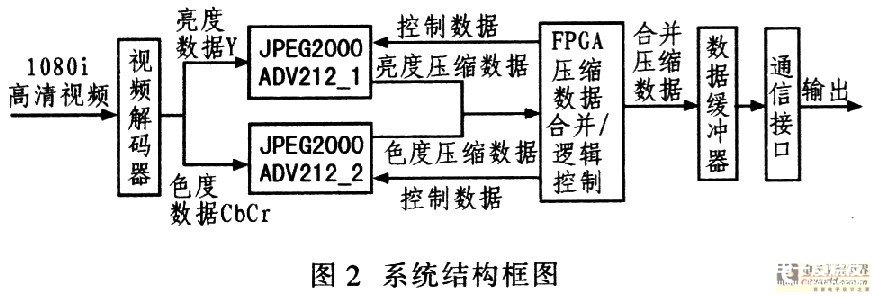

本方案作为实现高清视频数据压缩系统,首先从系统实现功能和性价比上考虑,采用FPGA+ADV212来实现。

视频解码器选取:视频解码器选用ADV7402型高清视频解码器。它采用10位ADC,12个模拟输入,支持标清(480i,NTSC,PAL,SECAM)、高清(1080i,720p)和图形RGB输入(1 280xl 024@60 Hz),可以实现与ADV212无缝连接。

ADV212片数选取:1个10 bit的高清晰度(HDTV)视频信号,输入数据传输率大约为124 Ms/s,而ADV212像素接口输入速率限制,在不可逆模式下为65 MS/s,可逆模式下为32 MS/s。这就要求系统至少要由2片ADV212组成,本系统选择2片ADV212压缩器件,YCbCr数据采取在4:2:2格式,分别完成亮度(Y)和色度(CbCr)的数据压缩处理,输入数据使用是EAV/SAV编码格式。图2所示为系统结构框图,本方案包括视频采集解码模块、视频图像JEPG200压缩模块、压缩合并模块、逻辑控制模块和通信输出模块。

FPGA选取:选用Altera公司的CycloneIII系列EP3C55F484C8器件,其具有328个用户I/O,55 856个可用逻辑元,312个嵌入式乘法器单元和4个锁相环,可轻松实现ADV212初始化及压缩数据捕获和亮度压缩数据与色度压缩数据的合并等功能。

3 ADV212器件初始化流程和参数配置

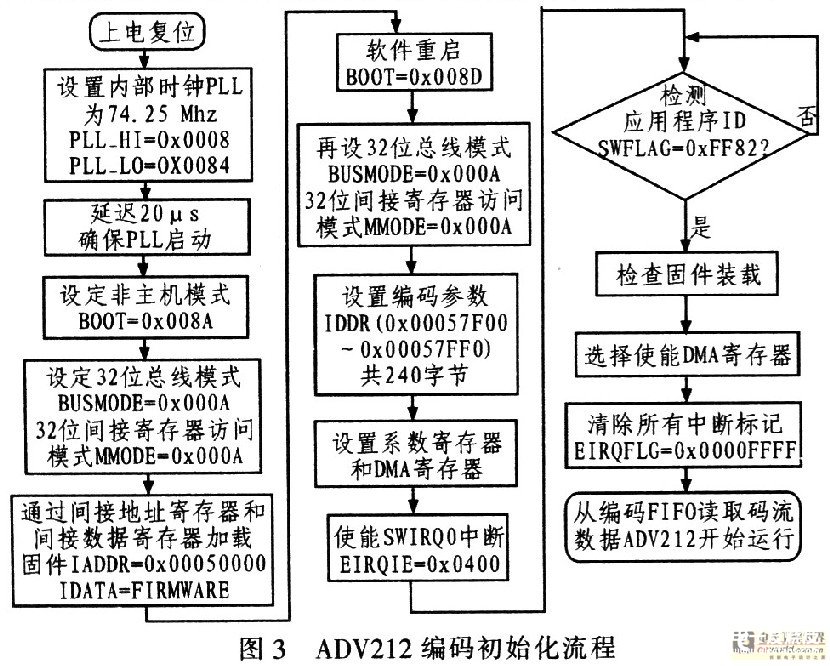

3.1 ADV212初始化流程

ADV212初始化程序依据特定的指令命令配置ADV212内部直接寄存器和间接寄存器来完成。图3所示为ADV212编码初始化流程,初始化程序从PLL寄存器、BOOT寄存器、MMODE寄存器和BUSMODE寄存器等直接寄存器的接入开始,访问直接寄存器时目标系统必须保持输入管脚ADDR,

,和HDATA(写)的状态。当装载完固件和配置参数后,软件重启,然后再次配置BUSMODE和MMODE寄存器和应用特殊寄存器。下一步,要确定正确的固件被应用ID装载。正确的固件装载能被EIRQFLG寄存器的中断或投票程序证实。当你确定固件连接装载和EIRQFLG寄存器清零后。编码开始。

3.2 ADV212参数配置

时钟配置:高清视频1080i要求VCLK为74.25 MHz。根据ADV212的数据表,JCLK必须至少为2VCLK,因此最大的脉冲频率推荐为0.35J-CLK,这接近50 MHz,这是最大的读写脉冲频率。

总线及DMA配置:HDTV(1080i)应用时,2个ADV212必须工作在不可逆最大传输率为65 MS/s模式,视频输入采取32位VDATA总线(像素接口),压缩数据输出采取2个ADV212共享32位HDATA总线(主机接口)。初始化ADV212选择属性类型5(ATTRTYPE),属性数据读取采用单一传输的DREQ/DACK DMA模式,码流读取采取脉冲传输DREQ/DACK DMA模式。

如图3所示。根据ADV212的直接寄存器配置,设定ADV212内部时钟、总线模式、间接寄存器访问模式等。ADV212_l和ADV212_2初始化流程说明如下:PLL_HIOx008h、PLL_HO,0x0084:设置VCLK为74.25 MHz;BOOT:0x008A引导模式用来那上否装载;BUSMODE:0x000A设置主机控制数据宽度和DMA数据宽度为32位;MMODE:0x000A设置间接数据存取位数和间接地址步长大小为32位;IADDR:Ox00050000设置程序存储的起始点;IDATA:0x********在程序存储器装载程序;BOOT Ox008D软件重启;BUSMODE0x000A重新设置主机控制数据宽度和DMA数据宽度为32位:MMODE 0x000A重新设置间接数据存取位数和间接地址步长大小为32位。ADV212的参数根据IADDR和IDATA设置,参数配置说明如下:IADDR 0x00057F00 ADV212_1和ADV212_2的编码参数起始地址;IDATA 0x02010503(ADV212_1)、0x03010503(ADV212_2)02=1080i亮度(03=1080i色度);0l=10位精度;05=5级小波变换;03=Y,C单级;IDATA 0x03000000 03=码块大小为128x32;00=不可逆9x7小波;00=跳过无字节区域;00=无属性数据输出;IDATA0x01019500(ADV212_1)、0x01008700(ADV212_2) Ol=目标视频域,帧大小;019500=10:1压缩率(008700=30:1压缩率);IDATA 0x00000001 00=LRCP级数格式;00=EAV.SAV编码,所有阴极同步;00=Qfaetor是1X;01=编码格式是.j2c;IDATA0x00000000保存参数。

上述配置好以后,ADV212_1和ADV212_2的EIRQFLG(地址Ox6h)写入0x0400去清除软件中断(SEIRQ0)并开始程序,当DREQ0变为有效,ADV2-12准备从CODE FIFO传输数据,主机按照ADV212特定时序说明开始数据传输。

4 FPGA结构功能

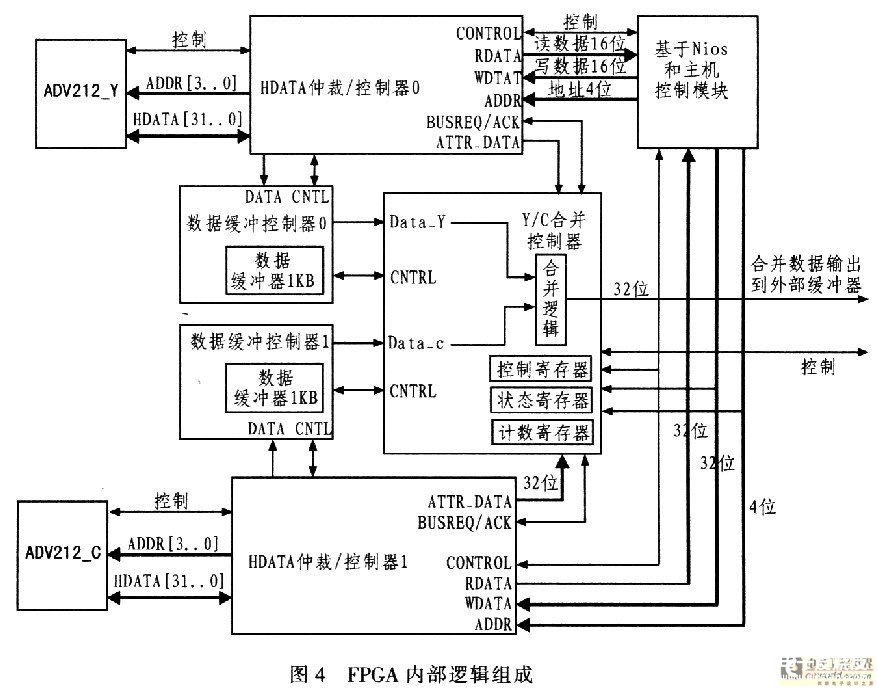

图4为FPGA内部逻辑组成,FPGA主要由以下功能模块组成:1)主机逻辑,基于Nios的嵌入式主机逻辑模块,主要实现2片ADV212的读写操作,实现对ADV212的初始化和固件下载;2)ADV212仲裁逻辑,实现2片ADV212压缩数据同步,应答总线判断状态的应答信号功能;3)Y/C合并逻辑,该部分根据读出的属性和代码信息,实现亮度压缩数据与色度压缩数据的合并功能;4)数据缓冲控制模块,缓冲外部DMA通道读取速率和亮度/色度合并逻辑模块间的数据流。

在FPGA主控模块中,要确保ADV212加载了正确的固件,通过4个步骤来实现:第1步是向外部中断使能寄存器中写入0x0400来屏蔽软件中断0位:第2步等待到中断引脚IRQ被拉低,第3步检查外部中断标记寄存器的EIRQFlLG[10]位是否被设置,第4步从软件标记寄存器中读应用标识,如果读到的是0XFF82,则说明固件加载正确,系统可以开始工作。

系统开始工作时,FPGA在仲裁,控制模块中将从ADV212属性FIFO中读取的分区字节数信息进行分析判断,数据缓冲控制模块将ADV212代码FIFO中读到的压缩数据进行寄存。仲裁/控制模块分析结果来控制亮度/色度合并逻辑模块,码流从Y数据开始从两个器件相对部分(Y和CbCr)交错合并,输出到缓冲器再由通信端口输出。

5 结束语

基于FPGA+ADV212结构的高清视频压缩系统可实现高清视频(YCbCr 4:2:2格式)信号的实时处理,本系统具有性价比高、可靠性好、调整灵活、压缩信号易恢复等优点。但本系统采用的是不可逆9/7小波变换,视频处理具有一定的失真,为获取1080i视频信号具有更好的特性(如无损压缩),建议用3片或3片以上的ADV212来处理信号,信号格式可采取YCbCr 4:4:4格式。随着JPEG2000的广泛应用,专用图像压缩器件ADV212必将被越来越多地应用到视频和图像压缩方面的领域中。

责任编辑:gt

-

【RTC程序设计:实时音视频权威指南】音视频的编解码压缩技术2024-04-28 1237

-

高清视频解码器功能介绍2023-08-17 3665

-

什么是视频解码器?2023-05-06 7147

-

如何在Hive中进行数据压缩2019-07-08 2142

-

视频编解码器是什么,编解码器技术原理作用2019-06-24 15310

-

ADV7181C视频解码器和图形数字化仪的性能与特点2019-06-06 4388

-

基于TMS320C6678处理器的节能型可扩展H.265/HEVC解决方案2019-01-02 4426

-

高清解码器的作用2018-12-10 14747

-

103-基于TMS320C6455和EP3C40F484C8的Camera Link 图像处理平台2014-07-01 2831

-

102-基于TI DSP TMS320C6455和Altera FPGA EP3C40F484C8软件无线电处理卡2014-06-30 3769

-

基于TI TMS320DM6467无操作系统Camera Link智能图像分析平台2012-12-04 3001

-

基于TI DSP TMS320C6455和Altera FPGA EP3C40F484C8软件无线电处理卡2012-06-13 3549

-

HDTV信源解码器2006-03-11 2081

全部0条评论

快来发表一下你的评论吧 !