DSP+ZYNQ核心板是如何实现核间通讯的?

描述

这款DSP + ZYNQ核心板,是如何实现核间通讯呢?

核心板简介

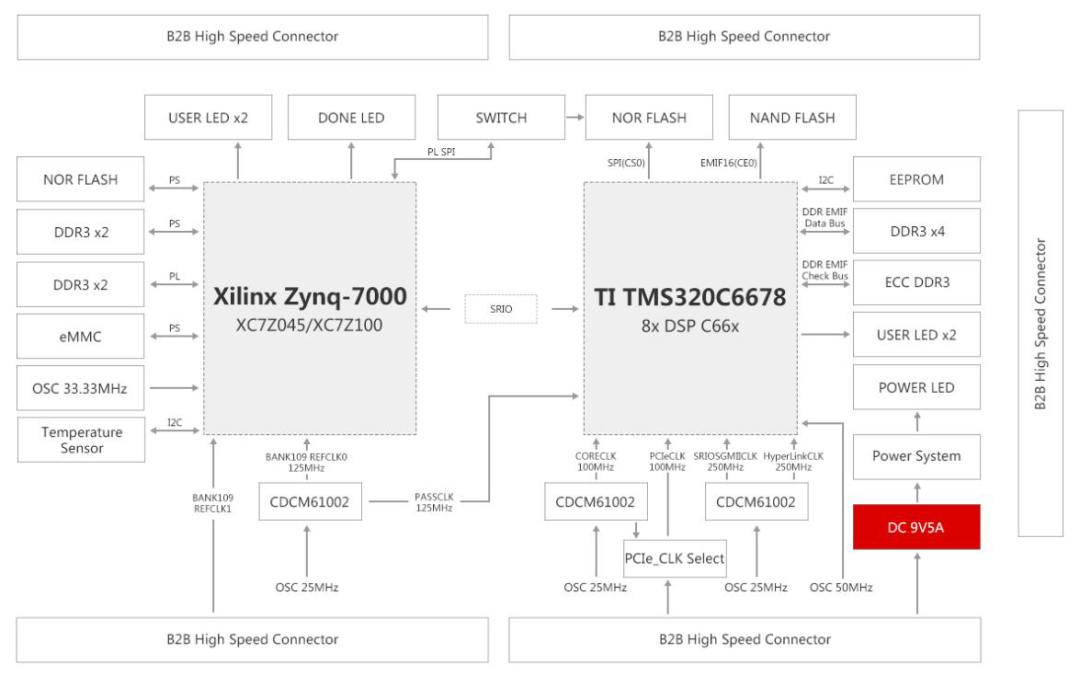

SOM-TL6678ZH是一款基于TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP,以及Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC处理器设计的高端异构多核工业级核心板。TMS320C6678每核心主频可高达1.25GHz,XC7Z045/XC7Z100集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源。核心板内部DSP与ZYNQ通过SRIO通信总线连接,并通过工业级高速B2B连接器引出千兆网口、PCIe、HyperLink、EMIF16、USB、CAN、UART、GTX等通信接口。

本文主要介绍DSP + ZYNQ基于SRIO的通信案例。

1

SRIO简介

SRIO(Serial Rapid I/O)是高速串行RapidIO通信接口,常用于DSP与DSP、DSP与FPGA之间的数据高速传输。SRIO引脚占用数量少,支持多点传输,速率可配置为1.25Gbps、2.5Gbps、3.125Gbps和5Gbps。

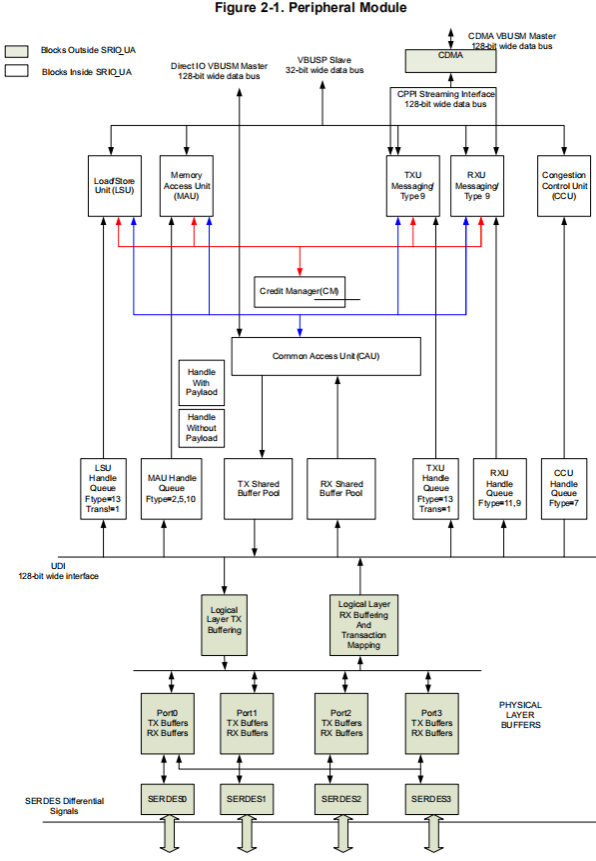

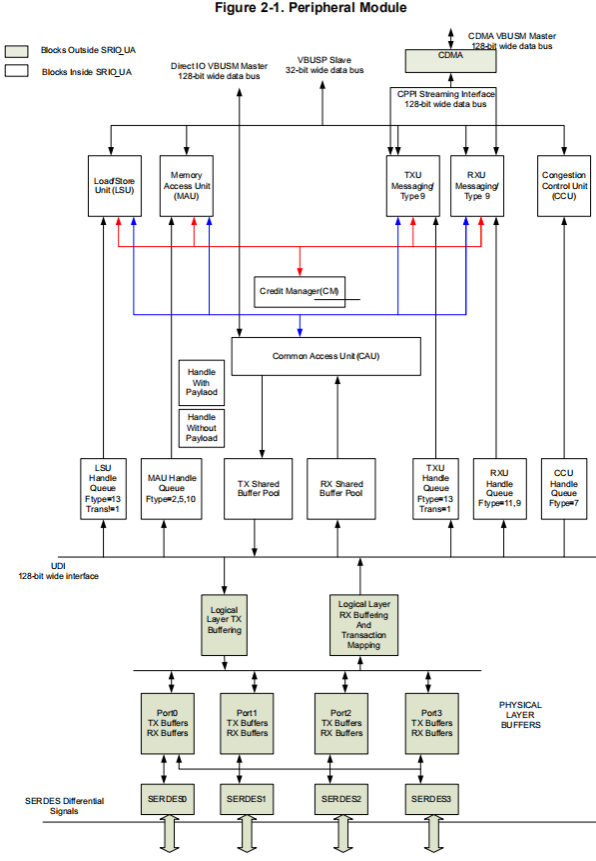

SRIO包含三层结构协议,即物理层、传输层、逻辑层。

(1) 逻辑层:定义包的类型、大小、物理地址、传输协议等必要配置信息。

(2) 传输层:定义包交换、路由和寻址规则,以确保信息在系统内正确传输。

(3) 物理层:包含设备级接口信息,如电气特性、错误管理数据和基本流量控制数据等信息。

RapidIO体系结构如下:

2

SRIO通信案例

1.1 案例功能

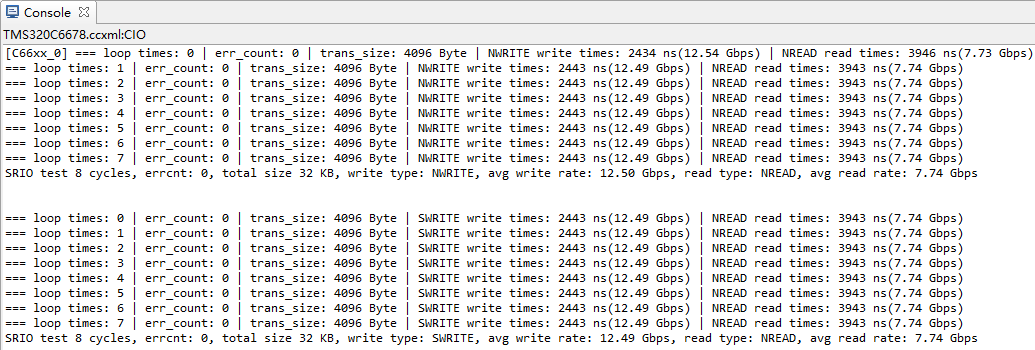

评估板DSP端和ZYNQ PL端进行SRIO通信测试,并统计读写速率。评估板DSP端作为Initiator,评估板ZYNQ PL端作为Target。SRIO默认配置为x4模式,每个通道速率5Gbps,并分别使用NWRITE + NREAD和SWRITE + NREAD模式进行测试。ZYNQ PL端使用一个36Kbit的BRAM作为设备存储空间,将DSP端发送的过来数据储存至BRAM。

1.2 案例测试

先加载运行ZYNQ PL端程序,再运行DSP端程序,CCS Console窗口将打印测试结果。

NWRITE + NREAD模式:NWRITE = 12.50Gbps NREAD = 7.74Gbps

SWRITE + NREAD模式:SWRITE = 12.49Gbps NREAD = 7.74Gbps

备注:由于写测试仅统计发送数据至SRIO FIFO的时间,读测试统计发送读请求并等待Target发送数据完成的时间,因此写速率将比读速率高。

2.3关键代码

2.3.1 DSP工程

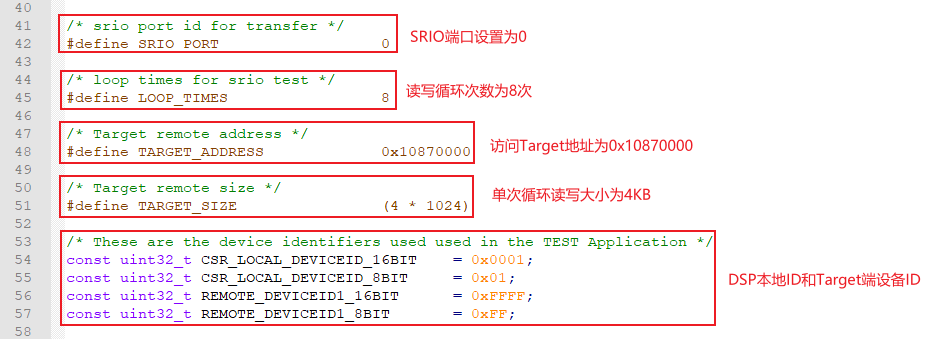

(1) 程序配置说明。

(2) 使能SRIO PSC,初始化SRIO子系统,SRIO通信测试。

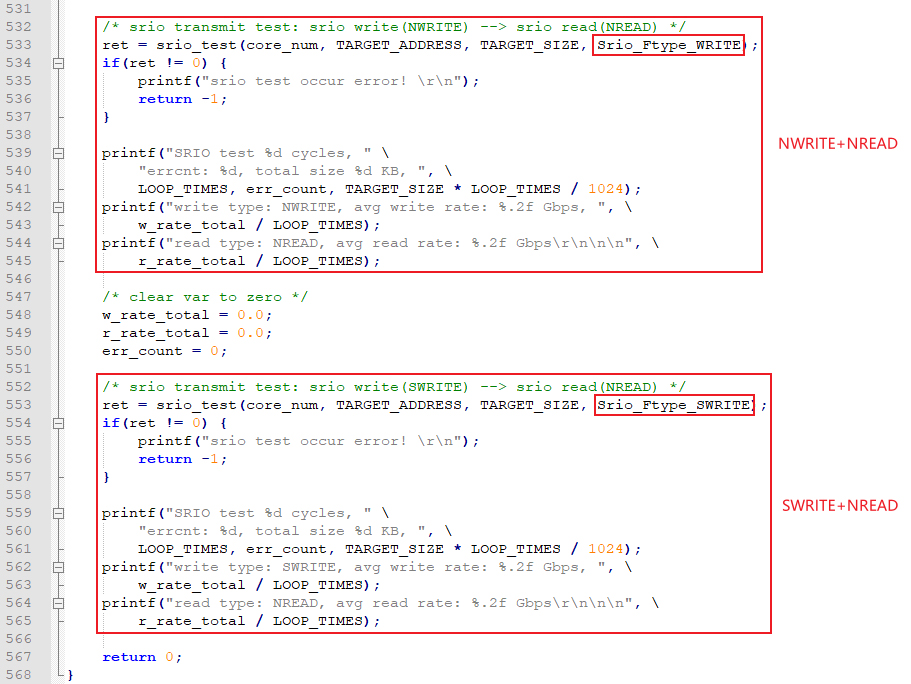

(3) 以NWRITE + NREAD和SWRITE + NREAD模式进行SRIO通信测试,单次读写大小为transfer_size,单位为Byte。w_format_type写格式类型在main函数中调用srio_test()传入。

(4) SRIO写测试流程。

(5) SRIO读测试流程。

2.3.2 ZYNQ工程

(1) 端口定义。

(2) 使用STARTUPE2原语提供的EOS作为系统复位信号,CFGMCLK(65MHz)作为系统时钟。

(3) 例化Serial RapidIO Gen2 IP核。

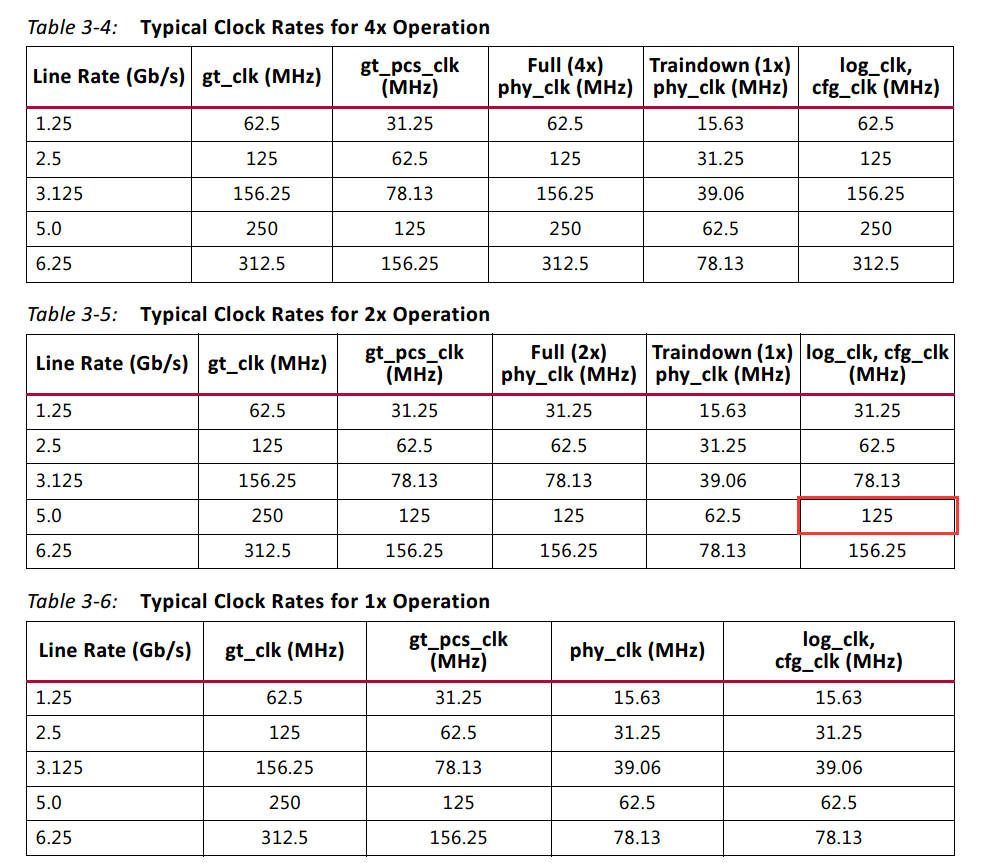

其中Serial RapidIO Gen2 IP核输出的log_clk为125MHz。

(4)调用srio_response_gen模块,其接口与Serial RapidIO Gen2 IP核连接。

SRIO详细开发说明请参考产品光盘“6-开发参考资料TI官方参考文档”目录下的《Serial Rapid IO (SRIO) User Guide.pdf》文档。

原文标题:想了解DSP+ZYNQ核间通讯?看完这篇就够了

文章出处:【微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!2024-09-02 10225

-

正点原子ZYNQ7015开发板!ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2,性能强悍,资料丰富!2024-09-14 8240

-

1创龙 C6678八核DSP核心板2016-03-30 5933

-

安卓核心板-安卓智能方案定制2018-09-12 2256

-

想了解DSP+ZYNQ核间通讯?看完这篇就够了|基于DSP + ZYNQ的TL6678ZH-EVM评估板2021-03-16 4439

-

ZYNQ-7010核心板资源都有哪些呢2021-11-04 4445

-

【资料分享】Zynq-7010/7020工业核心板规格书(双核ARM Cortex-A9 + FPGA,主频766MHz)2023-06-21 2627

-

全志T113i全国产核心板上市2023-11-20 1851

-

打造Zynq平台性价比标杆,米尔强势推出MYC-Y7Z010/007S核心板2018-03-07 10782

-

XQ6657Z35-EVM 的DSP + ZYNQ核心板,SRIO通讯2022-12-05 1339

-

Zynq7015 SoC工业核心板手册2023-01-04 1056

-

Xilinx Zynq-7010/7020邮票孔核心板全新上市,引出所有IO!!2021-10-25 2798

-

DSP+ARM+FPGA,星嵌工业级核心板,降低开发成本和时间2023-08-01 1418

-

DSP+ZYNQ双核通信案例开发手册2021-12-28 1433

-

骁龙665安卓核心板_SM6125核心板参数_安卓核心板高通方案定制2024-11-13 3916

全部0条评论

快来发表一下你的评论吧 !