基于单片机和无源三阶滤波器实现自适应式时钟源的应用方案

描述

时钟技术在现代科学技术中有着广泛的应用。计量测试系统需要高精度的参考源,通信系统需要高精度的同步时钟作参考,以此来协调全网所有基站的工作。传统时钟源的内外频标切换是用检波器对外频标进行检波,用检波出来的信号去控制晶振的电源通断,从而实现切换。但这种传统的检波方式,只能对频标的有无进检波,无法检出参考的频率,而且要求内外频标的频率相等,因此,存在硬件电路复杂,需要外部控制,成本高等缺点。

本文设计的自适应式时钟源的内外频标切换采用软件检测和控制来适应5 MHz,10 MHz和20 MHz频标,通过改变芯片内部寄存器的频率控制字,改变参考频率的倍频次数,最终得到所需频率的时钟。时钟源采用目前应用最为广泛的一种频率合成方法中的锁相技术,具有低杂散、低相噪、输出带宽较宽的特点。与传统的内外频标切换时钟源相比,内外频标切换可以不用外部控制,达到完全自适应多个不同频率外频标,并且可以省去检波、继电器切换电路,具有硬件电路简单,成本低等优点。

1 自适应式时钟源内外频标的切换原理

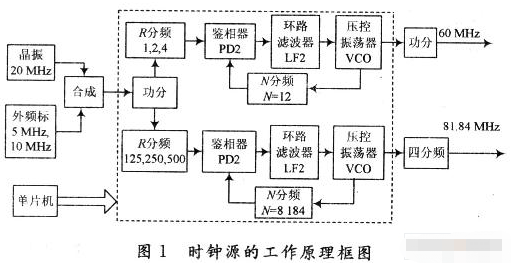

图1给出的锁相时钟源是单片机通过串行数字接口对锁相芯片内部的分频器进行设置,将需要的频率N次分频作为一路鉴相输入;将参考信号进行R次分频,作为另一路鉴相输入,通过鉴相器后得到反映两路鉴相信号误差的控制电压,经过低通滤波器后,取出其中缓慢变化的直流电压分量,用来控制压控元件电容量的变化,将VCO的输出频率拉回到稳定值上来,环路锁定。

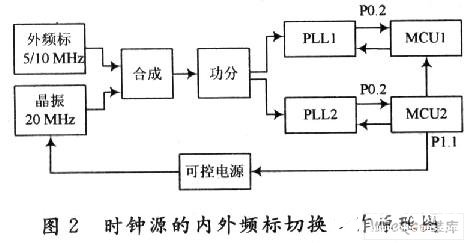

时钟源的内外频标切换主要由软件来实现。图2中单片机的P1.1口用来控制内部晶振加电,P0.2口用来检测环路锁定指示。当外加频标时,单片机通过串行数据口,给锁相环芯片送入5 MHz参考的频率控制字,延时等待,检测锁定指示电平为高,则环路锁定在5 MHz频标上,单片机停止送数,降单片机的内部时钟,来避免单片机带给环路的干扰;如果锁定指示为低,单片机继续送10 MHz参考的频率控制字,延时等待,如果检测锁定指示电平为高,则环路锁定在10 MHz频标上,单片机停止送数,降单片机的内部时钟;如果锁定指示为低,单片机将通过P1.1口的高电平,控制稳压块LT1762,给内部的20 MHz晶振加电,然后单片机送20 MHz参考的频率控制字,最终环路锁定。如果内外频标同时外加,锁定指示电平高低发生跳变,环路处于失锁状态,单片机随即切断内频标电源,环路重新锁定在外频标上。

传统的内外频标切换时钟源的内外频标频率是相同的,而自适应式时钟源内外频标频率不同,外频标还可以有几种不同频率的选择。因此,该时钟源在整机使用中对外部频标的要求大大降低,内部的恒温晶振也保证了在没有外频标情况下,时钟源仍然能正常工作,增加了在整机系统使用中的兼容性。软件的实时监测又可以保证在内外频标同时存在的情况下,及时切断内部晶振的电源,避免两种不同的参考频率,对环路带来不必要的干扰。所以改进后的自适应时钟源从产品的适应性和使用的方便性都大大增强。

在调试中发现,若外频标为方波,上升沿比较陡,对频标的电平要求不高,大于0 dBm即可;若外频标为正弦波,上升沿不够陡,因此如果环路预先锁定在内频标上,再加外频标,外频标的信号需强于内频标,环路才能重新锁在外频标上。所以,外频标为正弦波的时侯,电平必须大于5 dBm,环路才能在内外频标间自适应切换。

2 自适应内外频标切换时钟源的设计与实现

2.1 自适应式时钟源的内外频标切换软件的设计

该时钟源软件的流程如图3所示。

2.2 自适应式时钟源的环路滤波器的设计

环路滤波器的设计在整个时钟源中很关键,既要兼顾5 MHz,10 MHz外频标,又要兼顾20 MHz内频标。因此,环路的设计必须同时考虑到各个频标的因素。鉴于这种情况,设计环路时,对参考频率分别进行1,2,4分频,使得环路在多个频标下,均以5 MHz鉴相频率,相同的N分频次数,满足锁相环的要求。所以,对环路带宽必须合理选择。一般情况下,选择在参考源噪声源和VCO噪声源谱密度线的交叉点。

在设计中采用无源三阶滤波器,环路带宽大致设为45 kHz,相位裕量为65°。环路带内的相位噪声取决于晶振相位噪声,环路带外的噪声取决于压控振荡器的相位噪声。时钟源输出信号的相位噪声是所有噪声同时作用的结果。图4为锁相环附加噪声源的系统框图。

数字锁相环在锁定状态下可以认为是线性系统,应用线性叠加原理,将各噪声源反映到时钟源输出端的相位噪声功率谱密度相加,则可得到总的相位噪声功率谱密度(单位:dBc/Hz):

其中:Sr(f),SPD(f),SLP(f),SVCO(f),So。(f)分别为参考频标、鉴相器、环路滤波器、VCO、时钟源输出的相位噪声,单位均为dBc/Hz,H(j2πF)为环路的有效传输函数。上式右边第一项为环路的低通输出相位噪声谱,第二项为环路的高通输出相位噪声谱。

参考信号的相位噪声对输出信号相噪的贡献L1(f)(单位:dBc/Hz),可用式(1)计算:

式中:Lr(f)为晶振的相位噪声(单位:dBc/Hz);鉴相器的基底相噪对输出信号相噪的贡献L2(f)(单位:dBc/Hz),可用式(2)来计算:

式中:LpD(f)为鉴相器的基底相噪(单位:dBc/Hz);Fc为鉴相频率(单位:Hz)。

由式(1)和式(2)得,在环路带内输出信号的相位噪声L(f)(单位:dBc/Hz),可由式(3)得到:

利用式(3)可估算出输出信号的相位噪声为-120 dBc/Hz@1 kHz。

由于参考频率的不同,R分频的次数不同,相位噪声改善的不同,加之N倍频相位噪声恶化的差异性,最终环路在各频标作用下,表现出来的相位噪声也各有差异,不尽相同。

3 实验结果及其分析

实验结果证明,三种参考频率在相同的相位噪声基准下,20 MHz频标倍频次数最少,相位噪声曲线最好;5 MHz频标倍频次数最多,相位噪声也能满足要求。图5给出了E4440A测试的时钟源输出相位噪声曲线(其横坐标表示频率,纵坐标表示相位噪声)。

从图5可以看出,时钟源实际输出相位噪声与根据上述公式估算的结果比较接近,满足系统对时钟源相位噪声的要求,这说明本文提出的内外频标自适应式时钟源的环路带宽设计合理,电路布局优化,设计方法是完全可行的。

4 结 语

新设计的内外频标自适应式时钟源具有电路硬件结构简单,成本低,相位噪声低,杂散小的特点。内外频标的切换不用外部控制,完全自适应多个不同频率的内外频标,而且产品的适应性和使用的方便性都大大增强。目前该时钟源已在数字基带系统中得到广泛应用。

责任编辑:gt

-

自适应Notch滤波器的FPGA实现2011-02-17 1848

-

二阶无源滤波器电路2012-04-19 6944

-

改进的变阶数LMS自适应滤波算法2010-05-13 3778

-

转:有源滤波器和无源滤波器2011-07-28 6927

-

三阶不对称滤波器电路2009-12-07 2085

-

无源滤波器基本概念2010-04-13 7091

-

无源RC滤波器设计性学生实验方案构思2016-01-14 1107

-

变阶自适应滤波器及其算法研究2017-01-08 927

-

一种三阶Volterra自适应滤波算法2017-01-07 901

-

无源滤波器的类型2018-08-30 18900

-

采用二阶无源环路滤波器实现三阶电荷泵锁相环的设计2020-07-24 4263

-

如何设计无源lc滤波器的频率2023-12-01 2722

-

无源滤波器和有源滤波器的区别2024-09-26 2581

-

什么是无源滤波器2024-10-16 4136

-

有源滤波器与无源滤波器的区别2025-06-18 1377

全部0条评论

快来发表一下你的评论吧 !