支持片上测试和调试功能的在线调试模块的应用设计

描述

1 引言

集成电路制造工艺的飞速发展推动了信息技术的发展,而信息技术的核心是微处理器技术。微处理器的总体发展趋势是功能越来越强大,工作频率越来越高。由于微处理器芯片从设计过程到生产过程中都可能产生一些缺陷,这些缺陷都将最终影响微处理器的功能和性能,为了保证微处理器功能的正确性,减少设计风险,对其进行测试和调试是必不可少的。但是微处理器的发展趋势也导致了微处理器芯片的测试与调试变得更加复杂,板级调试系统设计和调试软件的开发也越来越困难。特别是进入21世纪,集成电路进入了高度集成的系统芯片SoC(System-On-Chip)时代,而嵌入式微处理器是系统芯片的核心。传统的微处理器的调试方法采用监测并控制其地址与数据总线的方法。对于高度集成化的系统芯片,由于封装尺寸的限制,不可能将嵌入片内的微处理器信号引出片外,通过外部直接测试和调试。在板级,通过软件模拟、验证和分析等系统功能调试已经远远不能满足功能正确性调试和故障定位等要求,所以微处理器芯片,特别是嵌入式微处理器,硬件上支持片上测试和调试功能显得十分重要。

为了能让嵌入式微处理器的片上调试功能也能够像高级语言编程工具那样支持断点设置、单步执行、寄存器内容的查看和内存内容查看等功能,文章提出了一种在线调试模块设计,此设计为嵌入式微处理器增加了一些专用的调试引脚,通过这些引脚可以响应硬件和软件触发,提供开始/停止调试模试,单步调试操作以及程序执行的跟踪。有了这些引脚,还可以对微处理器做调试接口,提供更好的调试性能,查错功能,从基本停止/ 开始或单步执行到硬件、软件断点支持再到对数据存储区、程序存储区和SFRs的访问和修改以及对程序进行跟踪。

2 嵌入式微处理器的片上调试原理

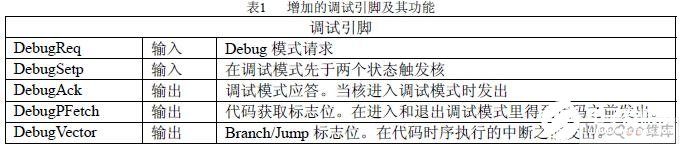

为微处理器增加的调试引脚及其功能如表1所示。

可实现的调试功能:

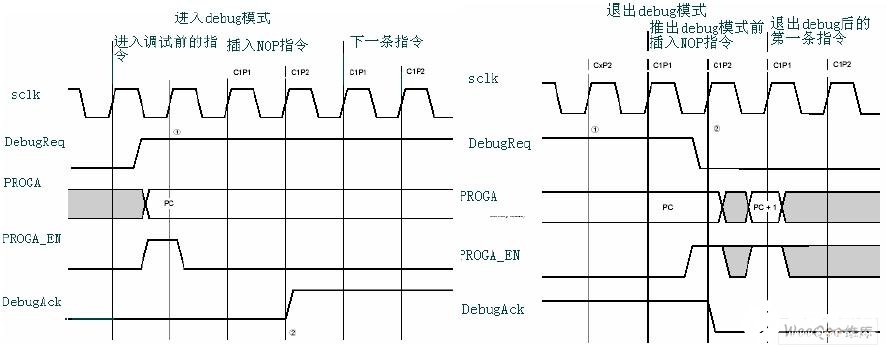

⑴ 开始/停止debug模式

可以通过两种方式进入调试模式即硬件请求或者软件中断指令TRAP。硬件请求进入到debug模式将发出一个DebugReq信号。这个信号在核运行的每个指令操作的最后一个周期的第一个阶段进行采样,若是采样信号为高,核将完成当前指令,插入一个NOP指令。在NOP指令的第一阶段的最后核将发出一个DebugAck信号然后进入debug模式。它的时序图见图1。当TRAP指令被执行的时候,核只是简单的发送一个DebugAck信号,然后在这个单一周期指令第一个阶段的结束进入debug模式。

在debug模式,核在每个机器周期的第一阶段的最后采样DebugReq信号,当DebugReq信号为高之后采样一个机器周期的信号,如果为低则离开调试模式(置DebugAck信号无效)。它的时序图见图2。注意:如果在TRAP下进入调试模式,外部硬件必须在重新置信号为低之前置DebugReq信号为高一个机器周期才可以离开试模式。

图1 进入debug模式的时序图 图2 退出debug模式的时序图

①DebugReq采样信号为高电平。① DebugRep采样信号为高电平。

②微处理器内核进入调试模式,置DebugAck 为高电平。 ② DebugRep 采样信号为低,CPU核置DebugAck为低并离开调试模式。

其中 PROGA 为程序存储器的地址总线,PROGA_EN 为程序存储器的地址总线使能。它们是微处理器内核已经设计好的。

⑵单步调试

在调试模式下,把DebugReq 置成无效的低信号,微处理器执行一个用户指令,等待DebugAck 信号无效的时候指出离开了调试模式,再把DebugReq 信号置成高电平。

⑶程序执行的跟踪信号 DebugPFetch 和Debug Vector 支持程序追踪。当程序代码在下一个上升缘被读取的时候DebugPFetch信号发出,它并不发送程序数据提取的信号。(例如使用MOVC 指令读取数据)。当在程序计数器里的下一个代码表现为一个间断性程序的时候DebugVector 被发送,(例如Jump,Call 或者Return 指令)。

⑷外部数据存储器、SFR、内部数据存储器的读和写

提供了一个时序发生器一个RAM,它包含了一些访问存储器的指令。当一个时序开始的时候,DebugStep信号发送直到时序结束。因此时序指令以全速的处理器速度运行。在微处理器程序输入端设计了一个多路选择器允许时序发生器的指令给内核执行。时序发生器中的指令总是把想访问的存储器和SFRs 中的数据加载到累加器A 中,因此只要把XRAMD0 总线的状态存储到结果储存器中,然后通过JTAG 接口把结果储存器读出就可以得知存储器和SFRs 中的数据。给出一个读内部数据存储器的时序发生器中的程序。其中Temp1,Temp 是时序发生器中定义的存放中间数据的寄存器。

3 微处理器的在线调试模块的结构设计

在微处理器内核中设计的调试部分为DebugReq 信号锁存器、调试状态机、操作码指示器。

调 试 状 态 机 是 有 DebugReq 、DebugAck、DebugStep、TRAP 信号来控制的。它有4 种状态:00、01、10、11。00 表示用户状态。01 表示调试开始状态,此状态时已检测到DebugReq 信号有效,插入NOP 指令。01 表示单步调试模式,已检测到DebugStep 信号有效。11 为调试模式。状态机为10、11 时都要置DebugAck 为有效信号,进入Debug 模式。

操作码指示器是有指令译码器和状态机译码器控制的。当程序代码在下一个上升缘被读取的时候(而不是程序数据的读取), 操作码指示器就置DebugPFetch 为有效信号,以实现对程序的跟踪。当操作码指示器检测到程序计数器为不连续数值时置DebugVector 为有效信号。

外部数据存储器、SFR、内部数据存储器的读和写是基于1149.1 JTAG 的设计。IEEE 1149.1 JTAG 接口是专门为集成电路测试和电路板系统测试制定的国际标准。TDI(数据输入),TMS(TAP 模式选择),TCK(测试时钟输入),TRST(测试接口复位),TDO(数据输出)是JTAG 的5 个外部管脚。调试部分电路为:调试扫描链、调试数据寄存器、指令译码器、时序发生器和多路选择器(MUX)。时序发生器是一个RAM,它包含了一些访问存储器的指令。指令010110xx 表示启动时序发生器,把预先存好的访问程序送到微处理器的程序输入端(PROGDI),微处理器执行这些程序,实现对存储器、SFR 的访问。指令译码器对调试指令进行译码,并发出调试控制信号,比如:设置DebugReq 为有效,进入Debug 模式;启动时序发生器,控制多路选择器(MUX),让PROGDI 上的信号为时序发生器中的指令。调试数据寄存器是为存放中间数据和访问结果数据的。调试扫描链对中间数据和访问结果进行查看。

4 结论

此设计给微处理器内核增加了一些调试引脚。实现了开始/停止调试模试,单步调试操作以及程序执行的跟踪的调试功能。这些引脚使内核具有很好的可扩张性,可对芯片增加调试接口,实现更强大的调试功能。基于1149.1 JTAG 接口的对存储器、SFR 访问,既可以使芯片原有的测试功能不受影响,又可以节省硬件,减少开销。带Debug 模块的微处理器在SMIC 的0.25um 标准单元库映射综合后,可工作在120MHz。仿真的结果表明,扩充Debug 功能的JTAG 接口所增加的芯片面积很少,而且在对存储器、SFR 进行访问时不影响处理器的工作速度。

责任编辑:gt

-

基于SoPC的通用在线调试器设计2011-01-16 1181

-

接口调试与测试工具postman安装说明与基础功能2022-07-15 1927

-

单片机串口模块调试方法2023-07-28 2419

-

英创Eclipse支持在线调试Linux应用程序2017-03-24 4113

-

玩转Zynq连载5——基于Vivado的在线板级调试概述2019-05-24 3196

-

一种嵌入式微处理器中的在线调试模块设计2009-08-14 487

-

嵌入式处理器在片调试功能的设计2011-06-29 805

-

总线实现片内硬件调试支持单元设计2011-08-11 2205

-

总线实现片内硬件调试支持单元设计2017-12-01 600

-

基于双端口RAM中多行代码设置断点功能实现新型通用调试模块的设计2020-03-10 1366

-

FPGA开发在线调试和配置过程2020-11-01 5721

-

PLC编程中模拟调试和在线调试2022-01-06 6944

-

通过片上仪器和逻辑分析轻松进行FPGA和ASIC调试2022-07-09 907

-

EB-USB-DA 调试适配器带编程功能的片上调试仿真器用户手册2023-04-21 504

-

PLC远程调试模块是什么?PLC远程调试模块的功能2024-05-22 2265

全部0条评论

快来发表一下你的评论吧 !