一种基于数字改良的SRAM设计存内计算方案

今日头条

1191人已加入

描述

最近的ISSCC上,台积电的研究人员提出了一种基于数字改良的SRAM设计存内计算方案,能支持更大的神经网络。

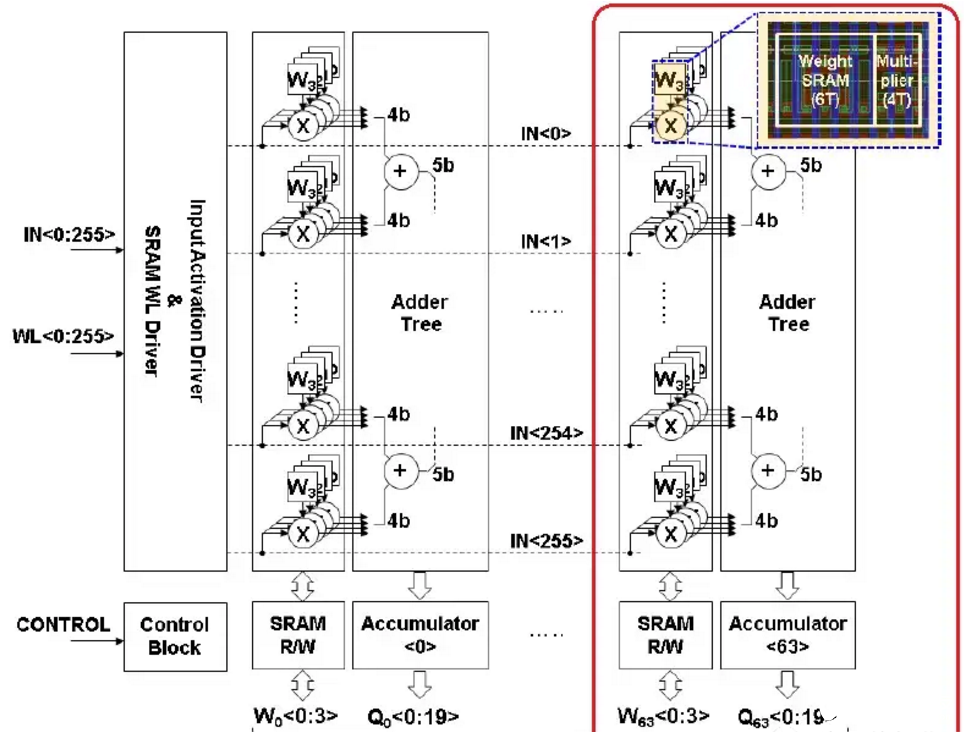

上图显示了台积电用于其测试的扩展SRAM阵列配置——阵列的一部分被圈出。每个切片具有256个数据输入,它们连接到“ X”逻辑(稍后将对此逻辑进行更多介绍)。数据输入向量的连续位在连续的时钟周期中提供给“ X”门。每个切片存储256个4位权重段,每个数据输入一个权重半字节。这些权重位使用常规的SRAM单元,因为它们可能会经常更新。存储在每个权重位中的值连接到“ X”逻辑的另一个输入。

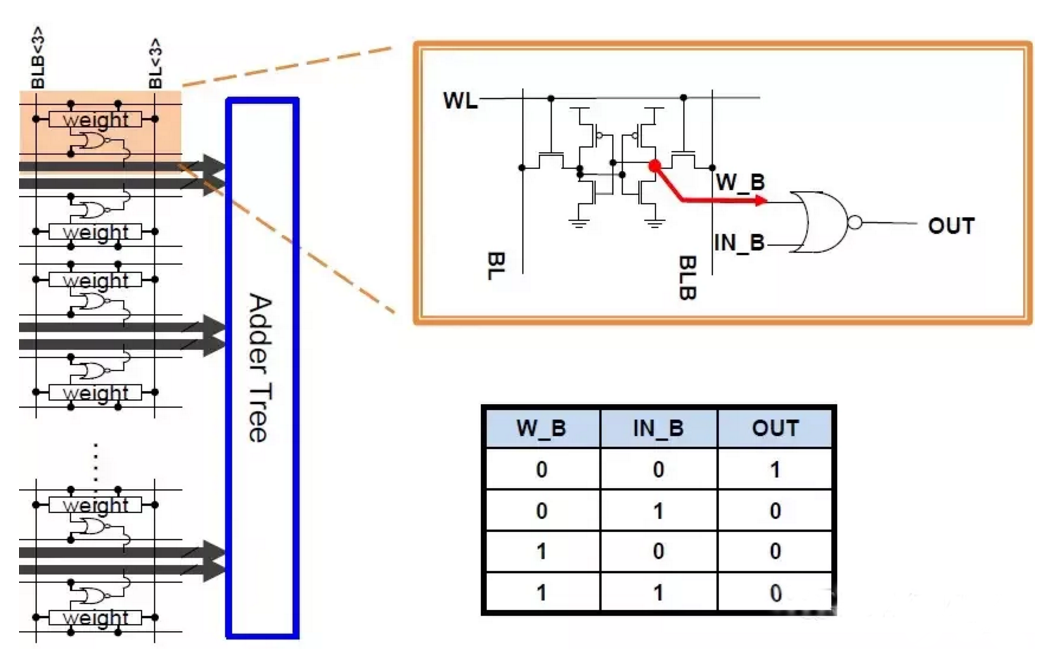

下图说明了如何将此逻辑集成到SRAM中

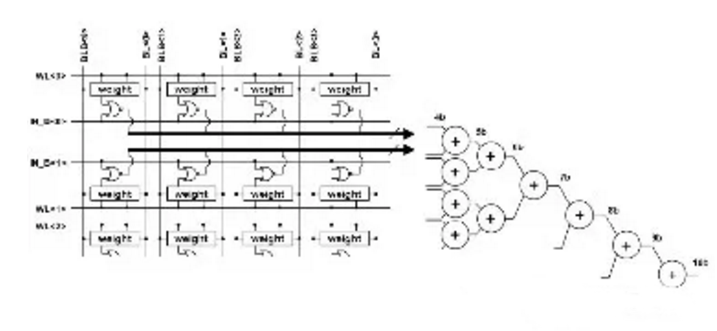

其中“ X”是2输入或非门,具有数据输入和权重位作为输入。(两个“一位”值的乘积由“与”门实现;通过使用反相信号值和DeMorgan定理,2输入“或非”门在面积和功率方面都具有效率。)在每个限幅之间,有一个加法器树和一个加法器树。集成了部分和累加器逻辑,如下图所示。

上图中的加权位存储使用常规的SRAM拓扑-对于6T的位单元,加权位字线和位线照常连接。每个单元上的存储值都扇出到或非门的一个输入。

每个切片的输出表示每个权重向量的半字节的部分乘积和。扩展数组之外的其他逻辑提供了移位和相加计算,以实现更宽的权重值表示。例如(有符号或无符号整数)16位权重将合并来自四个条带的累加器结果。

fqj

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

第二届知存科技杯华东高校存内计算创新应用大赛正式启动2025-05-06 1069

-

开源芯片系列讲座第24期:基于SRAM存算的高效计算架构2024-11-27 1618

-

知存科技启动首届存内计算创新大赛2024-11-21 1385

-

直播预约 |开源芯片系列讲座第24期:SRAM存算一体:赋能高能效RISC-V计算2024-11-16 1352

-

存内计算原理分类——数字存内计算与模拟存内计算2024-05-21 6232

-

论基于电压域的SRAM存内计算技术的崭新前景2024-05-17 2182

-

存内计算技术工具链——量化篇2024-05-16 2730

-

什么是存内计算2022-08-08 5938

-

分享一种DTCM,SRAM1,SRAM2,SRAM3和SRAM42021-08-03 1657

-

求一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案2021-04-26 1337

-

一种低成本的 高速SRAM 替代解决方案2017-07-05 1944

-

一种基于SRAM的FPGA的加密方法2011-03-16 845

全部0条评论

快来发表一下你的评论吧 !