基于数字可编程增益仪表放大器AD8250实现数据采集系统的设计

描述

AD8250(G=1、2、5或10)数字可编程增益仪表放大器(PGIA)采用最新工艺和新的电路技术以减小尺寸并且提高数据采集和过程控制应用的性能。其软件增益控制允许设计工程师简单地设置其精密模拟前端。AD8250通过集成匹配电阻、开关以及运算放大器,减少了器件数量。这款产品具有快速建立时间、低失真以及低噪声,从而使其成为驱动模数转换器(ADC)的理想放大器,而无需额外的缓存器,从而进一步减少了所需器件的数量。

数据采集系统一般与具有在1 mV~±10 V之间变化的满量程输出信号的各种传感器连接。这些传感器也具有多种输出阻抗,因此数据采集前端必须提供高输入阻抗以避免负载误差。仪表放大器通常用于调理来自传感器的差分信号。然而,由于信号大小变化较大,因此需要许多不同的增益。AD8250适合于解决数据采集系统设计工程师所面临的四大难题, 最大程度地提高ADC的性能;提供对模拟信号调理的数字控制;占用更小的PCB面积;并且降低成本。

四大设计难题的解决

第一个难题是在不降低ADC性能的情况下提供信号调理。当今最新的ADC具有非常高的信噪比(SNR),例如16位ADC通常可提供90 dB的SNR。前端应提供共模抑制和增益。此外,其输出必须在ADC的采集时间内建立。

第二个难题是设计增益可编程模拟信号调理电路。数据采集系统具有多种软件控制功能。最方便的产品应具有数字控制模拟前端。当前,设计工程师必须设计他们自己的解决方案,因为现有的混合信号解决方案并不能提供令人满意的模拟性能。AD8250基于ADI公司专有技术双极性CMOS工艺的iCMOS技术,它通过在鲁棒的高压数字逻辑电路中集成精密线性器件解决该难题。AD8250允许设计工程师使用软件设置增益。另外,不使用FPGA或微控制器设置增益的设计工程师也可以选择将增益引脚连接到电源电压上,电源电压最高达+15 V。其灵活的增益设置接口允许PGIA用于不同的电路拓扑。

设计工程师面临的第三个难题是将电路固定在更小的PCB板内。AD8250采用10引脚MSOP封装,这种封装面积大约是8引脚SOIC封装的1/2,并且比现有解决方案减少了90%以上。更小的封装面积意味着可以在PCB上放置更多的器件,从而允许设计工程师为其产品增加额外的数据通道。

第四个难题是降低成本。虽然数据采集系统设计工程师的主要目标是提高系统性能,但降低总成本也不容忽视。这些成本包括花费在产品研发上的时间和金钱到维持最终产品中的元器件总数。数据采集设计工程师通过设计可以共享同一平台的数据采集系统以重复利用能够工作的系统器件,从而降低器件成本。通过重复利用已有模块,设计工程师节省了开发时间和成本。AD8250之后还有AD8251(增益为1、2、4或8)和AD8253(增益为1、10、100或1000)两种同系列产品,这有助于解决上述难题。所有这三款产品都引脚兼容。设计工程师可以将AD8250用于需要低增益的产品,而将AD8253用于需要更高增益同时使用相同ADC和逻辑电路的其它产品。它们可以减少器件目录成本并且通过最大程度减少所使用的不同器件数量提高购买能力。

三项主要技术

AD8250采用了三项主要技术。第一项技术是能够达到-110 dB总谐波失真(THD)的失真消除电路。不同于为达到同样级别THD但消耗10mA以上电流的放大器,该器件仅消耗4mA电源电流即可达到该指标。功率节省非常有用,特别对于将许多器件封装在超小面积中而没有风扇制冷的超小PCMCIA数据采集产品。除了低失真外,AD8250能够在615ns内达到16位的分辨率。其20 V/μs的转换率适合于使用多路复用器-切换通道的应用。AD8250通过使用并行端口可在小于375 ns内切换增益。

第二项技术是开关型、内部匹配并且经激光调整的电阻。在过去,设计工程师通过使用外部精密电阻和开关设计他们自己的可设置增益放大器。匹配电阻非常昂贵,每阵列花费15美元以上,但匹配电阻是维持高共模抑制(CMR)和低增益漂移所必需的。用于选择不同增益设置电阻的开关会随着温度的升高而增加误差。此外,开关会产生降低随频率变化的CMR的寄生电容。相比之下,AD8250集成了经激光调整的内部电阻和可以减小开关寄生电容影响的电路拓扑,从而允许其在50kHz内达到90 dB的CMR(G=10)。该技术解决了设计PGIA的难题并且提高了性能。第三项技术改进是精心的设计使这款放大器易于使用。例如,保持带宽在大部分增益(G=1、2或5)内恒定不变。虽然AD8250是一款电压反馈仪表放大器,但其为每种增益使用了传统的内部补偿电容器。因此,设计工程师希望为几种增益维持10MHz的带宽。

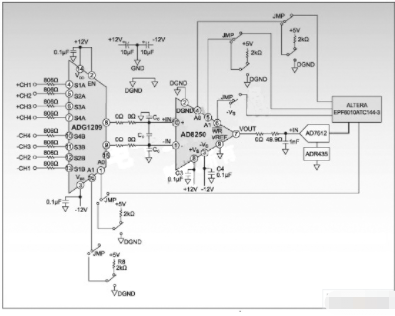

图1:AD825X DAQ演示板的简化原理图。

图1所示是AD825x DAQ演示板中AD8250的电气原理图。这是一个仅使用少量IC的高性能数据采集信号链的设计实例。ADG1209用于为AD8250增加四个差分通道。ADG1209具有低输入电容,从而使其适合于快速多路技术。AD8250可直接驱动AD7612,这是一款750 kSPS采样率的16位ADC。AD7612具有可以采样±10V信号的开关电容输入。相反,如果使用+5V ADC,由于许多工业信号是±10V,则需要降压。ADR435可为AD7612提供参考电压。1 nF的电容器与49.9 ???阻器为AD7612构成反锯齿滤波器。49.9 Ω的串行电阻器可以减小来自放大器1 nF负载的负担并且将其与来自AD7612开关电容器输入影响不好的电流注入隔离。FPGA可控制ADC、PGIA和MUX。请注意所有这三种混合信号器件都基于iCMOS工艺构建。图2所示是使用该演示板调理1kHz信号的软件快速傅立叶变换(FFT)的结果。总谐波失真是-111 dB,信噪比是91 dB。图3所示是AD825X DAQ演示板的图片。

图2:AD825X DAQ演示板对1 kHz信号的快速傅立叶变换结果。

图3:AD825X DAQ演示板照片。

进一步提高集成度、减小尺寸并且实现智能化的市场趋势造就了对AD8250系列的需要。iCMOS等工艺的发展、失真消除电路等电路的改进以及对放大器应该简化使用的理解共同推动了这种可编程增益仪表放大器的发展。

责任编辑:gt

-

AD8250:高性能可编程增益仪表放大器的卓越之选2026-01-16 377

-

PGA855可编程增益仪表放大器技术解析与应用指南2025-08-08 1612

-

AD625:可编程增益仪表放大器数据表2021-04-24 1070

-

AD8231:零漂数字可编程仪表放大器数据表2021-04-20 1065

-

AD8250:10兆赫,20V/μs,G=1,2,5,10CMOS可编程增益仪表放大器数据表2021-04-18 822

-

LTC6915: 具有数字可编程增益的零漂移、精准仪表放大器 数据手册2021-03-21 1198

-

可编程增益放大器在模数接口的应用2019-05-21 2542

-

PGA206/207 高速可编程增益仪表放大器2019-03-20 1760

-

可编程放大器在USB接口数据采集系统中的应用2018-11-22 2385

-

利用仪表放大器获得可编程增益的方法是什么?2018-08-15 7159

-

用于数据采集的超高性能差分输出可编程增益仪表放大器2016-01-04 735

-

AD8250数字可编程仪表放大器简化数据采集系统2011-08-25 1675

-

模数接口中的可编程增益放大器(PGA)2010-09-25 4344

-

可编程增益放大器2008-12-17 1339

全部0条评论

快来发表一下你的评论吧 !