基于TS101S芯片实现雷达信号处理系统的应用设计

描述

数字信号处理就是用一些数学算法对数字信号进行分析、变换、综合、估值和识别。作为数字信号处理核心和标志的数字信号处理器(DSP)芯片自问世以来得到了快速的发展,广泛应用于通信系统、图形/图像处理、雷达声纳、医学信号处理等实时信号处理领域。随着人们对实时信号处理要求的不断提高和大规模集成电路技术的迅速发展,数字信号处理器也发生着日新月异的变革。美国AD公司,继16 b定点ADSP21xx和32 b浮点ADSP21xxx系列之后推出的ADSP Tiger SHARC系列处理器,是基于AD2106x的下一代高性能芯片。本文着重介绍Tig er SHARC系列中TS101S芯片的性能及结构特点,并将其应用在雷达信号处理系统设计中。

1 Tiger SHARC DSP

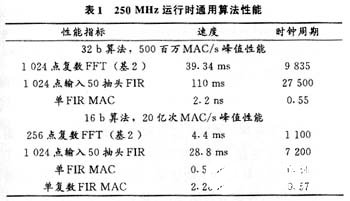

Tiger SHARC DSP是一款高性能的静态超标量数字信号处理器,该处理器专为大的信号处理和通信任务而在结构上进行了优化。由于该处理器将非常宽的存储带宽和双运算模块结合在一起,从而建立了数字信号处理器性能的新标准。Tiger SHARC 静态超标量结构使DSP 每周期能够执行多达4 条指令、24 个16 b定点运算和6个浮点运算。该Tiger SHARC DSP 器件在3条相互独立的128 b宽度的内部数据总线中,每条可连接3个2 Mb 内部存储器 中的1个,并可提供4个字的数据、指令及I/O访问和12 GB/s的内部存储器带宽。运行在250 MHz时,ADSPTS101S 的内核指令周期为4 ns,同时可以提供20亿次 的40 b MAC运算或者500万次80 b MAC运算。

Tiger SHARC DSP器件的主要性能如下:

(1)最高运行速度为300 MHz,指令周期为3.3 ns。

(2)带有6 Mb片内SRAM,分为了3个2 Mb的存储块M0,M1和M2,每一个存储块都能够 单独存储程序、数据或同时存储程序和数据。

(3)带有双运算模块,每个运算块有1个64 b ALU,1个乘法器,1个64 b移位器和1个 由32个寄存器构成的寄存器组,可执行定点和浮点的算术逻辑等通用运算。

(4)3条内部地址/数据总线,每条总线都连接到3个内部存储器块中的1个。3条总线都 是128 b宽,可以在任一周期使用任一条总线传送多达4条指令或4个对齐的数据。这样TS10 1S内核可以在任一周期并行访问3个存储块,1个取指令,2个访问数据。

(5)4个链路口支持点对点的高带宽数据传送,可通过单个链接口以250 Mb/s 的速率进行 数据传输。4个链路口为处理器与处理器之间的通讯提供了一个良好的途径,总吞吐量多达 1 Gb/s。

(6)多处理器特性,当单个DSP芯片组成的系统不能满足处理要求时,TS101S通过外部口或链路口与其他TS101S相连构成多处理器系统。TS101S的外部总线支持多达8个DSP外加Host处理器的并行总线连接。在构成多处理器系统时,处理器之间无论是采用共享总线方式,还是采用链路口互连方式,都不需任何外加控制,实现无缝连接,在并行总线上可以80 0 Mb/s的速率进行数据传输。

(7)有DMA和SDRAM控制器,拥有14个DMA通道,提供了在处理器核不干预条件下的零 开销数据传输,SDRAM的地址、数据引脚可以与Tiger SHARC的直接相连,另外,Tiger SHAR C提供专用的寻址空间支持SDRAM。

TS101S的主要性能指标如表1所示。

2 信号处理系统的实现

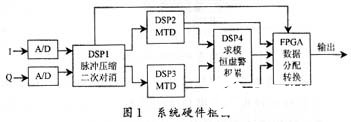

图1所示是一个雷达信号处理系统的硬件框图。为了简化系统硬件,减少DSP片间连线,该系统的4个DSP以松耦合的链路方式进行连接,并共用一片FPGA。

首先由DSP1通过外部DMA方式读入中频解调后的I、Q路数据,并由DSP1对读入数据进行脉冲压缩(匹配滤波),脉冲压缩后进行二次对消,以消除固定杂波。设计总距离单元数为2000,需做2 048点复数FFT,当2 048点复数FFT完成后,还必须和预先存储好的匹配滤波器 系数H(k)相乘,一般需要做2 048个复数乘法,相乘结果还需做2 048点复数IFFT以获得 脉冲压缩结果。Tiger SHARC DSP做2 048点复数FFT和IFFT大约需要200 μs(工作在250 MHz ),利用Tiger SHARC DSP的双运算块和单指令多数据(SIMD)特点同时进行两个距离单元的复 数乘法,完成2 048个复数乘法仅需25 μs。二次对消对于每个距离单元都需要做2次减法和1次加法,2 000个距离单元的二次对消大约需要50 μs。DSP完成上述运算大约要300 μs。

DSP2和DSP3完成动目标检测功能。在使用窄带多谱勒滤波器组时,为了降低旁瓣可在系统 中采用滑窗加权FFT的方法,在距离单元数为2 000时大约需要640 μs处理时间,用2片DSP 并行处理即可实现。

求模采用近似算法,每个距离单元只用做1次比较和1次加法。恒虚警处理先进行选大单 元平均运算,再对被检单元进行比较判决,从而降低

虚警率。积累采用简单累加求平均的方 式完成。以上3种运算由DSP4实现。

FPGA在电路中起辅助作用,在数据量较大的情况下进行数据寄存和分配,同时也能担负DS P4的工作,如果需要的话还能进行数据的并/串转换工作。

3 Tiger SHARC DSP的使用

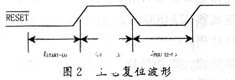

为保证Tiger SHARC DSP能正常工作,上电复位信号的设计非常重要。上电复位波形要求 如图2所示,但应注意tSTARTLO在供电稳定之后必须至少大于1 ms,tPULSE1HI必须大于50个系统时钟周期,同时小于100个系统时钟周期,tPULSE2LO必须大于100个系统时钟周期,在DSP上电后,如需正常复位,其低电平持续时间必须大于100个系统时钟周期。

Tiger SHARC DSP有3个电源,其中数字3.3 V为I/O供电,数字1.2 V为DSP内核供电,模拟1.2 V为内部锁相环和倍频电路供电。Tiger SHARC DSP要求数字3.3 V和1.2 V应同时上电。若无法严格同步,则应保证内核电源1.2 V先上电,I/O电源3.3 V后上电。本系统在数字3.3 V输入端并联了一个大电容,而在数字1.2 V输入端并联了一个小电容,其目的就是为了保证3.3 V充电时间大于1.2 V充电时间,以便很好地解决电源供电的先后问题。

Tiger SHARC DSP内核最大电流为1.277 A,该电流是DSP进行单指令多数据(SIMD) 方式下,4个16 b定点字乘加与2个4字读取并行操作以及进行由外部口到内部存储器DMA操作所需的电流。实际上,DSP 内核电流大小还和内核工作频率有关,因此,供给DSP 内核电流可根据不同的并行处理任务和内核工作频率来确定,最大内核功耗为1.534 W。外部口的功耗(对VDDIO)主要是输出引脚(例如数据线的某个位由高到低,或由低到高)转换的功 率消耗,而且该功耗与系统无关,一般为0.45 W。由此可估算出该信号处理系统的功耗大 约为10 W。

4 结语

本文介绍了多片Tiger SHARC DSP在雷达信号处理系统中的应用,该系统充分利用了TS101 S高速的运算能力及数据吞吐量,对不同的距离单元段进行并行处理。文中分析了系统的运 算量、所需时间以及完成算法所需的DSP数,并且讨论了DSP应用过程中需注意的几个问题, 具有很强的实用性。该系统外接计算机总线,预留链路口,按信号处理通用板的模式设计, 也就是说,当单板资源不够时,通过增加板子的数量就可成倍地增加信号处理能力,这对于 各种新型号雷达的开发研制起到了事半功倍的作用,大大缩短了研发周期,具有广泛的 应用价值。

责任编辑:gt

-

哪位有ADSP TS101S 芯片的Cadence原理图封装啊 跪求 ..2015-03-14 2918

-

一种基于TS101的SAR回波信号模拟器设计2019-07-22 1509

-

如何采用ADSP-TS101实现高速信号处理系统的设计?2021-04-12 1046

-

ICS554在软件高频雷达上的接口实现2009-12-16 570

-

基于ADSP-TS101S的多芯片数字信号处理系统的实现方案2006-03-11 1326

-

采用ADSP-TS201S芯片的图像采集处理系统设计2009-03-30 1508

-

多片TS101S的加载引导设计分析及实现2010-03-31 1873

-

一种雷达组网融合实时处理系统设计与实现2011-10-09 540

-

基于TS101的图像采集和处理系统设计2011-10-11 1144

-

雷达通用信号处理系统的实现与应用2011-12-15 1052

-

基于FPGA的雷达信号处理系统设计2015-10-30 1138

-

地面脉冲多普勒雷达信号处理系统方案2016-12-26 931

-

采用FPGA与高性能DSP芯片的雷达信号处理系统设计2018-10-14 3230

-

激光雷达信号处理系统2021-11-24 3413

-

深度解析ADSP - TS101S TigerSHARC嵌入式处理器2026-03-24 244

全部0条评论

快来发表一下你的评论吧 !