物理可级联的LUT的优势在哪?

描述

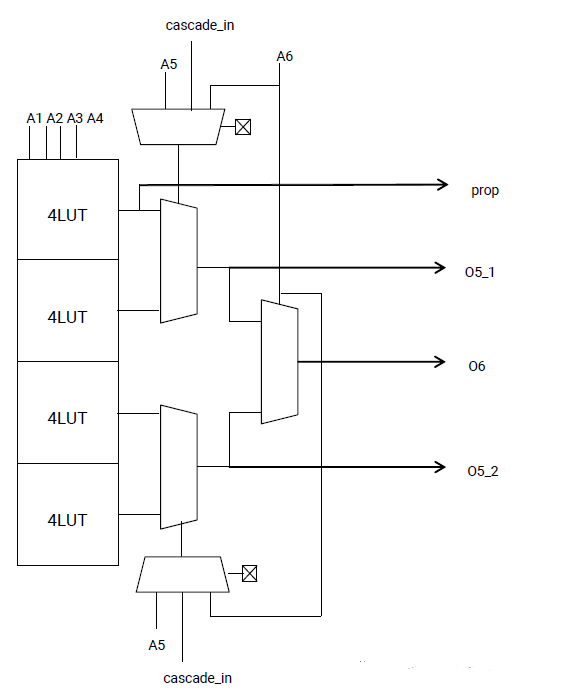

在Versal ACAP中,同一个CLB内同一列的LUT是可以级联的,这是与前一代FPGA UltraScale+系列的一个显著不同点。这里我们先看看Versal中LUT的结构,如下图所示(图片来源:Figure4, am005)。

可以看到,一个LUT6(6输入LUT)是由4个LUT4(4输入LUT)外加一些MUX(数据选择器)共同构成。同时,LUT6有4个输出端口。其中,prop端口只有在LUT用作进位逻辑时使用,且在CLB外部不可见。用做6个输入的逻辑函数发生器时,输出在O6端口;双LUT5模式时,输出在O5_1和O5_2端口。同时还可以注意到,多了一个级联端口cascade_in,该端口用于与前一级LUT的O6输出相连接。级联端口不需要手工连接,工具会自动判断是否使用该端口。

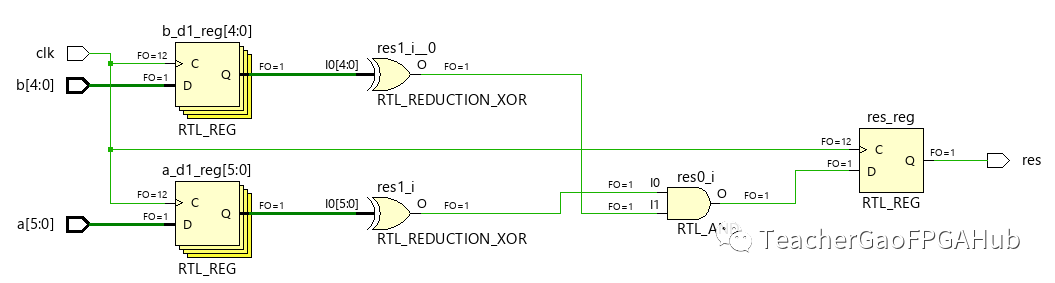

我们看一个具体的案例,如下图所示。输入a为6bits,b为5bits,a/b分别执行异或位缩减运算(^a,^b),然后再将两者结果执行逻辑与。显然a的异或位缩减运算会占用一个LUT6,b的异或位缩减运算与后续的与门共同消耗一个LUT6。

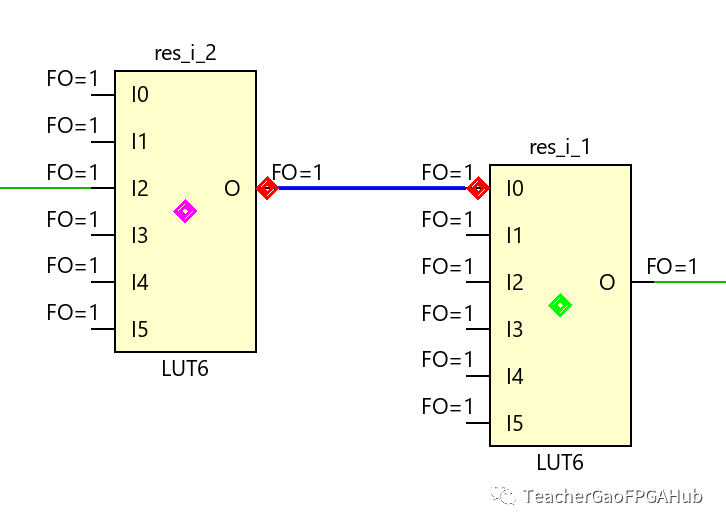

上述电路图布线后打开Schematic视图,锁定其中的两个LUT6,如下图所示。

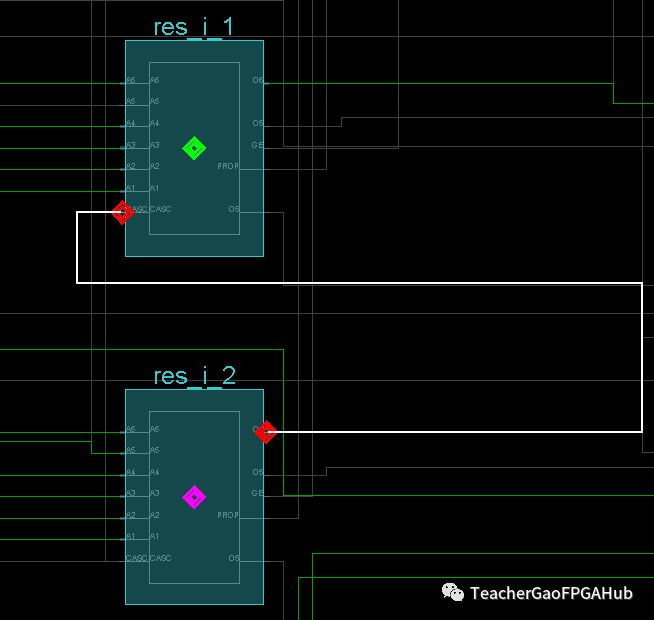

进一步在Device视图中可以看到具体的物理连接方式,如下图所示。可以看到图片下方的LUT由O6输出,并连接到上方LUT的级联端口。

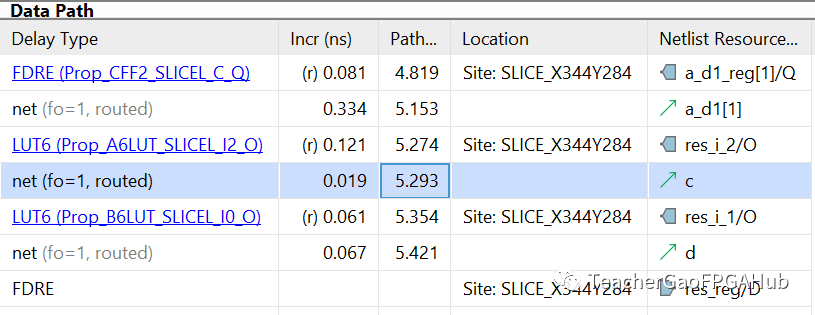

再从时序角度看,这里我们设定时钟频率为600M,在时序报告中,可以看到这部分的延迟(两个LUT之间的布线延迟)为0.019ns。整个设计的WNS为0.923ns。

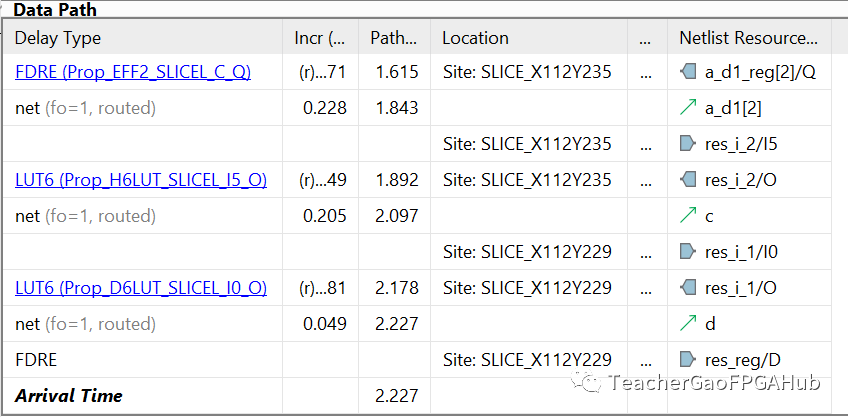

同样的设计,如果在UltraScale+中执行,结果如下图所示,可以看到两个LUT相距很远,因为UltraScale+中的LUT是不支持级联的,这就要消耗CLB外部的布线资源。

从时序角度看,这部分的延迟为0.205ns,显然大了很多。

综上所示,我们可以得出如下结论:

LUT的级联可以有效降低关键路径上的延迟,同时减少CLB外部布线资源的消耗。这对于缓解布线拥塞非常有利。还要注意的是这种级联仅限于同一个CLB中的同一列LUT,且级联方向由下至上,这意味着级联所用到的布线资源都在CLB内部,而不会消耗CLB外部布线资源。

编辑:jq

-

labview相比matlab优势在哪?2011-07-17 5627

-

【求资料或回答】quartus的LUT的使用方法2016-06-17 4834

-

FPGA中LUT设计2018-07-30 3498

-

Virtex-6 FPGA上的可重配置LUT无法打包2018-10-22 2974

-

使用的LUT触发器对的数量与Slice Register和Slice LUT的关系是什么?2018-10-23 12339

-

在FPGA设计中如何用LUT组建分布式的RAM2021-07-28 1523

-

什么是MGTs?MGTs的优势在哪里?2021-09-30 2758

-

在哪里可以找到qspiflash_config.memConfig.lookupTable中序列到FLEXSPI中LUT的映射?2023-05-17 670

-

可级联FIR滤波器的IP设计及FPGA验证2009-05-11 1320

-

MAX11040K可级联ADC中文资料2012-10-17 980

-

如何利用LUT来实现FPGA中的DSP功能2018-07-02 13662

-

LUT内容用编程语言修改的应用教程2017-11-25 10455

-

基于电网拓扑结构和物理特性的连续级联故障仿真模型2018-01-17 1012

-

LUT如何构成逻辑函数2018-10-26 11491

-

FPGA——LUT/FDRE/FDCE/FDSE/FDPE2022-11-09 3867

全部0条评论

快来发表一下你的评论吧 !