三星计划斥资1,160亿美元用于其下一代芯片业

描述

据报道,三星计划斥资1,160亿美元用于其下一代芯片业务,其中包括为外部客户制造芯片代工业务,以期在2022年之前缩小与行业领导者台积电的差距。

三星的策略是双重的:

1.2022年下半年将量产3nm芯片,以与台积电匹配。

2.如图1所示,采用更先进的全能栅极(GAA)技术代替TSMC的FinFET结构。

图1资料来源:三星

GAA在晶体管性能控制方面具有显着优势,因为它可以更精确地控制流经沟道的电流,缩小芯片面积并降低功耗。

与FinFETs不同,在FinFETs中,更高的电流需要多个并排的鳍片,而GAA晶体管的载流能力通过垂直堆叠数个纳米片,栅极材料包裹在沟道周围而增加。

三星声称,与7nm技术相比,其GAA工艺将能够使芯片面积减少45%,功耗降低50%,从而使整体性能提高35%。

在IEEE国际固态电路会议(ISSCC)上,三星工程师分享了即将推出的3nm GAE MBCFET芯片的制造细节。三星表示,传统的GAAFET工艺使用三层纳米线构造晶体管,并且栅极相对较薄。此外,三星MBCFET芯片工艺使用纳米片构造晶体管。目前,三星已经为MBCFET注册了商标。三星表示,这两种方法都可以达到3nm。

在本文中,我从技术,产能和资本支出重点探讨了三星公司目前和未来的能力(三星存储部门除外),以及三星是否确实能够缩小7纳米以下节点的差距。

三星3纳米芯片的更多细节

三星晶圆厂将成为第一家在即将到来的3nm工艺中使用类似全栅场效应晶体管(GAAFET)结构的半导体制造商。虽然该节点尚未准备就绪,但在IEEE国际固态电路会议(ISSCC)上,三星晶圆厂的工程师分享了有关即将推出的3 nm GAE MBCFET(multi-bridge channel FET)制造技术的一些细节。

据介绍,有两种类型的GAAFET:典型的GAAFET,这被称为具有“薄”鳍的纳米线。以及MBCFET,称为具有“厚”鳍的纳米片。在两种情况下,栅极材料在所有侧面上都围绕沟道区。纳米线和纳米片的实际实现方式在很大程度上取决于设计,因此,一般而言,许多行业观察家用术语GAAFET来描述两者。但是以前它们被称为环绕栅晶体管(surrounding-gate transistors :SGT)。值得一提的是,MBCFET是 三星的 商标。

图片来源:三星 1988年,全球首次展示了GAAFET,因此该技术的关键优势众所周知。这种晶体管的结构使得设计人员可以通过调节晶体管通道的宽度(也称为有效宽度或Weff)来精确地对其进行调谐,以实现高性能或低功耗。较宽的薄片(sheets)可以在更高的功率下实现更高的性能,而较薄/较窄的薄片可以降低功耗和性能。为了对FinFET做类似的事情,工程师必须使用额外的鳍来改善性能。但是在这种情况下,晶体管沟道的“宽度”只能增加一倍或两倍,这并不是很精确,有时效率很低。另外,由于不同的晶体管可以用于不同的目的,因此通过调整GAAFET可以提高晶体管的密度。

图片来源:三星 早在2019年,三星推出的的3GAE工艺设计套件版本0.1就包括四种不同的纳米片宽度,以为早期采用者提供一定的灵活性,尽管目前尚不清楚该公司是否增加了宽度以提供额外的灵活性。但是三星表示,总的来说,与7LPP技术相比,其3GAE节点将使性能提高30%(在相同的功率和复杂度下),功耗降低50%(在相同的时钟和复杂度下),并且晶体管密度提高了80%(包括逻辑和SRAM晶体管的混合)。

图片来源:三星 三星的3GAE(其第一代MBCFET技术)将于2022年推出。虽然三星目前尚未披露其所有特性。但该公司在ISSCC上讨论了如何使用新型晶体管来提高SRAM性能和可扩展性。 近年来,SRAM的可扩展性一直落后于逻辑的可扩展性。同时,现代片上系统将SRAM的负载用于各种高速缓存,因此提高其可伸缩性是一项至关重要的任务。

图片来源:三星 据《EE Times》亚洲报道,三星代工厂在ISSCC上介绍了其256Mb MBCFET SRAM芯片,该芯片的尺寸为56mm2 。这意味着尽管该公司尚未推出其首款3GAE逻辑芯片,但显然该技术适用于SRAM。 SRAM是一个六晶体管存储单元:两个传输门(pass gates),两个上拉和两个下拉。在FinFET设计中,SRAM单元将使用具有相同沟道宽度的相同晶体管。借助MBCFET,三星可以调整沟道宽度,因此提出了两种方案:在一种情况下,三星将沟道更宽的晶体管用于传输门和下拉电路,而在另一种情况下,三星将使用具有较宽沟道的晶体管用于传输门和晶体管。 至于较窄的下拉通道。三星通过IEEE Spectrum称,通过将具有更宽沟道的晶体管用于传输门,并将具有较窄通道的晶体管用于上拉,与常规的SRAM单元相比,三星设法将写入电压降低了230 mV 。

三星与台积电的支出和产能

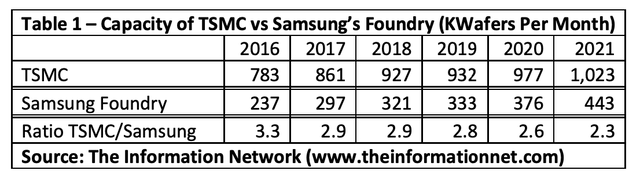

三星是否有能力在台积电主导的市场中占据重要份额?这是一个很复杂的问题。因为台积电本身在2021年花费了创纪录的250亿美元,以确保它保持在技术和产能的前列。 表1列出了台积电和三星晶圆代工部门所有节点的总产能。从积极的一面来看,台积电的产能比例从2016年的3.3倍降至2021的2.3倍。

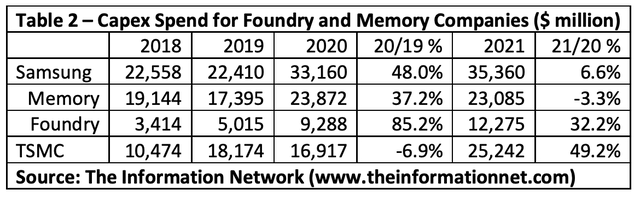

表1中的数据显示,台积电在产能方面远远领先于三星,但价差略有下降。原因之一是三星的资本支出增加,如表2所示,该公司在2020年的制造资本支出同比增长了85%,并计划在2021年进一步增长32%。相比之下。台积电在2020年的资本支出变化为-7%,但在2021年将增长49%。

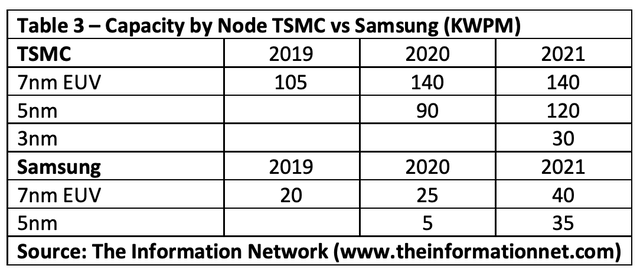

表3显示了7TSMC和Samsung在7nm以下节点的产能对比。在2019年和2020年,台积电在7nm节点的产能大约增加了5-6倍,到2021年的预测是3.5倍。在5纳米节点,台积电的产能大约增加了四倍。

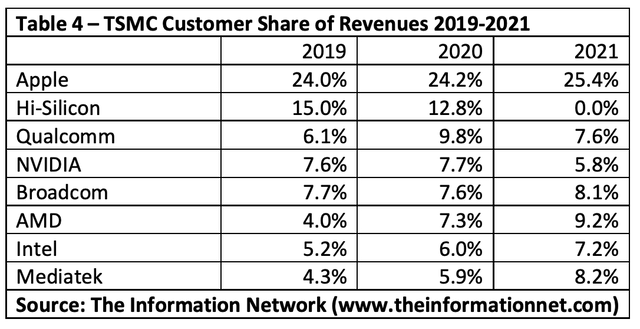

为了弥补5nm和3nm的有限产能,三星正推进先进的逻辑体系结构,我之前已经讨论过,请读者参考图1。 台积电拥有460多个客户,其领先的客户名单包括苹果,博通,海思半导体,AMD,联发科,NVIDIA,高通和英特尔等顶级无晶园公司和IDM。 表4显示了这些公司及其在2019-2021年台积电收入中所占的百分比。

至于三星,将其客户群与台积电进行比较有点误导。2020年,三星将其晶圆代工厂产的60%用于内部使用,主要用于智能手机的Exynos芯片。其余产能来自非专属客户,高通(20%),其余20%来自Nvidia,IBM和英特尔。随着三星在2021年增加其低于7纳米的产量,自用产能占比将降低,可能降至50%。

三星和台积电争霸战开打

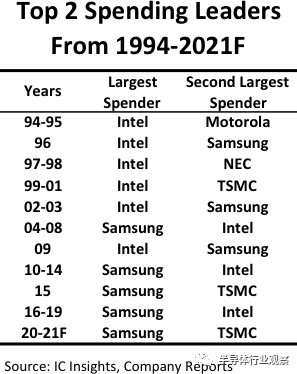

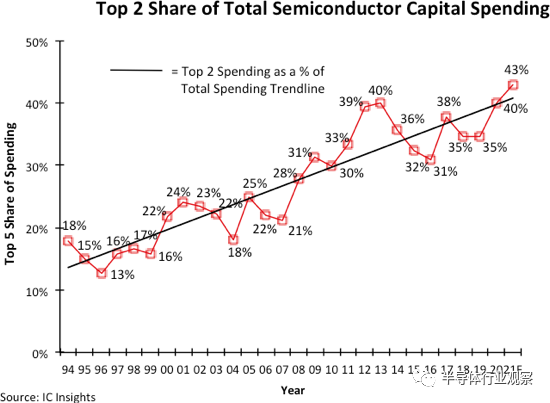

据分析机构ICinsights报道,在过去的25年中,跟上前沿IC技术的发展步伐变得越来越昂贵。现在,为逻辑器件实施最先进的工艺技术所需的投资已将大部分公司已经赶出了市场,仅剩下三星,台积电和英特尔这三家公司。而在这三家制造商中,只有两家可以真正地处于领先地位,那就是三星和台积电。 从现状看来,他们都可以批量生产7nm和5nm IC。相比之下,预计直到2022年,英特尔都不会在自己的制造工厂中大批量生产7nm器件,而届时三星和台积电预计已经推出3nm制程技术生产商业量的IC。 从历史上看,具有最高资本支出水平的IC公司也是能够生产最先进芯片的公司。尽管在过去27年中,英特尔已连续25年位居半导体行业前两大资本支出者之列(图2),但该公司在2020年的支出仅是三星当年支出的一半左右,而且预计将再次远低于三星支出的一半。三星和台积电预计今年将各自支出约280亿美元。 在2010年,三星的半导体资本支出花费首次超过了100亿美元。在2016年,公司在半导体资本支出上花费了113亿美元,然后在2017年,三星半导体集团的支出增加了一倍以上,达到242亿美元。 自2017年以来,三星的半导体资本支出一直非常强劲,2018年的支出更是达到惊人的216亿美元,2019年达到193亿美元,去年达到281亿美元。 在半导体行业的历史上,三星在2017-2020年期间的庞大支出(932亿尽管三星尚未为其2021年的支出提供指导,但IC Insights估计该公司的支出将基本与2020年持平。

图2 台积电是唯一提供领先技术的纯晶圆代工厂。它对7纳米和5纳米工艺的需求非常强劲,这些工艺占其2H20销售额的47%。它目前的大部分投资都针对其7nm和5nm技术的额外产能。 台积电的5nm产品占到2020年总销售额的8%(35亿美元),由此可以说明去年台积电转向了更先进的工艺有多快,因为该公司在去年上半年基本上没有5nm收入。 现在看来,三星和台积电都意识到了眼前的千载难逢的机遇。 三星在2017年开始支出激增,台积电也将在2021年开始大规模的多年支出增长。ICInsights预计,三星和台积电今年的资本支出将至少达到555亿美元,占总支出的5%。前两个支出最多的时间是半导体行业总支出中的高百分比(图3)。 由于目前尚无其他公司能够与这些庞大的支出相匹敌,因此三星和台积电今年可能会在先进集成电路制造技术方面与自身和竞争对手展开更大的距离。

图3 像欧盟,美国和中国这样的政府能否投资于其本土IC产业并赶上与三星和台积电(TSMC)的IC技术竞赛? 考虑到差距还很大,IC Insights认为,各国政府至少需要在至少五年内每年花费至少300亿美元,才能获得合理的成功机会。他们是否有意愿和/或能力兑现这一承诺? 此外,对中国而言,即使有钱,也肯定会受到贸易问题的阻碍,因为贸易问题禁止一些最关键的过程设备出售到中国。 如果没有其他IC生产商或政府采取迅速而果断的行动,三星和台积电就将成功占领世界领先的IC工艺技术,这是未来先进的消费,商业和军事电子系统的基石。

总结

三星比台积电落后一代,后者预计将保持5nm和3nm的领先地位。 EUV系统的不足是台积电在三星方面领先一代的催化剂。到2020年,三星电子总共购买了25台EUV光刻系统,而台积电则购买了约50台。 在短期内,有几个缓解因素将保持这一差距:

ASML的生产限制为每年约50个EUV系统

ASML还有其他要分配系统的客户,包括SK海力士,英特尔,美光科技和可能的中芯国际

三星还必须分配资本支出用于其DRAM部门的EUV购买

由于三星不是台积电(TSMC)这样的纯晶圆代工厂,其7纳米以下的产量中至少有50%被分配给其智能手机内部使用,这将限制其客户群,因为其产能增长将因缺乏EUV而受到阻碍系统。 三星将通过过渡到3nm的GAA和MBCFET等高级逻辑架构,逐步缩小技术差距。GAA的功耗降低了50%,整体性能提高了35%,这将推动客户向三星迁移,只要有可用的容量。但是产能缺口仍将存在。

责任编辑:lq

-

三星半导体发展面临巨大挑战2012-09-21 0

-

三星手机RFID读取芯片2019-07-04 0

-

三星电子斥资19亿美元新建逻辑芯片生产线2012-06-08 573

-

三星将投资19亿美元开发下一代芯片2012-06-08 689

-

解析三星为什么可以赶超Intel成为芯片业老大2017-12-28 2197

-

三星芯片业务营收690亿美元 正式超越Intel成新王者2018-01-31 1017

-

三星的下一代芯片将重点放在AI和5G技术上2019-07-27 3821

-

三星为发展模拟芯片而投资1150亿美元2019-08-16 592

-

三星计划投资110亿美元推动下一代显示器的开发2019-10-10 3045

-

三星电子宣布大规模长期投资计划 金额达1160亿美元2019-12-25 2694

-

谷歌与三星和好了?下一代Pixel手机或用三星5nm处理器2020-04-13 3738

-

三星电子奋力赶超台积电,计划在2022 年量产 3 纳米芯片2020-11-19 1616

-

三星下一代SoC或搭载AMD GPU2021-01-14 2047

-

斥资100亿美元!三星计划在美国建立3纳米芯片工厂 追赶台积电2021-01-23 4679

-

三星成功拿下特斯拉下一代FSD芯片订单2023-07-19 739

全部0条评论

快来发表一下你的评论吧 !