教你们怎么去设定寄存器的初始值

描述

对于寄存器,如果没有明确指定其初始值,Vivado会根据其类型(FDCE/FDRE/FDPE/FDRE)设定合适的初始值。有些工程师喜欢使用复位信号,对所有的寄存器进行上电复位,使其在处理数据之前达到期望初始状态。但这会有一个不利之处就是复位信号的扇出很大,从而消耗了大量的布线资源,甚至造成布线拥塞。那么能不能让寄存器在上电之后不用通过复位就输出期望值呢?答案是肯定的。

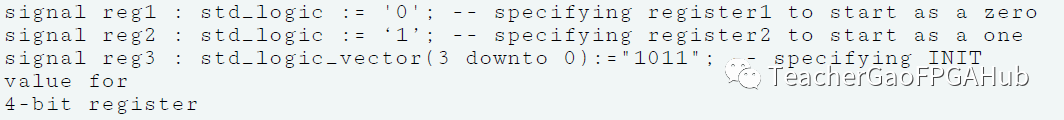

Xilinx也建议对于同步元件,最好设定其初始值。这里我们以最常用的寄存器为例。如果使用的是VHDL,可以采用下面的方法设定寄存器初始值,如下图所示。

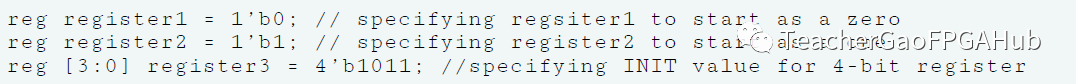

如果使用的是Verilog,可以采用下面的方法设定寄存器初始值,如下图所示。

此外,对于Verilog,也可通过initial设定初始值,如下图所示。

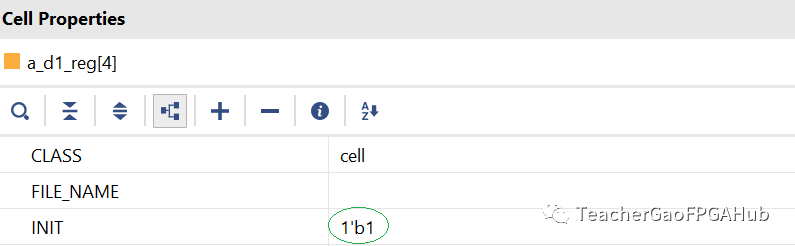

采用这种方法的好处是:综合工具是支持的,这样生成bit文件时这些初始值会被写入配置文件中,上电即可生效,避免了使用复位造成的扇出过大;同时在仿真时,也能跟实际业务相匹配。 为了验证这个方法是否生效,只需要打开综合后的.dcp,找到相应的寄存器,在其Property窗口中查看属性INIT的值,如下图所示。

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

智能显示模块怎么在显示工程中给寄存器设置初始值?我想给变量一个上电的默认值该如何设置?2025-12-06 634

-

AFE4404没有接外部时钟,4404寄存器的为初始值,能够通过IIC修改寄存器值吗?2024-12-06 385

-

详解寄存器模型镜像值2024-10-23 2465

-

如何理解 RAMECC FAR 寄存器的值2023-10-19 1505

-

Cortex-M3寄存器等基础知识2022-02-08 901

-

寄存器与静态库2022-01-13 853

-

stm32是如何将寄存器值通过标准库写入寄存器的?2021-12-16 1253

-

定时器的初始值要怎么设定2021-12-01 1652

-

由RAM上电后初始值引起的问题2021-04-28 1126

-

Labview while循环移位寄存器运行中初始化数值为初始值2019-04-20 6291

-

K60的FTM寄存器详细资料说明2019-03-26 1263

-

抑制初始值的警告2019-02-25 2634

-

Virtex6怎么配置寄存器初始值2018-10-26 2333

-

换路定律及初始值的确定2009-05-10 4956

全部0条评论

快来发表一下你的评论吧 !