FPGA、Zynq和Zynq MPSoC三种器件的特点介绍

描述

FPGAs,Zynq 和 Zynq MPSoC!

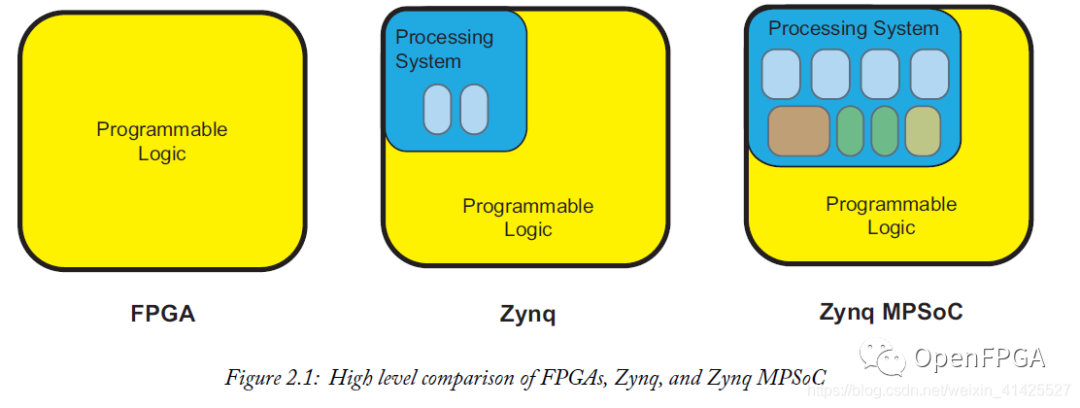

Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点。

2.1 技术时间线

进一步介绍之前,需要指出这三种产品都有各自的优势,在选择时,并不是越贵越好,而是最适合我们设计的选择才是最好的选择。这三种产品都有自己在成本,性能等方面最好的平衡,这使其可适用于不同的任务和应用。

因为大多数读者比较熟悉Zynq,因此我们从它开始介绍,以方便后面我们将Zynq MPSoC与其进行对比。因为FPGA 是所有SoC产品的PL部分,因此,我们稍后再做介绍。

2.2 Zynq-7000 SoC

Zynq-7000 SoC是Xilinx发布的第一款SoC器件。集成了基于FPGA的PL部分和基于Arm的PS部分。这里只对其做简单介绍。更详细介绍可参考[The Zynq Book](http://www.zynqbook.com/)该书已出中文版。

2.2.1 Zynq架构特征

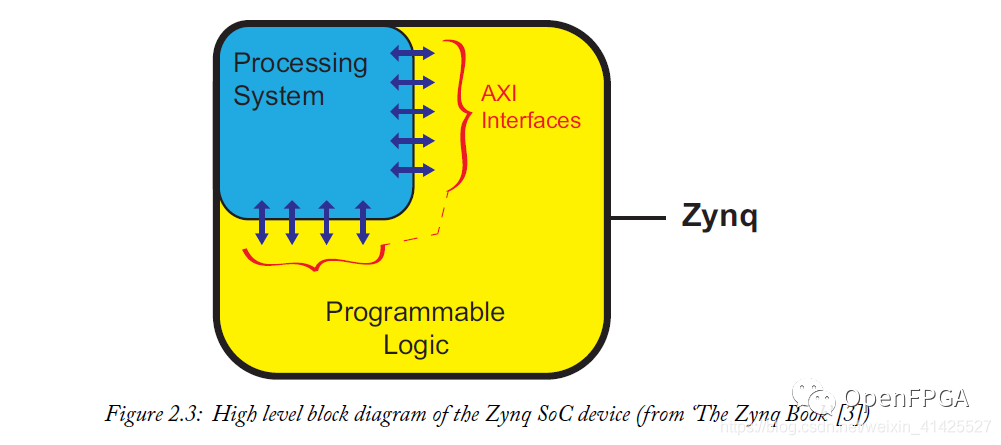

从高层次的角度去看,Zynq架构包含PS和PL两部分以及之间的互连线。如图2.3所示。互联遵循AXI标准,AXI标准是Arm开发的片上通信技术标准。

将PS和PL集成到一起一方面能够为运行嵌入式系统中的基于软件的部分提供专用的优化的资源(我的理解是适合运行于处理器的部分),另一方面能够发挥FPGA的优势(尤其时其并行性和可配置能力)。AXI接口来连接这两个不放呢,AXI是专为SoC应用优化的一个接口标准。

图2.3中并不是按尺寸比例画的,对于不同的Zynq器件,他们有相同的PS架构,但是PL部分的尺寸不同。而对于Zynq和Zynq MPSoC,其PS和PL部分都是不同的。

Zynq PS部分

如图2.3的蓝色部分,是一个应用级的处理器以及相关元件。如下所示:

应用处理单元Application Processor Unit (APU) -这部分包括一个双核 Arm Cortex-A9处理器,以及256KB的片上缓存。

互连线和存储接口 -用来进行PL和PS通信以及与各自的片外存储单元通信

I/O外设 -一系列集成的外设接口,包括一些常用的标准例如 USB,UART,SPI,I2C等

Zynq的PS部分包含两个处理核,这使得设计人员可以在两个核上运行相同操作系统,或者每个核运行一个不同的操作系统。后面我们会对比Zynq核Zynq MPSoC的PS架构,并说明新器件增加的一些功能,实际上,Zynq MPSoC具有6个处理核。

最近(应该是2019年),一个轻量级的Zynq版本,Zynq-7000S发布,该版本PS只包含一个Cortex-A9的处理器。

Zynq PL部分

Zynq的PL部分是基于Xilinx的FPGA器件的,其PL部分所对应的器件性能决定PL性能,包括Xilinx的Artix-7,Kintex-7以及Virtex-7系列器件。像这些FPGA一样,其PL部分包含DSP48x slices(高速计算资源),Block RAMs,高速收发器件,以及集成的通信模块。以及通用逻辑。2.4.3节对现代FPGA的这些模块进行进一步介绍。

Zynq PS与PL部分接口

Zynq的PL和PS部分有9个接口,包括4个“通用目的接口”,四个“高性能”接口,以及1个用来PS中APU和PL通信的“加速一致性”接口。

2.2.2 Zynq器件

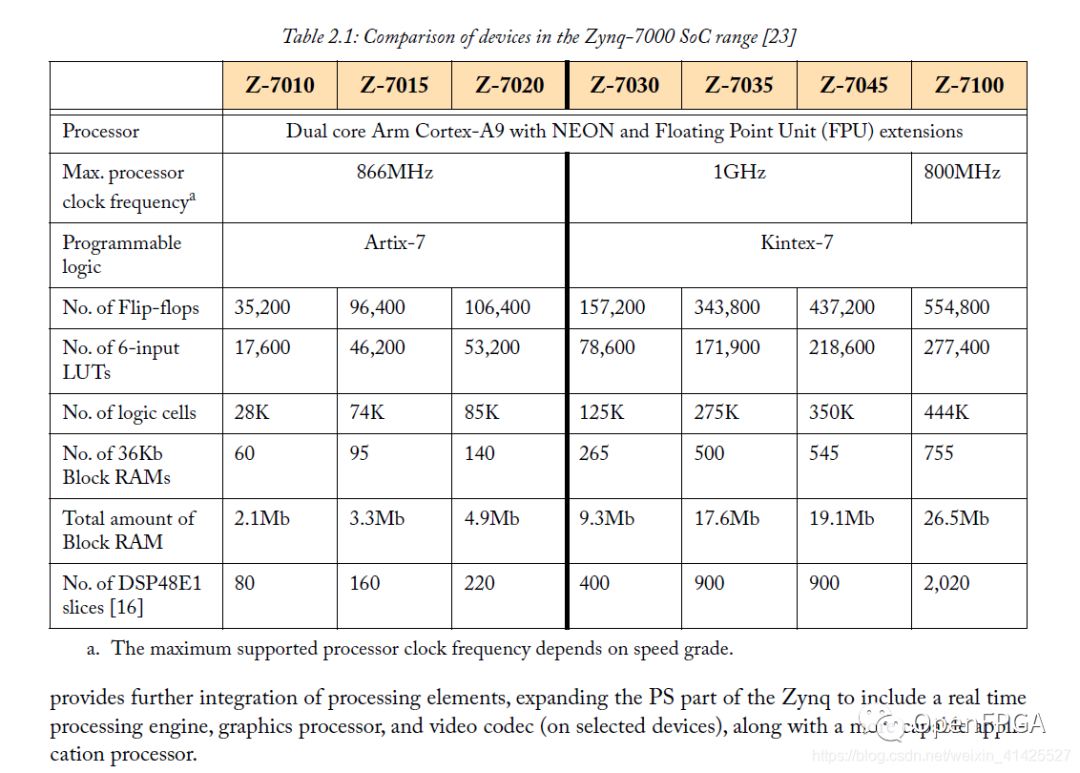

表2.1对Zynq-7000系列器件的关键特征和参数进行了对比(注意这里并没有给出单核的Zynq-7000S系列对比,可查看Zynq-7000 SoC Data Sheet: Overview文档)。

对于列出Zynq-7000系列器件,除了支持的最大时钟频率其PS部分是没有区别的。而其PL部分与其所基于的FPGA型号相似,例如基于Artix-7的PL部分与Artix-7资源类似。不同型号的PL部分在DSP slices,Block RAM以及输入输出资源上有所区别。

2.3 Xilinx Zynq MPSoC

Zynq MPSoC是Zynq的进阶版本,其PS部分更加复杂,PL部分也由Xilinx7系列升级到UltraScale+ FPGA架构,对于大多数Zynq MPSoC器件,其PL部分的资源和面积要比Zynq系列要多。

2.3.1 Zynq MPSoC发布

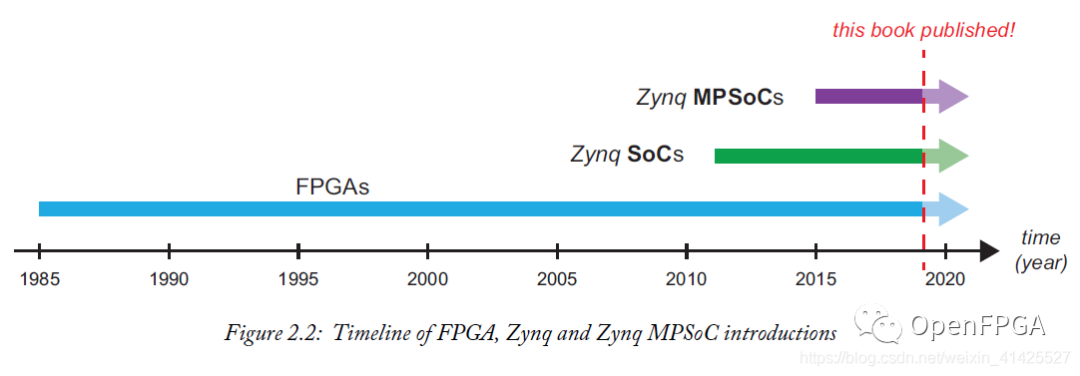

Zynq MPSoC是在Zynq发布四年之后的2015年发布的。在这四年期间,Zynq在应用于了很多领域,因此诞生了“FPGA+processor”的需求。

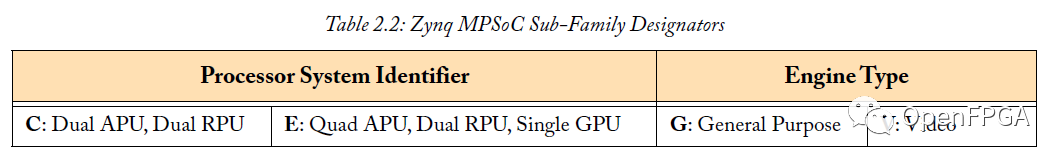

Zynq MPSoC提供了加强版的PS以及更多资源和面积的PL.包含不同子系列以满足不同应用的需求,其不同主要体现在PS资源上。三个子系列分别由两个大写字母表示,分别为CG系列,EG系列以及EV系列,这两个字母的意思如表2.2所示。

Zynq MPSoC并不是Zynq的替代品,只是以相同的形式提供了一个扩展增强的解决方案。Zynq对于更适用相对来说低消耗和稍微简单的系统。

2.3.2 Zynq MPSoC架构及其特点

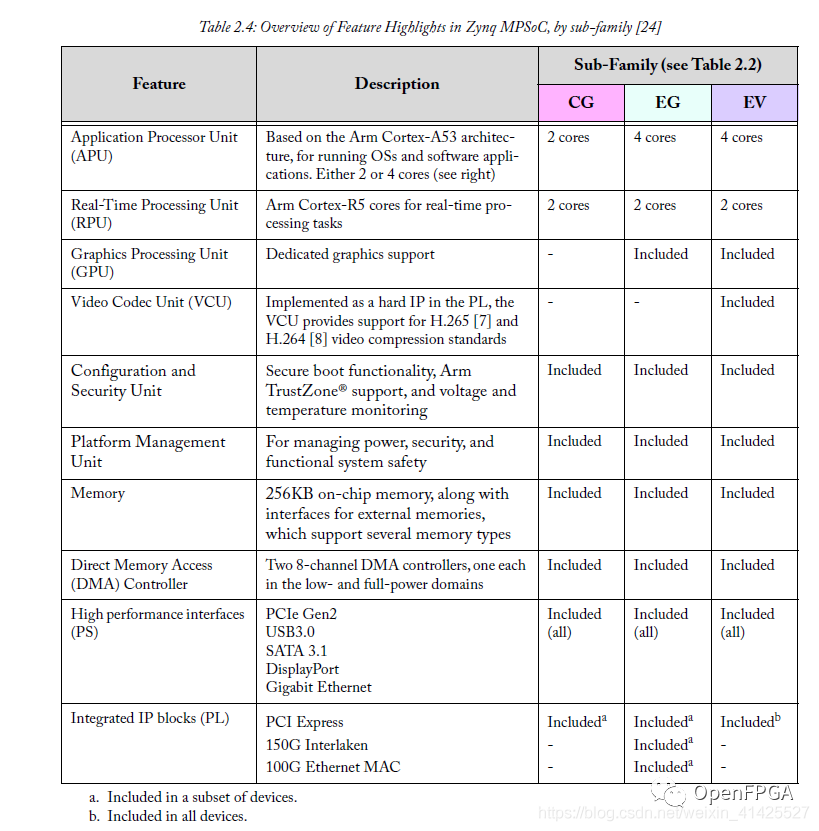

Zynq MPSoC的三个子系列PS和PL部分资源如表2.4,在后面几章本书会详细介绍这些特点。

Zynq MPSoC架构的另外一个重要特点是其电源管理能力。该器件被分为四个电源区域,可以被单独控制,这意味着可以给闲置部分断电(power down),提高电源效率。另外,Zynq MPSoC架构的安全方面也得到了进一步加强。

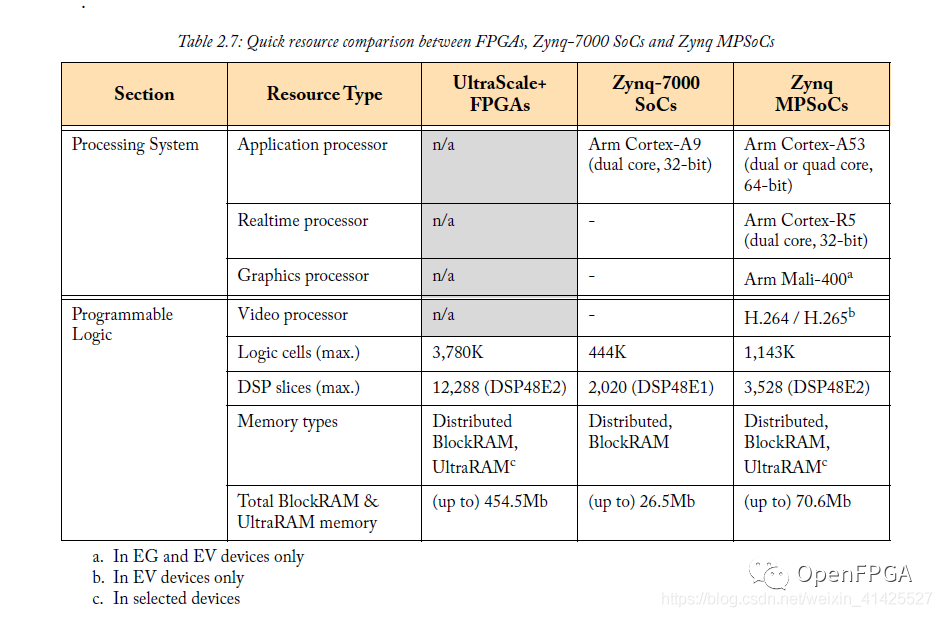

额外需要强调的是, Zynq MPSoC架构PL部分所采用的UltraScale+ FPGA架构(2.4.3节讨论)相对于Zynq所采用的7系列也有很大增强。两个非常重要的特征是其包含了UltraRAM以及DSP由DSP48E1发展为DSP48E2。

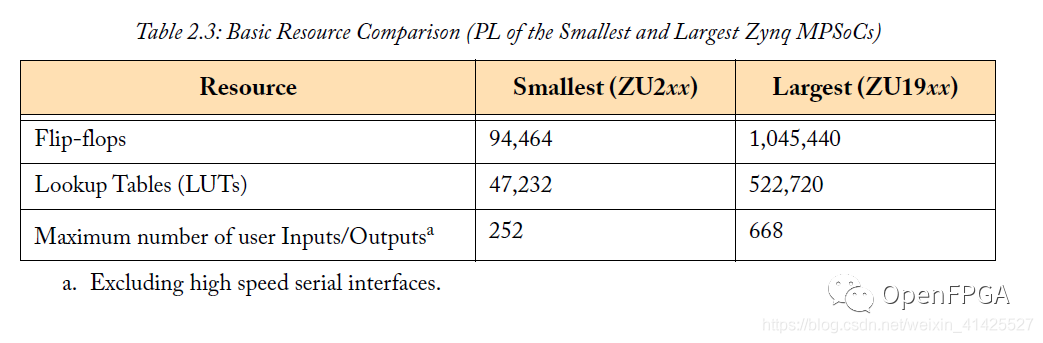

该器件系列的PL部分对于不同型号资源也不同,表2.3给出了最少和最多资源的情况,与Zynq的PL部分(表2.1)相比,Zynq MPSoC具有更多的资源,适合开发对PL资源要求更高的加速应用。

2.4 FPGA

FPGA是以上两种器件PL部分的基础,也是最早出现的器件。因此我们对其发展进行回顾,接着介绍一些应用,最后介绍现代FPGA技术的架构和特征。

2.4.1 什么是FPGA

(FPGA介绍资料较多这不再赘述及翻译)

2.4.2 FPGA发展

Xilinx的FPGA架构从最开始的只有64个触发器和3输入查找表(LUT实现逻辑功能)。随着FPGA技术的发展,其面积不断增大,逻辑资源不断增加。其架构也在发展,,功耗不断降低,越来越能够用于更高的频率。而且大量的专用资源例如高速存储器,计算模块,时钟和互联也在不断发展。

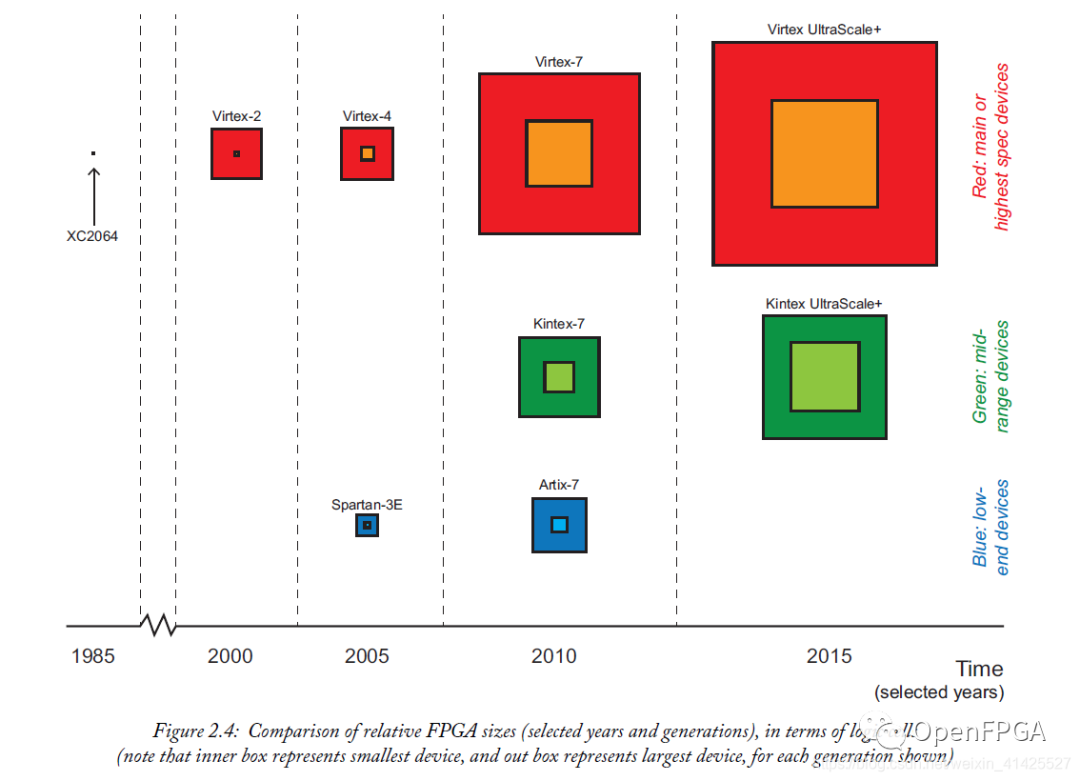

从FPGA的规模来看,用“逻辑单元(logic cells)”来度量逻辑密度,我们从稍微抽象的较低层次考虑体系结构之间的差异。图2.4.张图总结了FPGA在“逻辑单元”方面的发展。以5年为一个时间节点展示了过去15年来发展。并将其与第一块FPGA(1985年发布)对比,可以看到,如今的FPGA即使相对于过去10年的发展已经相当大,更不用是更早期的FPGA。可以看到,第一块FPGA在图中左侧只能用一个点来表示。另外,今年,也有一些比较先进但相对低端的设备可供需求不高的开发者选择。大框中的小框代表该系列较低端的器件。

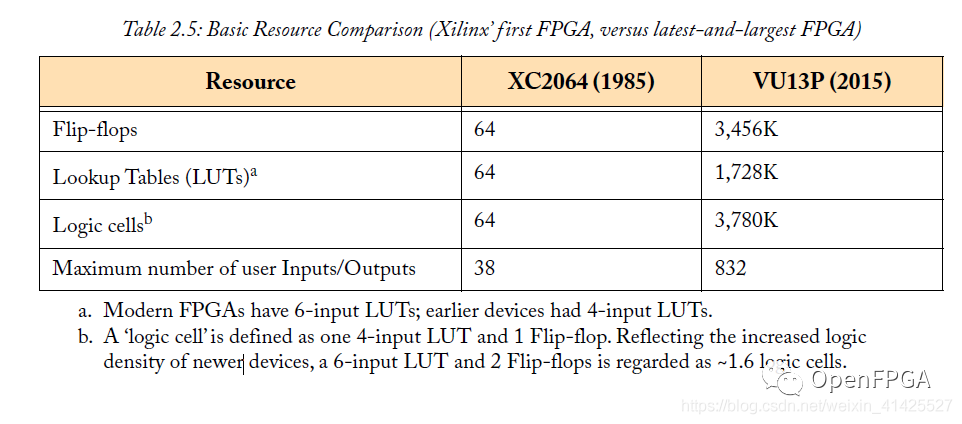

仅从逻辑单元方面对比,表2.5给出了XC2064和如今最先进的器件Virtex UltraScale+ VU13P的对比。这还不包括近年来不断发展的架构等更先进特征的发展。

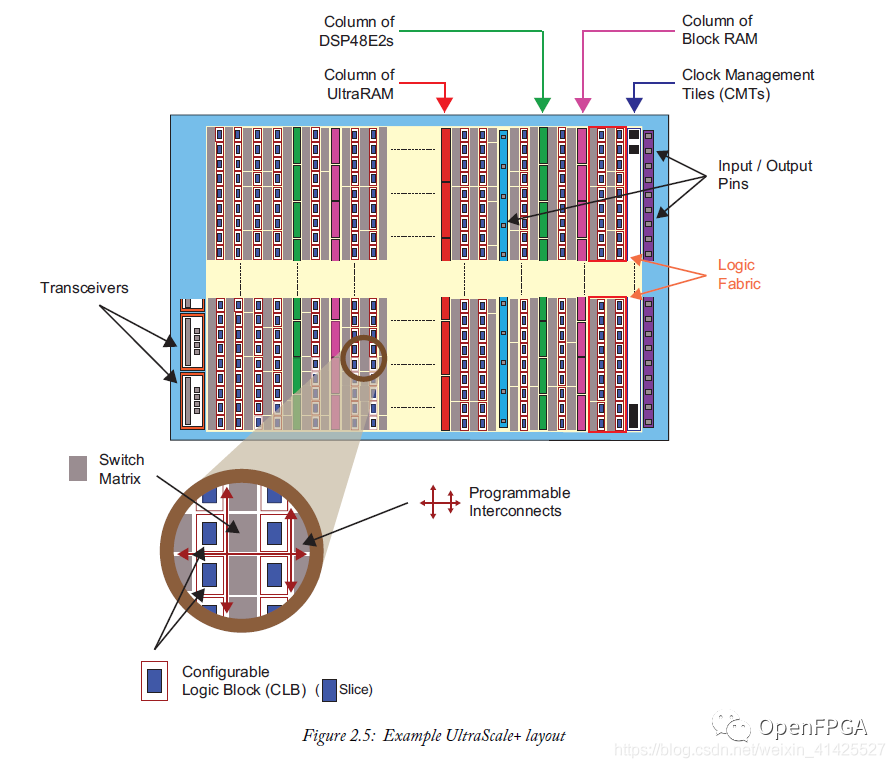

Xilinx基础的FPGA结构仍然是一个二维的数字逻辑元件阵列,以CLB分组。每一个CLB包含少量的触发器(flip-flop)和查找表(LUT),其中LUT用来实现布尔逻辑函数,小块存储器以及移位寄存器。从更底层面看,CLB的组成随着时间在不断发展,现代的CLB比早期的CLB含有更更多的逻辑资源。我们保留了这个术语,CLB仍然是将可编程互连线(programmable interconnects)和开关矩阵(switch matrices)连接到一起。当然这种连接技术也有了很大提高。在图2.5中,可以看到CLB的阵列结构的一个图示,开关矩阵和可编程互连线可在图2.5底部看到。

随着应用要求的发展,FPGA架构也在不断发展,更大的存储单元(从Bock RAM 到最近的 Ultra RAM)提供了更大密度更高速度的存储能力,例如更大的存储使得能够在器件中存储视频数据。在2000年左右集成了乘法器,之后又集成了算术处理模块(DSP48x slices)能够进行乘法,加减法以及其他的逻辑计算。当然,DSP这些年来也有了很大的发展。

随着FPGA技术越来越多的应用于基础通信设施,数据中心,高性能云计算,支持包含高速串口的IP块价值越来越大。

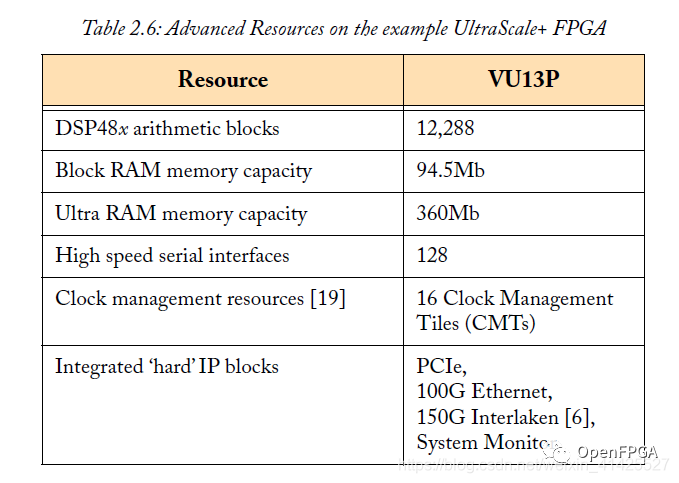

如表2.6所示,除了更大的面积,最新的FPGA包含更加专用的资源和功能。

下一节我们继续讨论UltraScale+ FPGAs的更多的细节。

现代FPGA架构:UltraScale+

现代的FPGA架构本质上也是一个器件的二维阵列。从某种意义上与早期的器件类似。其特点正如之前强调的时含有更丰富的资源,器件面积更大。

图2.5时UltraScale+ FPGA资源的一个图示,从较高的一个抽象层次来看,该图可认为由竖直方向的一块块区域组成。大部分区域属于通用目的逻辑(general purpose logic)。例如由查找表和触发器组成的CLB。还有一部分区域是Ultra RAM存储块以及DSP58x计算单元,排列在单或双列,组成较窄的竖直条纹区域。

在接口方面,输入/输出块被排列在bank(不好翻译)中,并在主要资源阵列中形成列。输入输出块(IOB)支持各种接口标准。另外的连接是以高速串行收发器的形式提供的,这些收发器通常位于FPGA边缘的四组。在这些基础上,提供了专用块来支持选定的通信标准(见表2.6)。在FPGA结构中还存在用于配置、时钟管理和系统监控的额外资源。

DSP功能

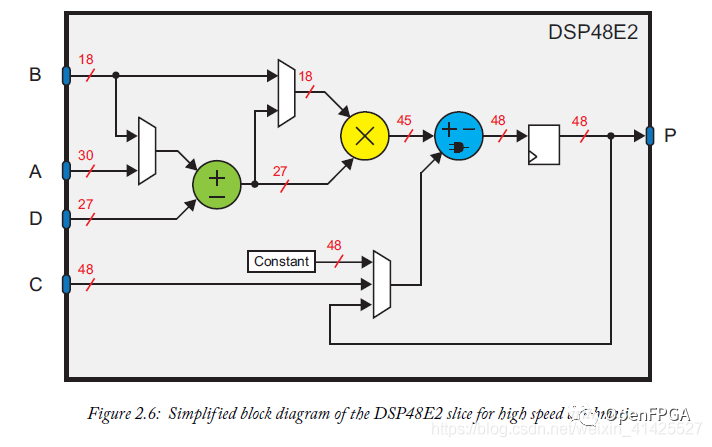

数字信号处理(DSP)的大部分操作都是定点数乘法和加法操作。常见的DSP任务,如有限脉冲响应(FIR)滤波和快速傅里叶变换(FFT)的计算,主要操作是加法/减法、乘法和采样延迟(sample delays)。在Xilinx FPGA中,这些操作主要由DSP48x slice完成。这个slice的简化框图如图2.6所示,该图显示了其算法操作和字长(wordlengths),省略了一些附加功能。例如延迟元件,信号路径以及多路复用器等。为了实现FIR或者FFT,可以将DSP48E2 slices级联到一起(不需要消耗FPGA资源)。例如需要实现一个比单独DSP slice字长更长的加法器——比如实现一个96位的加法器——可以将多个DSP48E2组合到一起。

除了计算功能外,DSP48E2 slice还可用于桶形移位寄存器、模式检测(pattern detection)以及其他逻辑操作。更多关于DSP48E2的完整信息,包括与之前的DSP48Ex相比的改进细节。可以查看文档:UltraScale Architecture DSP Slice: User Guide

存储支持

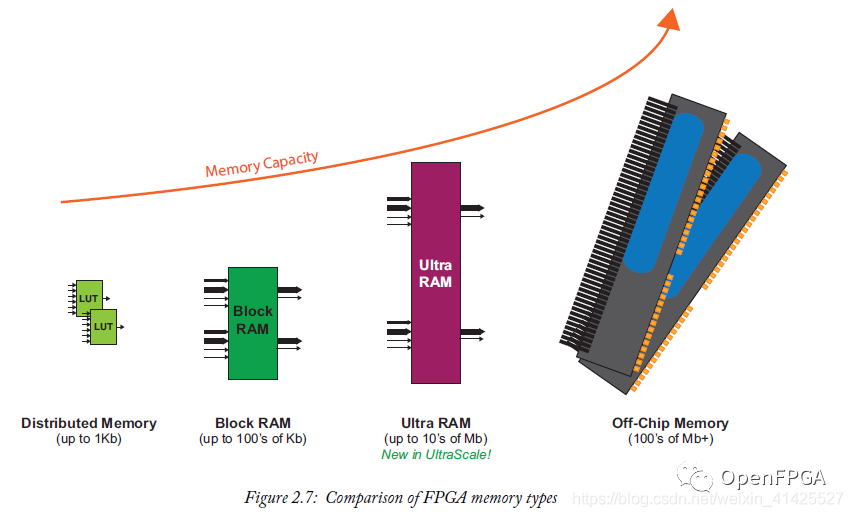

FPGA中的存储器可以由CLB资源组成,由CLB组成的的存储资源经常被用来存储少量数据。对于较大的存储,可以用Block RAM(能够存储36Kb,或分为两个18Kb的存储器),在UltraScale器件中,集成了具有更大存储能力的Ultra RAM(每个288Kb)。更大的存储器可以通过组合Block RAM 或者Ultra RAM实现。

Block RAM和Ultra RAM是作为FPGA上的专用物理block实现的,而不是由通用的更底层的逻辑元件组成的。它们支持高性能操作,能够以设备支持的最大时钟频率运行。Ultra RAM在不用时可以单独断电。关于Ultra RAM的更多细节参考文档:UltraRAM: Breakthrough Embedded Memory Integration on UltraScale+ Devices。

图2.7给出了FPGA上四种可用的存储资源。

随着器件面积的增加,尤其是Ultra RAM的引入,片上存储能力不断增强,这使得可以减少甚至消灭对片外存储的依赖。这使得我们减少了额外的系统消耗,接口努力(effort),能耗以及延迟和性能限制。图2.7的每一种存储都有各自的特征,在不同的任务中可以选择合适的。取决于采用的设计方法,设计人员能够选择特定的存储资源或者直接让综合工具去选择。

2.5 对比和讨论:FPGA,Zynq和Zynq MPSoC

这一节总结了FPGA,Zynq和Zynq MPSoC的不同特点,包括其架构、功耗、性能以及他们在嵌入式系统实现时的特点。

2.5.1 架构

(本小节大部分内容前面都已经提到过这里只给出一个结论性表格,更详细的总结可参考原书)

2.5.2 功耗和性能

多年来,在降低电力消耗的同时,在提高性能(即。最大处理频率,或“速度”)。从1985年发布的Xilinx FPGA到2011年7系列器件,能耗(每个逻辑单元测量)减少了1000倍以上。同时,性能增加了大约100倍。我们下面对这些器件进行一个简单的比较。

功耗

(参考原书)

性能

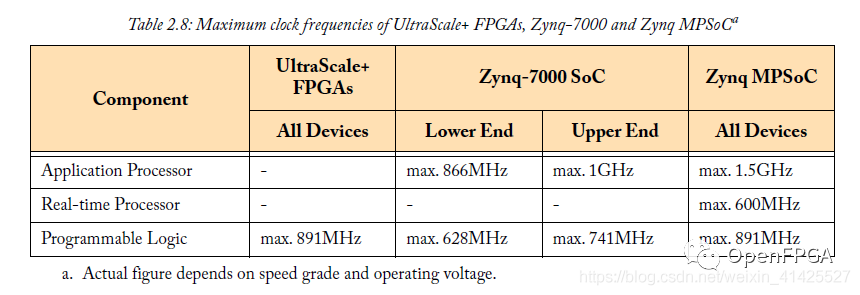

计算性能通常用最大处理频率来度量。为了比较性能,表2.8比较了PS和PL元件的最大时钟频率。

总之,FPGA和SoC设备的功耗是密切相关的,因为所有的SoC都包括一个与FPGA有效相同的PL区域。与Zynq和Zynq MPSoC相比,Zynq MPSoC器件的中的功耗(每个逻辑单元)较低,整体性能较高,这是由于UltraScale+ FPGA体系结构的各种优化所致。在PS方面,Zynq MPSoC体系结构更加复杂,提供了更高的性能,还包括了电源管理等附加特征。

原文标题:FPGA、Zynq 和 Zynq MPSoC简析及架构分析

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

看门狗在Zynq MPSoC上的使用技巧2023-06-30 3452

-

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计2022-11-02 2560

-

Zynq UltraScale ZU19EG MPSOC评估板2022-09-26 1348

-

FPGAs,Zynq和Zynq MPSoC器件的特点2022-08-15 4102

-

ZYNQ简介和Hello World介绍2022-02-17 1054

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 4869

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 2793

-

米尔科技Zynq UltraScale+ MPSoC技术参考手册介绍2019-11-18 4400

-

请问Zynq Ultrascale + MPSOC本身是否存在问题?2019-10-14 3051

-

如何利用ZYNQ MPSoC玩DOOM?2019-10-09 3859

-

Zynq UltraScale + MPSoC USB 3.0 CDC器件类设计2019-01-03 7811

-

全新Zynq UltraScale MPSoC的特点介绍2018-11-27 4771

-

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞2018-06-28 3131

-

用ZYNQ MPSoC玩DOOM!2017-11-18 3230

全部0条评论

快来发表一下你的评论吧 !