关于AI芯片的概念与发展历程及其应用领域

描述

2010年以来,由于大数据产业的发展,数据量呈现爆炸性增长态势,而传统的计算架构又无法支撑深度学习的大规模并行计算需求,于是研究界对AI芯片进行了新一轮的技术研发与应用研究。这一新兴技术既为科技巨头的业务升级和拓展带来转机,也给了新创企业颠覆现有格局的机会。

AI芯片是人工智能时代的技术核心之一,决定了平台的基础架构和发展生态。作为人工智能产业的重中之重,AI芯片已经成了最热门的投资领域,各种AI芯片层出不穷。

从广义上讲,只要能够运行人工智能算法的芯片都叫作AI芯片。但是通常意义上的AI芯片指的是针对人工智能算法做了特殊加速设计的芯片,现阶段,这些人工智能算法一般以深度学习算法为主,也可以包括其它机器学习算法。

一般来说,所谓的AI芯片,是指针对AI算法的ASIC(专用芯片)。传统的CPU、GPU都可以拿来执行AI算法,但是速度慢,性能低,无法实际商用。

比如,自动驾驶需要识别道路行人红绿灯等状况,但是如果是当前的CPU去算,那么估计车翻到河里了还没发现前方是河,这是速度慢,时间就是生命。如果用GPU,的确速度要快得多,但是,功耗大,汽车的电池估计无法长时间支撑正常使用,而且, GPU巨贵,普通消费者也用不起。另外,GPU因为不是专门针对AI算法开发的ASIC,所以,说到底,速度还没到极限,还有提升空间。而类似智能驾驶这样的领域,必须快!在手机终端,可以自行人脸识别、语音识别等AI应用,这个又必须功耗低。

AI芯片到底是什么?

回答这个问题之前,先来弄明白两个概念,什么是CPU和GPU?

简单来说,CPU就是手机的“大脑”,也是手机正常运行的“总指挥官”。GPU被翻译成图形处理器,主要工作确实是图像处理。

再来说说CPU和GPU之间的分工,CPU遵循的是冯诺依曼架构,核心就是“存储程序,顺序执行”,就像是做事一板一眼的管家,什么事情都要一步一步来。假如你让CPU去种一棵树,挖坑、浇水、植树、封土等工作都要独自一步一步进行。

如果让GPU去种一棵树的话,会喊来小A、小B、小C等一同来完成,把挖坑、浇水、植树、封土等工作分割成不同的子任务。这是因为GPU执行的是并行运算,即把一个问题分解成若干个部分,各部分由独立的计算单元去完成。恰好图像处理的每一个像素点都需要被计算,与GPU的工作原理不谋而合。

就如同比方:CPU像是老教授,积分、微分什么都会算,但有些工作是计算大量一百以内的加减乘除,最好的方法当然不是让老教授挨个算下去,而是雇上几十个小学生把任务分配下去。这就是CPU和GPU的分工,CPU负责大型运算,GPU为图像处理而生,从电脑到智能手机都是如此。

但当人工智能的需求出现后,CPU和GPU的分工就出现了问题,人工智能终端的深度学习和传统计算不同,借由后台预先从大量训练数据中总结出规律,得到可以给人工智能终端判定的参数,比如训练样本是人脸图像数据,实现的功能在终端上就是人脸识别。

CPU往往需要数百甚至上千条指令才能完成一个神经元的处理,无法支撑起大规模的并行运算,而手机上的GPU又需要处理各种应用的图像处理需求。强行使用CPU和GPU进行人工智能任务,结果普遍是效率低下、发热严重。

诸如苹果A12、麒麟980和Exynos 9820提供的AI芯片的一种。通俗来说就是人工智能加速器,因为GPU是基于块数据处理的,但手机上的AI应用是需要实时处理的,人工智能加速器刚好解决了这个痛点,把深度学习相关的工作接管过来,从而缓解CPU 和GPU 的压力。

它们将CPU和GPU的计算量分开,诸如面部识别、语音识别等AI相关的任务卸载到ASIC上处理,AI芯片核早已成为一种行业趋势。

一方面AI芯片的价值在于与CPU、GPU进行协同分工,CPU和GPU过多的任务堆叠只会虚耗电量、提高温度。

另一方面在AI芯片的协同下,可以对用户行为进行学习,进而对用户的使用场景进行预测,然后进行合理的性能分配。好比说当你在游戏时让CPU高效运算,而当你在看电子书时避免性能浪费。

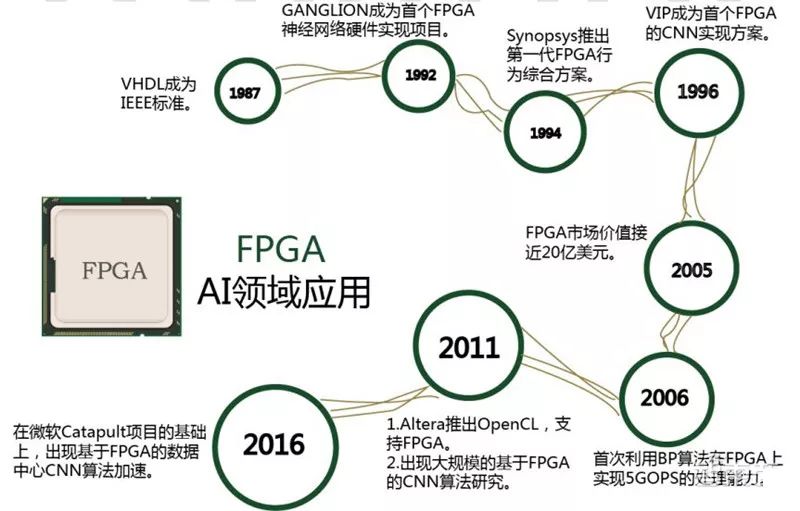

AI芯片发展历程

从图灵的论文《计算机器与智能》和图灵测试,到最初级的神经元模拟单元——感知机,再到现在多达上百层的深度神经网络,人类对人工智能的探索从来就没有停止过。上世纪八十年代,多层神经网络和反向传播算法的出现给人工智能行业点燃了新的火花。反向传播的主要创新在于能将信息输出和目标输出之间的误差通过多层网络往前一级迭代反馈,将最终的输出收敛到某一个目标范围之内。1989年贝尔实验室成功利用反向传播算法,在多层神经网络开发了一个手写邮编识别器。1998年Yann LeCun和Yoshua Bengio发表了手写识别神经网络和反向传播优化相关的论文《Gradient-based learning applied to document recognition》,开创了卷积神经网络的时代。

此后,人工智能陷入了长时间的发展沉寂阶段,直到1997年IBM的深蓝战胜国际象棋大师和2011年IBM的沃森智能系统在Jeopardy节目中胜出,人工智能才又一次为人们所关注。2016年Alpha Go击败韩国围棋九段职业选手,则标志着人工智能的又一波高潮。从基础算法、底层硬件、工具框架到实际应用场景,现阶段的人工智能领域已经全面开花。

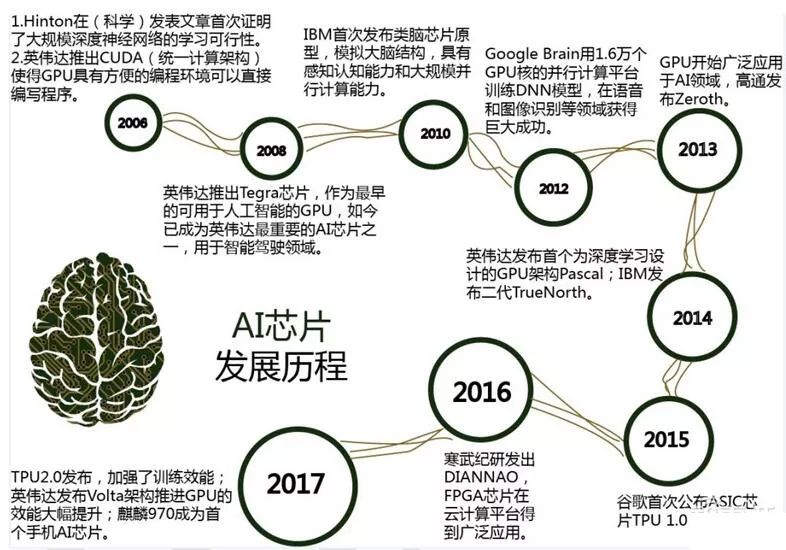

作为人工智能核心的底层硬件AI芯片,也同样经历了多次的起伏和波折,总体看来,AI芯片的发展前后经历了四次大的变化,其发展历程如图所示。

1、2007年以前,AI芯片产业一直没有发展成为成熟的产业;同时由于当时算法、数据量等因素,这个阶段AI芯片并没有特别强烈的市场需求,通用的CPU芯片即可满足应用需要。

2、随着高清视频、VR、AR游戏等行业的发展,GPU产品取得快速的突破;同时人们发现GPU的并行计算特性恰好适应人工智能算法及大数据并行计算的需求,如GPU比之前传统的CPU在深度学习算法的运算上可以提高几十倍的效率,因此开始尝试使用GPU进行人工智能计算。

3、进入2010年后,云计算广泛推广,人工智能的研究人员可以通过云计算借助大量CPU和GPU进行混合运算,进一步推进了AI芯片的深入应用,从而催生了各类AI芯片的研发与应用。

4、人工智能对于计算能力的要求不断快速地提升,进入2015年后,GPU性能功耗比不高的特点使其在工作适用场合受到多种限制,业界开始研发针对人工智能的专用芯片,以期通过更好的硬件和芯片架构,在计算效率、能耗比等性能上得到进一步提升。

AI芯片与普通芯片的区别在哪里?

AI算法,在图像识别等领域,常用的是CNN卷积网络,语音识别、自然语言处理等领域,主要是RNN,这是两类有区别的算法。但是,他们本质上,都是矩阵或vector的乘法、加法,然后配合一些除法、指数等算法。

一个成熟的AI算法,比如YOLO-V3,就是大量的卷积、残差网络、全连接等类型的计算,本质是乘法和加法。对于YOLO-V3来说,如果确定了具体的输入图形尺寸,那么总的乘法加法计算次数是确定的。比如一万亿次。(真实的情况比这个大得多的多)那么要快速执行一次YOLO-V3,就必须执行完一万亿次的加法乘法次数。

这个时候就来看了,比如IBM的POWER8,最先进的服务器用超标量CPU之一,4GHz,SIMD,128bit,假设是处理16bit的数据,那就是8个数,那么一个周期,最多执行8个乘加计算。一次最多执行16个操作。这还是理论上,其实是不大可能的。那么CPU一秒钟的巅峰计算次数=16X4Gops=64Gops。这样,可以算算CPU计算一次的时间了。同样的,换成GPU算算,也能知道执行时间。

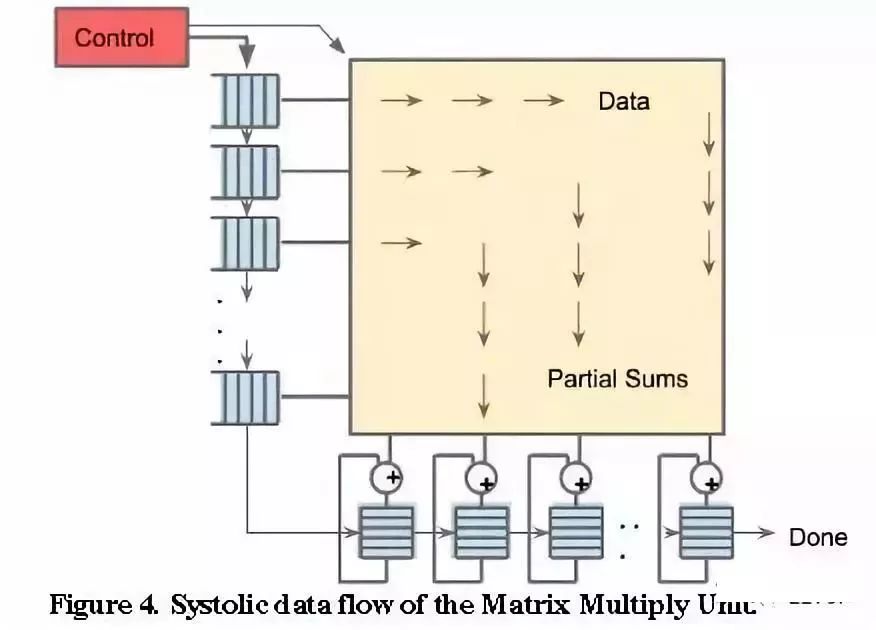

再来说说AI芯片。比如大名鼎鼎的谷歌的TPU1。

TPU1,大约700M Hz,有256X256尺寸的脉动阵列,如下图所示。一共256X256=64K个乘加单元,每个单元一次可执行一个乘法和一个加法。那就是128K个操作。(乘法算一个,加法再算一个)

另外,除了脉动阵列,还有其他模块,比如激活等,这些里面也有乘法、加法等。所以,看看TPU1一秒钟的巅峰计算次数至少是=128K X 700MHz=89600Gops=大约90Tops。对比一下CPU与TPU1,会发现计算能力有几个数量级的差距,这就是为啥说CPU慢。

当然,以上的数据都是完全最理想的理论值,实际情况,能够达到5%吧。因为,芯片上的存储不够大,所以数据会存储在DRAM中,从DRAM取数据很慢的,所以,乘法逻辑往往要等待。另外,AI算法有许多层网络组成,必须一层一层的算,所以,在切换层的时候,乘法逻辑又是休息的,所以,诸多因素造成了实际的芯片并不能达到利润的计算峰值,而且差距还极大。

目前来看,神经网络的尺寸是越来越大,参数越来越多,遇到大型NN模型,训练需要花几周甚至一两个月的时候。突然断电,还得一切重来。修改了模型,需要几个星期才能知道对错,确定等得起?突然有了TPU,然后你发现,吃个午饭回来就好了,参数优化一下,继续跑,多么爽!

总的来说,CPU与GPU并不是AI专用芯片,为了实现其他功能,内部有大量其他逻辑,而这些逻辑对于目前的AI算法来说是完全用不上的,所以,自然造成CPU与GPU并不能达到最优的性价比。

目前在图像识别、语音识别、自然语言处理等领域,精度最高的算法就是基于深度学习的,传统的机器学习的计算精度已经被超越,目前应用最广的算法,估计非深度学习莫属,而且,传统机器学习的计算量与深度学习比起来少很多,所以,讨论AI芯片时就针对计算量特别大的深度学习而言。毕竟,计算量小的算法,说实话,CPU已经很快了。而且,CPU适合执行调度复杂的算法,这一点是GPU与AI芯片都做不到的,所以他们三者只是针对不同的应用场景而已,都有各自的主场。

AI芯片的分类及技术

人工智能芯片目前有两种发展路径:一种是延续传统计算架构,加速硬件计算能力,主要以3种类型的芯片为代表,即GPU、FPGA、ASIC,但CPU依旧发挥着不可替代的作用;另一种是颠覆经典的冯·诺依曼计算架构,采用类脑神经结构来提升计算能力,以IBM TrueNorth芯片为代表。

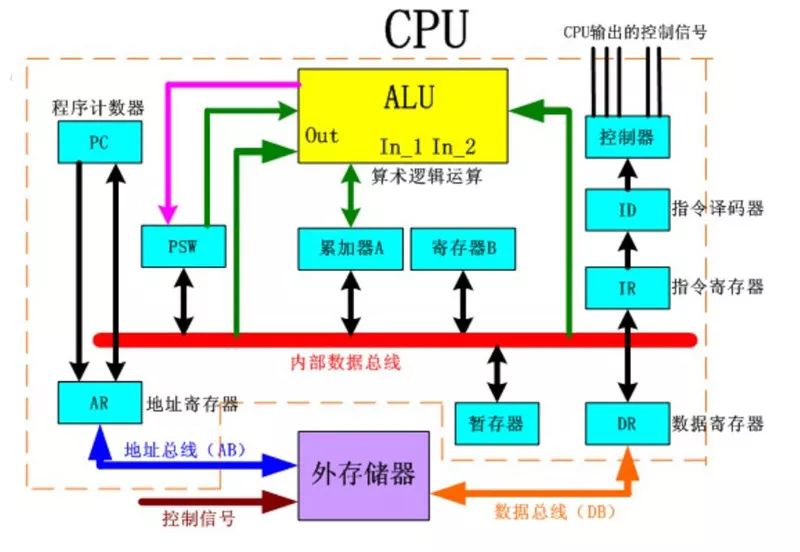

传统的CPU

计算机工业从1960年代早期开始使用CPU这个术语。迄今为止,CPU从形态、设计到实现都已发生了巨大的变化,但是其基本工作原理却一直没有大的改变。通常CPU由控制器和运算器这两个主要部件组成。传统的CPU内部结构图如图3所示,从图中我们可以看到:实质上仅单独的ALU模块(逻辑运算单元)是用来完成数据计算的,其他各个模块的存在都是为了保证指令能够一条接一条的有序执行。这种通用性结构对于传统的编程计算模式非常适合,同时可以通过提升CPU主频(提升单位时间内执行指令的条数)来提升计算速度。但对于深度学习中的并不需要太多的程序指令、却需要海量数据运算的计算需求,这种结构就显得有些力不从心。尤其是在功耗限制下,无法通过无限制的提升CPU和内存的工作频率来加快指令执行速度,这种情况导致CPU系统的发展遇到不可逾越的瓶颈。

并行加速计算的GPU

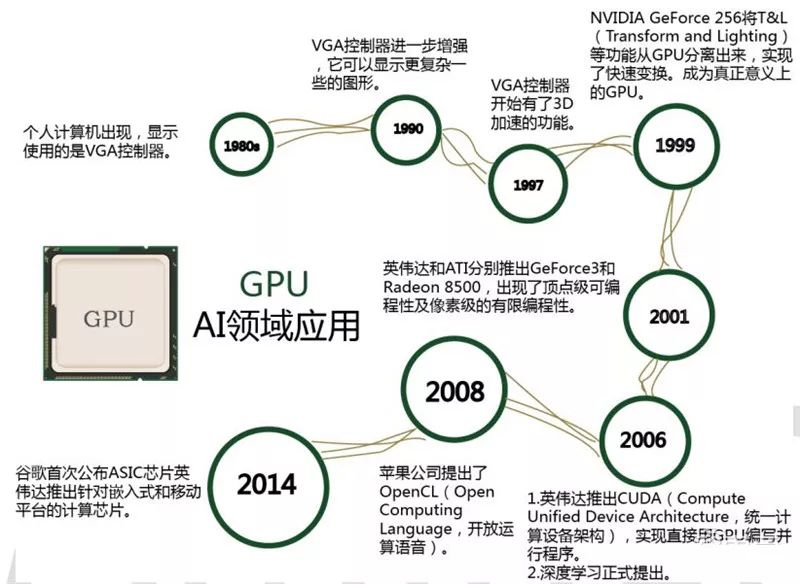

GPU作为最早从事并行加速计算的处理器,相比CPU速度快,同时比其他加速器芯片编程灵活简单。

传统的CPU之所以不适合人工智能算法的执行,主要原因在于其计算指令遵循串行执行的方式,没能发挥出芯片的全部潜力。与之不同的是,GPU具有高并行结构,在处理图形数据和复杂算法方面拥有比CPU更高的效率。对比GPU和CPU在结构上的差异,CPU大部分面积为控制器和寄存器,而GPU拥有更ALU(ARITHMETIC LOGIC UNIT,逻辑运算单元)用于数据处理,这样的结构适合对密集型数据进行并行处理,CPU与GPU的结构对比如图所示。程序在GPU系统上的运行速度相较于单核CPU往往提升几十倍乃至上千倍。随着英伟达、AMD等公司不断推进其对GPU大规模并行架构的支持,面向通用计算的GPU(即GPGPU,GENERAL PURPOSE GPU,通用计算图形处理器)已成为加速可并行应用程序的重要手段。

GPU的发展历程如图所示:

目前,GPU已经发展到较为成熟的阶段。谷歌、FACEBOOK、微软、TWITTER和百度等公司都在使用GPU分析图片、视频和音频文件,以改进搜索和图像标签等应用功能。此外,很多汽车生产商也在使用GPU芯片发展无人驾驶。不仅如此,GPU也被应用于VR/AR相关的产业。但是GPU也有一定的局限性。深度学习算法分为训练和推断两部分,GPU平台在算法训练上非常高效。但在推断中对于单项输入进行处理的时候,并行计算的优势不能完全发挥出来。

半定制化的FPGA

FPGA是在PAL、GAL、CPLD等可编程器件基础上进一步发展的产物。用户可以通过烧入FPGA配置文件来定义这些门电路以及存储器之间的连线。这种烧入不是一次性的,比如用户可以把FPGA配置成一个微控制器MCU,使用完毕后可以编辑配置文件把同一个FPGA配置成一个音频编解码器。因此,它既解决了定制电路灵活性的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA可同时进行数据并行和任务并行计算,在处理特定应用时有更加明显的效率提升。对于某个特定运算,通用CPU可能需要多个时钟周期;而FPGA可以通过编程重组电路,直接生成专用电路,仅消耗少量甚至一次时钟周期就可完成运算。

此外,由于FPGA的灵活性,很多使用通用处理器或ASIC难以实现的底层硬件控制操作技术,利用FPGA可以很方便的实现。这个特性为算法的功能实现和优化留出了更大空间。同时FPGA一次性成本(光刻掩模制作成本)远低于ASIC,在芯片需求还未成规模、深度学习算法暂未稳定,需要不断迭代改进的情况下,利用FPGA芯片具备可重构的特性来实现半定制的人工智能芯片是最佳选择之一。

功耗方面,从体系结构而言,FPGA也具有天生的优势。传统的冯氏结构中,执行单元(如CPU核)执行任意指令,都需要有指令存储器、译码器、各种指令的运算器及分支跳转处理逻辑参与运行,而FPGA每个逻辑单元的功能在重编程(即烧入)时就已经确定,不需要指令,无需共享内存,从而可以极大的降低单位执行的功耗,提高整体的能耗比。

由于FPGA具备灵活快速的特点,因此在众多领域都有替代ASIC的趋势。FPGA在人工智能领域的应用如图所示。

全定制化的ASIC

目前以深度学习为代表的人工智能计算需求,主要采用GPU、FPGA等已有的适合并行计算的通用芯片来实现加速。在产业应用没有大规模兴起之时,使用这类已有的通用芯片可以避免专门研发定制芯片(ASIC)的高投入和高风险。但是,由于这类通用芯片设计初衷并非专门针对深度学习,因而天然存在性能、功耗等方面的局限性。随着人工智能应用规模的扩大,这类问题日益突显。

GPU作为图像处理器,设计初衷是为了应对图像处理中的大规模并行计算。因此,在应用于深度学习算法时,有三个方面的局限性:第一,应用过程中无法充分发挥并行计算优势。深度学习包含训练和推断两个计算环节,GPU在深度学习算法训练上非常高效,但对于单一输入进行推断的场合,并行度的优势不能完全发挥。第二,无法灵活配置硬件结构。GPU采用SIMT计算模式,硬件结构相对固定。目前深度学习算法还未完全稳定,若深度学习算法发生大的变化,GPU无法像FPGA一样可以灵活的配制硬件结构。第三,运行深度学习算法能效低于FPGA。

尽管FPGA倍受看好,甚至新一代百度大脑也是基于FPGA平台研发,但其毕竟不是专门为了适用深度学习算法而研发,实际应用中也存在诸多局限:第一,基本单元的计算能力有限。为了实现可重构特性,FPGA内部有大量极细粒度的基本单元,但是每个单元的计算能力(主要依靠LUT查找表)都远远低于CPU和GPU中的ALU模块;第二、计算资源占比相对较低。为实现可重构特性,FPGA内部大量资源被用于可配置的片上路由与连线;第三,速度和功耗相对专用定制芯片(ASIC)仍然存在不小差距;第四,FPGA价格较为昂贵,在规模放量的情况下单块FPGA的成本要远高于专用定制芯片。

深度学习算法稳定后,AI芯片可采用ASIC设计方法进行全定制,使性能、功耗和面积等指标面向深度学习算法做到最优。

类脑芯片

类脑芯片不采用经典的冯·诺依曼架构,而是基于神经形态架构设计,以IBM Truenorth为代表。IBM研究人员将存储单元作为突触、计算单元作为神经元、传输单元作为轴突搭建了神经芯片的原型。目前,Truenorth用三星28nm功耗工艺技术,由54亿个晶体管组成的芯片构成的片上网络有4096个神经突触核心,实时作业功耗仅为70mW。由于神经突触要求权重可变且要有记忆功能,IBM采用与CMOS工艺兼容的相变非挥发存储器(PCM)的技术实验性的实现了新型突触,加快了商业化进程。

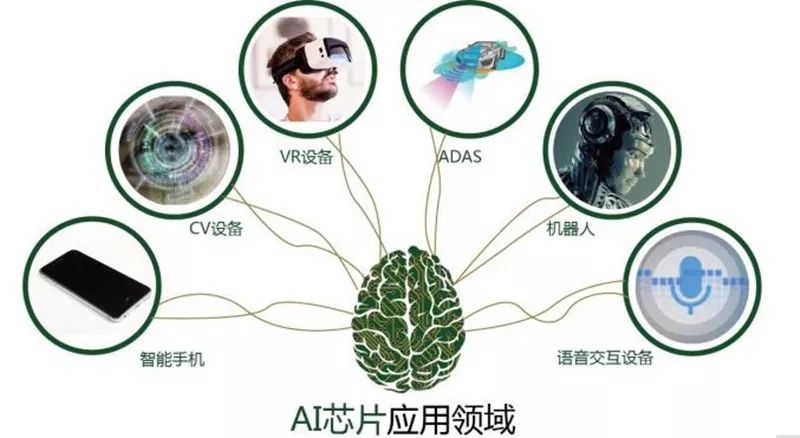

AI芯片应用领域

随着人工智能芯片的持续发展,应用领域会随时间推移而不断向多维方向发展。

智能手机

2017年9月,华为在德国柏林消费电子展发布了麒麟970芯片,该芯片搭载了寒武纪的NPU,成为“全球首款智能手机移动端AI芯片”;2017年10月中旬Mate10系列新品(该系列手机的处理器为麒麟970)上市。搭载了NPU的华为Mate10系列智能手机具备了较强的深度学习、本地端推断能力,让各类基于深度神经网络的摄影、图像处理应用能够为用户提供更加完美的体验。

而苹果发布以iPhone X为代表的手机及它们内置的A11 Bionic芯片。A11 Bionic中自主研发的双核架构Neural Engine(神经网络处理引擎),它每秒处理相应神经网络计算需求的次数可达6000亿次。这个Neural Engine的出现,让A11 Bionic成为一块真正的AI芯片。A11 Bionic大大提升了iPhone X在拍照方面的使用体验,并提供了一些富有创意的新用法。

ADAS(高级辅助驾驶系统)

ADAS是最吸引大众眼球的人工智能应用之一,它需要处理海量的由激光雷达、毫米波雷达、摄像头等传感器采集的实时数据。相对于传统的车辆控制方法,智能控制方法主要体现在对控制对象模型的运用和综合信息学习运用上,包括神经网络控制和深度学习方法等。

CV(计算机视觉(Computer Vision)设备

需要使用计算机视觉技术的设备,如智能摄像头、无人机、行车记录仪、人脸识别迎宾机器人以及智能手写板等设备,往往都具有本地端推断的需要,如果仅能在联网下工作,无疑将带来糟糕的体验。而计算机视觉技术目前看来将会成为人工智能应用的沃土之一,计算机视觉芯片将拥有广阔的市场前景。

VR设备

VR设备芯片的代表为HPU芯片,是微软为自身VR设备Hololens研发定制的。这颗由台积电代工的芯片能同时处理来自5个摄像头、1个深度传感器以及运动传感器的数据,并具备计算机视觉的矩阵运算和CNN运算的加速功能。这使得VR设备可重建高质量的人像3D影像,并实时传送到任何地方。

语音交互设备

语音交互设备芯片方面,国内有启英泰伦以及云知声两家公司,其提供的芯片方案均内置了为语音识别而优化的深度神经网络加速方案,实现设备的语音离线识别。稳定的识别能力为语音技术的落地提供了可能;与此同时,语音交互的核心环节也取得重大突破。语音识别环节突破了单点能力,从远场识别,到语音分析和语义理解有了重大突破,呈现出一种整体的交互方案。

机器人

无论是家居机器人还是商用服务机器人均需要专用软件+芯片的人工智能解决方案,这方面典型公司有由前百度深度学习实验室负责人余凯创办的地平线机器人,当然地平线机器人除此之外,还提供ADAS、智能家居等其他嵌入式人工智能解决方案。

编辑:lyn

-

AI大模型的发展历程和应用前景2024-07-03 3617

-

芯片技术的发展历程和应用领域2023-11-27 5737

-

大小端模式各有哪些优点及其应用领域呢2022-02-22 1661

-

ARM微处理器的应用领域及其特点2021-12-14 2111

-

小白求助,求ARM系列芯片的发展历程2021-10-21 1732

-

DSP芯片有哪些应用领域2021-10-15 3973

-

单片机的特点及应用领域2021-07-13 1424

-

工业机器人的认知和发展历程及应用领域行业现状等资料说明2019-12-12 1920

-

LED和OLED显示技术概念原理发展背景和应用领域与发展概述2019-11-27 1807

-

【免费直播】AI芯片专家陈小柏博士,带你解析AI算法及其芯片操作系统。2019-11-07 3744

-

AI发展对芯片技术有什么影响?2019-08-12 3520

-

安森美智能感知技术对三大应用领域发展有什么影响?2019-07-30 3478

-

剖析人脸识别技术及其应用领域和发展趋势2018-11-23 8018

-

半导体材料的发展历程和应用领域2010-03-04 15832

全部0条评论

快来发表一下你的评论吧 !