解析MIPS内核的HDTV-SoC平台总线接口模块

电子说

描述

“介绍了使用MIPS32TM4KcTM处理器作为CPU内核的高清晰度电视(HDTV)SoC平台,着重提出了该平台上系统总线接口(HIF)模块的设计方案。并通过仿真和综合实验,验证了该模块能够达到系统总体设计的要求。”

在系统级芯片(SoC)的设计当中,MIPS的RISC处理器是一种应用非常广泛的嵌入式CPU,它具有高性能、低功耗的特点,可以很方便地集成到一个完整的片上系统之中,使开发者能够专注于用户IP模块的设计。MIPS架构的处理器占据了数字机顶盒微处理器和解码器用CPU架构市场领域的领先地位。在MIPS家族的产品当中,32位的4KcTM处理器是具有代表性的一款,它采用了MIPS32的CPU架构,支持MIPS IITM指令集。在本文介绍的SoC系统设计中,就采用了MIPS32TM4KcTM处理器作为芯片的CPU内核。

在当前的数字消费电子市场领域,基于SoC平台的HDTV芯片是所有数字电视接收及播放设备的核心器件。SoC芯片具体到HDTV解码系统,就是把MPEG-2解复用(DeMux)、音视频解码(AVD)、视频格式转换(VTP)、画面后处理(OSD)以及接口I/O控制等功能模块都集成在一块芯片上。而要把众多功能复杂的系统控制模块和用户IP模块集成到一个芯片上并使其能够协调工作,就必须设计好各个模块之间的接口。本文针对高清数字电视SoC平台的项目,提出了系统总线接口模块(Host Bus Interface,HIF)的设计方案,并进行了仿真实验。

HIF模块在系统中的主要功能

HDTV-SoC平台是一个功能强大、结构复杂的系统,本文重点介绍了SoC架构中片上总线控制器的设计。片上总线能够提供针对特定应用的灵活多样的集成方法,它需要结构简单,速度快捷,在单芯片中实现多资源互联。HDTV-SoC系统的总线结构如图1所示。它分为3个层次,即与MIPS处理器接口的Ec总线(EcInterface)、系统总线和外围总线。

由图1可见,HIF模块在系统中所处的位置是十分关键的,它是系统总线(Host Bus)和各个IP模块以及周边I/O模块之间的接口单元,即系统总线和外围总线之间的桥梁,在系统中起着“承前启后”的作用,是CPU和外部模块之间数据交换的重要通道。具体而言,HIF模块主要完成3大功能,分别为外部模块W/R寄存器的设置和状态寄存器的读取、外部模块双口RAM的读写控制、外部模块中断的控制和管理。

电路功能模块设计

由上文所述可知,HIF电路设计主要分为3个模块:寄存器读写模块,双口RAM读写模块和中断处理模块。

寄存器读写模块

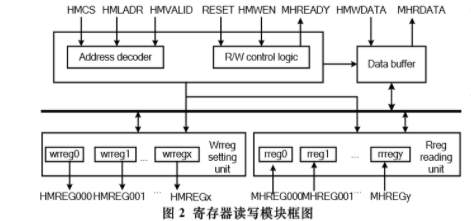

CPU和外部模块之间进行数据交互的一个重要方式就是通过寄存器的读写,实现对外部模块功能的控制和初始化。系统总线按照规定的时序读写HIF模块内部的寄存器资源,这些寄存器的每个比特位以连线的方式直接与外部模块互连。HIF模块在接收到系统总线过来的地址和数据之后,首先进行地址译码,选择相应的寄存器,再将数据写入。图2为该模块的逻辑框图。

MIPS的4Kc处理器支持猝发(burst)操作,所谓猝发操作是指在给出首地址之后,可以连续进行多个读写操作,而无须再给出每次操作的相应地址。在总线上,一个猝发指令与单个操作指令一样,只占用一个时钟周期。HIF模块在处理猝发操作时,将一个猝发指令转换为4个单周期指令,在转换之后,要保证从总线上过来的写数据与其相应的指令同步。

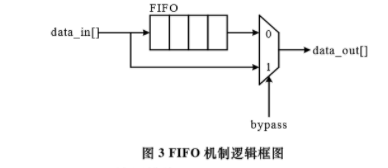

这样在猝发操作时,从寄存器组的角度看到的写数据与指令是同时发生的,尽管实际情况并不是这样。而要实现这种猝发操作,就必须引入一种FIFO机制。FIFO的深度为4,这与4Kc处理器所支持的猝发长度是一致的。在系统复位之后FIFO清空,可以随时接收总线上的猝发数据。在系统正常工作时,FIFO模块分别通过“in”和“out”指针来指示输入和输出的数据,以跟踪FIFO的使用情况。FIFO还需要用到一个“bypass”信号来确定是否旁路该模块,这发生在单个指令操作的情况下(bypass=‘1’),这时数据是绕过FIFO而直接通向寄存器的。FIFO机制的逻辑框图见图3。

双口RAM读写模块

在与系统总线的接口逻辑方面,RAM读写模块与寄存器读写模块是类似的,这里不再赘述。不同之处在于与外部模块的接口逻辑,寄存器读写模块是采用直接连线的方式,而RAM读写模块则必须满足相应的双口RAM的接口时序。在本设计中,选用了SMIC的0.18µm库的双口RAM单元作为模型。该模型的接口时序如图4所示,包括了读时序和写时序两种情况。

中断控制模块

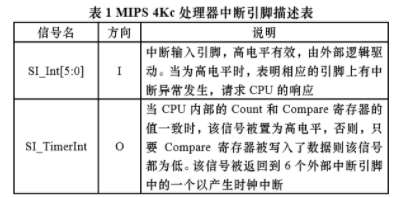

中断控制模块负责处理由DeMux、VD、GPIO等外部模块的中断源所发出的中断,对于系统来说,如何使产生的中断尽快得到响应是一个关键的问题。在图1中可以看到MIPS4Kc处理器所提供的中断引脚的连接情况,有关其引脚的说明如表1所示[1]。

表1 MIPS4Kc处理器中断引脚描述表

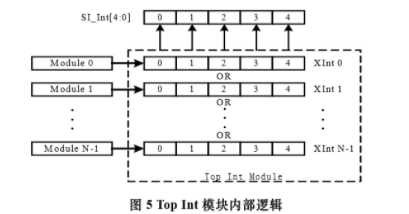

习惯将SI_TimerInt信号接到SI_Int[5]引脚,就像图1中所显示的那样。这样4Kc处理器的外部中断引脚就剩下5根,即SI_Int[4:0]。在本设计中,将系统外部中断分为5级,按照SI_Int[0]到SI_Int[4]的顺序优先级从高到低排列。针对每个外部模块,也将其所有的中断源分为5级,反映到每个模块的输出是一个5比特的寄存器XInt[4:0],同样,按照XInt[0]到XInt[5]的顺序中断优先级从高到低排列。假设系统有N个外部模块,则各个模块输出的XInt之间相或即得到SI_Int的输入,这些逻辑在TopInt模块中实现,如图5所示。

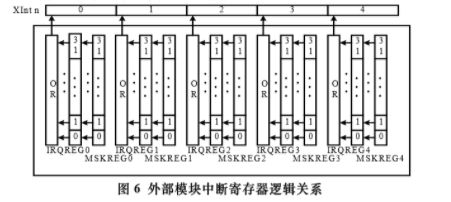

需要说明的是,TopInt模块本身也被当作系统的一个外部模块,系统可以对其进行与其它模块相同的寄存器读写操作。这样CPU在处理外部中断时,就可以通过读取XIntn寄存器的内容,追溯中断的产生源。另外,在每一个外部模块内部,设置5个32位的中断请求寄存器IRQREG0~IRQREG4和5个32位的中断屏蔽寄存器MSKREG0~MSKREG4。

当MSKREGn寄存器中的某个比特位被置“1”时,则IRQREGn寄存器中相应比特位的中断被屏蔽。在每一个IRQREGn寄存器当中,32个比特位之间相或即得到该模块相应XInt寄存器中的第n比特位的值。由此也可以看出,按照IRQREG0到IRQREG4的顺序,中断优先级从高到低。它们之间的逻辑关系如图6所示。

另外,为了便于CPU的访问,所有这些寄存器在模块中都有编址。这样对于任意一个中断,最多通过两次查询CPU就可以获知产生该中断的中断源。

仿真与综合

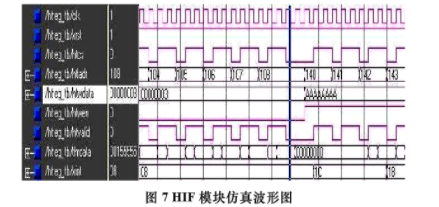

设计的仿真工作是分两部分进行的。各模块先单独仿真,待波形正确后再各模块联调。在编制TESTBENCH时,分别在不同的文件当中处理不同的工作情况。具体到HIF模块,仿真主要完成如下方面的验证:寄存器的写入和读取、双口RAM的写入和读取以及中断的产生和获取。在设计中,采用VHDL语言编写代码,以及Mentor公司的ModelSimSE5.7工具进行编译和仿真。在仿真时,SMIC库提供的双口RAM模型作为外部模块挂接在系统中,模型的接口时序与图4中所示的完全一致。图7为节选的HIF模块仿真波形。

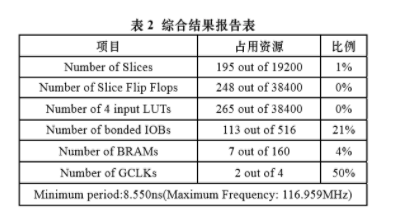

由于整个SoC系统的设计工作尚处于FPGA验证阶段,因此在综合时选用Xilinx公司的ISE6.1软件中自带的XST综合工具,FPGA器件选择Virtex-E系列的XCV2000E。综合后的结果报告如表2所示。

表2 综合结果报告表

总结

由仿真和综合的实验结果可以看出,HIF模块的设计可以满足系统在功能上的要求,而且综合后的模块所占用的FPGA的面积和资源的比例都很小,有些甚至可以忽略不计,因而不会影响到系统中其它模块的设计与实现。而综合后的主工作频率为116.959MHz,完全满足设计要求。

编辑:jq

-

mips32 soc方案2012-07-31 2200

-

MIPS32 M4K内核标准功能SRAM接口2019-05-28 1809

-

怎么实现基于IP内核的PCI总线接口设计?2021-05-27 2347

-

HDTV SOC系统中SDRAM控制器的设计2009-08-14 508

-

MIPS32 74K内核系列的微架构优势2009-12-19 658

-

基于MIPS32内核,Metalink推出新型WLAN芯片2006-03-13 711

-

MIPS与Tensilica推动Android上的SoC设计2009-12-21 822

-

瑞昱获多款MIPS32 Pro Series内核授权2010-01-08 3071

-

瑞昱获多款MIPS32TM Pro SeriesTM内核授权2010-01-11 1297

-

MIPS科技与摩威科技合作开发移动SoC2010-02-26 1280

-

龙芯中科获MIPS32与MIPS64架构授权 持续开发MIPS-Based龙芯CPU内核2011-08-24 1941

-

嵌入式MIPS32 M4K处理器内核SRAM接口应用2011-09-02 7033

-

Sequans新款LTE SoC采用MIPS处理器2011-11-14 1163

-

MIPS的强大武器,Aptiv内核细节详解2013-07-08 11011

-

MIPS CPU体系结构概述之Linux MIPS内核的详细资料说明2021-03-29 961

全部0条评论

快来发表一下你的评论吧 !