对AXI总线知识详解解析

描述

前言

本文针对秋招面试高频问题: AXI总线进行总结学习;

1.简介

AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA3.0中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。AMBA4.0将其修改升级为AXI4.0。AMBA4 包括AXI4、AXI4-lite、ACE4、AXI4-stream。

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

1.1 AXI协议特点

AMBA AXI协议支持支持高性能、高频率系统设计;

适合高带宽低延时设计

无需复杂的桥就能实现高频操作

能满足大部分器件的接口要求

适合高初始延时的存储控制器

提供互联架构的灵活性与独立性

向下兼容已有的AHB和APB接口关键特点

分离的地址/控制、数据相位

使用字节选通,支持非对齐的数据传输

基于burst传输,只需传输首地址

读、写数据通道分离,能提供低功耗DMA

支持多种寻址方式

支持乱序传输

易于添加寄存器级来进行时序收敛

支持outstanding AXI可以连续发送多个突发传输的首地址而无需等待之前的突发传输完成,这有助于流水处理transaction

1.2 AXI读写架构

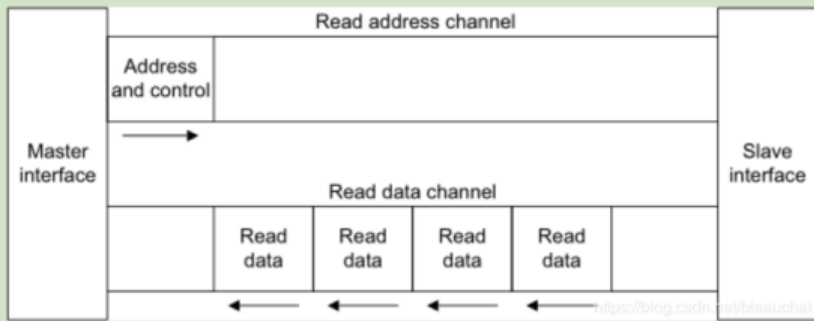

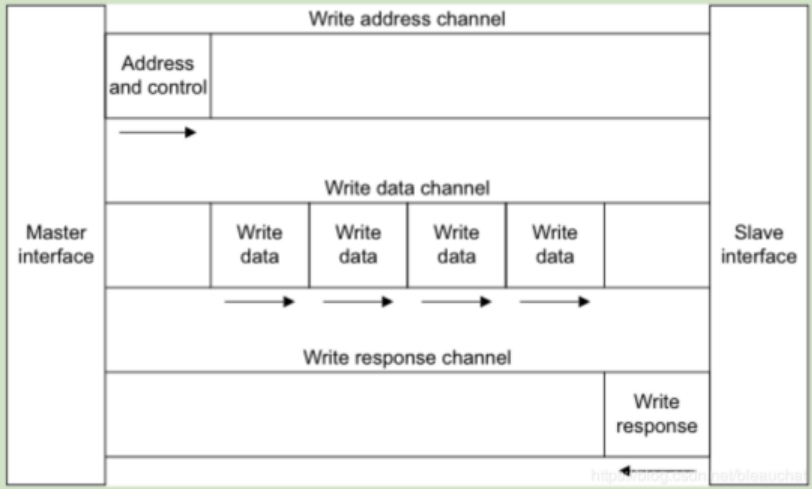

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。 地址通道携带控制消息,用于描述被传输的数据属性;数据传输使用写通道来实现master到slave的传输,slave使用写响应通道来完成一次写传输;读通道用来实现数据从slave到master的传输。

读架构

写架构

AXI使用基于VALID/READY的握手机制数据传输协议;传输源端使用VALID表明地址/控制信号、数据是有效的;目的端使用READY表明自己能够接受信息 ;读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息;

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024 bit)和指示读传输完成的读响应信号;

写数据通道:写数据通道的数据信息被认为是缓冲了的,master无需等待slave对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16/32/64/128/256/512/1024 bit)和字节线(用于指示8 bit 数据信号的有效性);

写响应通道:slave使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号;

通道名称通道功能数据流向

read address读地址通道主机-》从机

read data读数据通道(包括数据通道和读响应通道)从机-》主机

write address写地址通道主机-》从机

write data写数据通道(包括数据通道和每8bit一个byte的写数据有效信号)主机-》从机

write response写响应通道从机-》主机

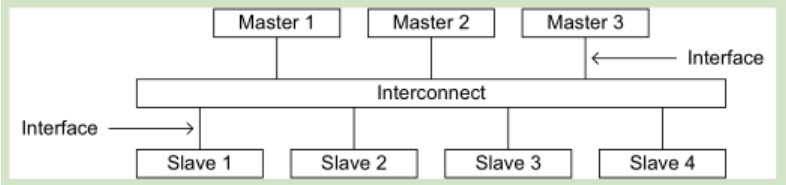

1.3 接口和互联

AXI协议提供单一的接口定义,用在下述三种接口之间:master/interconnect、slave/interconnect、master/slave。可以使用以下几种典型的系统拓扑架构:

共享地址与数据总线

共享地址总线,多数据总线

multilayer多层,多地址总线,多数据总线

在大多数系统中,地址通道的带宽要求没有数据通道高,因此可以使用共享地址总线,多数据总线结构来对系统性能和互联复杂度进行平衡;

寄存器片(Register Slices):每个AXI通道使用单一方向传输信息,并且各个通道直接没有任何固定关系。因此可以可以在任何通道任何点插入寄存器片,当然这会导致额外的周期延迟。

使用寄存器片可以实现周期延迟(cycles of latency)和最大操作频率的折中;

使用寄存器片可以分割低速外设的长路径;

2.信号描述

信号名来源描述

ACLKsystem clock全局时钟信号

ARESTnsystem reset全局复位信号,低有效

全局信号

信号名来源描述

AWIDmaster写地址ID(用于区分该地址属于哪个写地址组)

AWADDRmaster写地址

AWLENmaster突发长度

AWSIZEmaster突发尺寸(每次突发传输的最长byte数)

AWBURSTmaster突发方式(FIXED,INCR,WRAP)

AWCACHEmaster存储类型(标记系统需要的传输类型)

AWPROTmaster保护模式

AWQOSmasterQoS标识符

AWREGIONmasterregion标识符(当slave有多种逻辑接口时标识使用的逻辑接口)

AWUSERmaster用户自定义信号

AWVALIDmaster写地址有效信号(有效时表示AWADDR上地址有效)

AWREADYmaster写从机就绪信号(有效时表示从机准备好接收地址)

写地址通道信号

信号名来源描述

WDATAmaster写数据

WSTRBmaster数据段有效(标记写数据中哪几个8位字段有效)

WLASTmasterlast信号(有效时表示当前为突发传输最后一个数据)

WUSERmaster用户自定义信号

WVALIDmaster写有效信号(有效时表示WDATA上数据有效)

WREADYslave写ready信号(有效时表示从机准备好接收数据)

写数据通道信号

信号名来源描述

BIDslave响应ID

BRESPslave写响应

BUSERslave用户自定义信号

BVALIDslave写响应信号有效

BREADYmaster写响应ready(主机准备好接受写响应信号)

写响应通道信号

信号名来源描述

ARIDmaster读地址ID

ARADDRmaster读地址

ARLENmaster突发长度

ARSIZEmaster突发尺寸(每次突发传输的byte数)

ARBURSTmaster突发类型(FIXED,INCR,WRAP)

ARCACHEmaster存储类型

ARPROTmaster保护类型

ARQOSmasterQoS标识符

ARREGIONmaster区域标识符

ARUSERmaster用户自定义

ARVALIDmaster读地址有效(有效时表示ARADDR上地址有效)

ARREADYslave写有效信号(有效时表示从机准备好接收读地址)

读地址通道信号

信号名来源描述

RIDslave读ID标签

RDATAslave读数据

RRESPslave读响应

RLASTslave有效时表示为突发传输的最后一个

RUSERslave用户自定义

RVALIDslave读数据有效信号

RREADYmaster主机就绪信号(有效时表示)

读数据通道信号

信号名来源描述

CSYSREQClock controller该信号有效时,系统退出低功耗模式

CSYSACKPeripheral device退出低功耗模式应答信号

CACTIVEPeripheral device外设申请时钟信号

低功耗接口信号

3.信号接口要求

3.1读写传输

3.1.1 握手过程

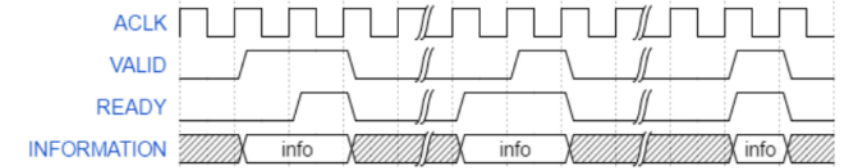

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。VALID信号表示地址/数据/应答信号总线上的信号是有效的,由传输发起方控制

READY信号表示传输接收方已经准备好接收,由传输接收方控制下图是几种握手机制:

VALID和READY的先后关系具有三种情况:

VALID先有效,等待READY有效后完成传输(VALID一旦有效后在传输完成前不可取消)

READY先有效,等待VALID有效后完成传输(READY可以在VALID有效前撤销)

VALID和READY同时有效,立刻完成传输此外,需要注意的是允许READY信号等待VALID信号再有效,即使从机准备好,也可以不提供READY信号,等到主机发送VALID信号再提供READY信号。对应的VALID信号不允许等待READY信号,即不允许VALID等待READY信号拉高后再拉高,否则容易产生死锁现象。

命令通道握手(读地址,写地址,写响应)

仅当地址等信息有效时,才拉高VALID,该VALID必须保持直到传输完成(READY置位)

READY默认状态不关心,仅当准备好接收时拉高READY数据通道握手(写数据和读数据)

突发读写模式下,仅数据信息有效时才拉高VALID,该VALID必须保持直到传输完成。当突发传输最后一个数据发送时拉高LAST信号

READY默认状态不关心,仅当准备好接收时拉高READY通道信号要求:

通道握手信号:每个通道有自己的xVALID/xREADY握手信号对。

写地址通道:当主机驱动有效的地址和控制信号时,主机可以断言AWVALID,一旦断言,需要保持AWVALID的断言状态,直到时钟上升沿采样到从机的AWREADY。AWREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言AWVALID,一个用来断言AWREADY);当AWREADY为高时,从机必须能够接受提供给它的有效地址。

写数据通道:在写突发传输过程中,主机只能在它提供有效的写数据时断言WVALID,一旦断言,需要保持断言状态,知道时钟上升沿采样到从机的WREADY。WREADY默认值可以为高,这要求从机总能够在单个周期内接受写数据。主机在驱动最后一次写突发传输是需要断言WLAST信号。

写响应通道:从机只能它在驱动有效的写响应时断言BVALID,一旦断言需要保持,直到时钟上升沿采样到主机的BREADY信号。当主机总能在一个周期内接受写响应信号时,可以将BREADY的默认值设为高。

读地址通道:当主机驱动有效的地址和控制信号时,主机可以断言ARVALID,一旦断言,需要保持ARVALID的断言状态,直到时钟上升沿采样到从机的ARREADY。ARREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言ARVALID,一个用来断言ARREADY);当ARREADY为高时,从机必须能够接受提供给它的有效地址。

读数据通道:只有当从机驱动有效的读数据时从机才可以断言RVALID,一旦断言需要保持直到时钟上升沿采样到主机的BREADY。BREADY默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。当最后一次突发读传输时,从机需要断言RLAST。

3.1.2 通道顺序

传输中,通道传输的先后有以下规定

写响应通道传输必须在写操作完成以后进行

读数据通道传输必须在读地址通道传输后进行

必须遵循一系列的状态依赖关系

通道握手信号的依耐关系

为防止死锁,通道握手信号需要遵循一定的依耐关系。VALID信号不能依耐READY信号。

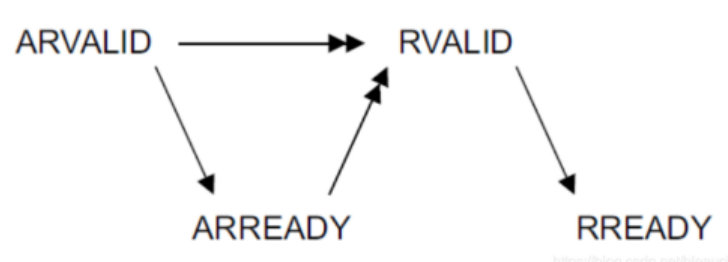

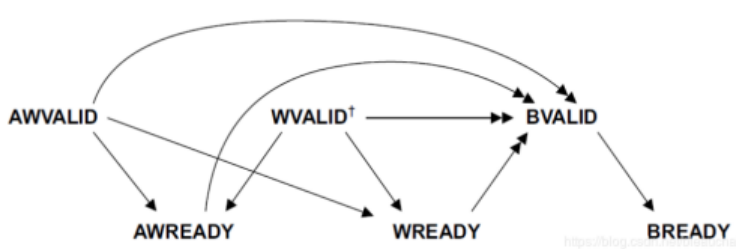

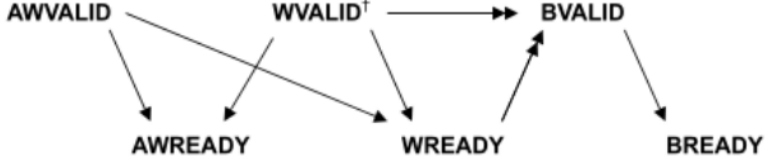

AXI接口可以等到检测到VALID才断言对应的READY,也可以检测到VALID之前就断言READY。下面有几个图表明依耐关系,单箭头指向的信号能在箭头起点信号之前或之后断言;双箭头指向的信号必须在箭头起点信号断言之后断言。

读传输握手依耐关系

上图为读操作的依赖关系,ARREADY可以等待ARVALID信号,RVALID必须等待ARVALID和ARREADY同时有效后(一次地址传输发生)才能能有效;

写传输握手依耐关系

从机写响应握手依耐关系

在AXI3中,写操作中唯一的强依赖关系是写响应通道BVALID,仅当WVALID和WREADY信号同时有效(数据传输完成)且WLAST信号有效(突发传输的最后一个数据传输完成)后才会被置位;

在AXI4中,定义了额外的依赖关系,即BVALID必须依赖AWVALID、AWREADY、WVALID和WREADY信号;

3.2时钟复位

时钟: 每个AXI组件使用一个时钟信号ACLK,所有输入信号在ACLK上升沿采样,所有输出信号必须在ACLK上升沿后发生。

复位: AXI使用一个低电平有效的复位信号ARESETn,复位信号可以异步断言,但必须和时钟上升沿同步去断言。

复位期间对接口有如下要求:

主机接口必须驱动ARVALID,AWVALID,WVALID为低电平;

从机接口必须驱动RVALID,BVALID为低电平;

所有其他信号可以被驱动到任意值。在复位后,主机可以在时钟上升沿驱动ARVALID,AWVALID,WVALID为高电平。

4.传输结构

4.1.地址通道数据结构

AXI总线是基于突发传输的总线,若主机要开始一次突发传输,需要传输一次地址和相关控制信号,之后从机自动计算地址(主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址),但一次突发传输的地址范围不能跨越4KB(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

(1)。突发传输信息

突发长度(AxLEN)

突发长度为每次突发传输的传输次数,范围限制1~16(AXI4增量模式1~256)。每次传输的突发长度为AxLEN[3:0] + 1(AXI增量模式AxLEN[7:0] + 1)

AXI3只支持1~16次的突发传输(Burst_length=AxLEN[3:0]+1);

AXI4扩展突发长度支持INCR突发类型为1~256次传输,对于其他的传输类型依然保持1~16次突发传输(Burst_Length=AxLEN[7:0]+1)。

对于回卷模式突发传输,突发长度仅能是2,4,8或16。

ARLEN[7:0]:读地址通道的突发长度接口

AWLEN[7:0]:写地址通道的突发长度接口burst传输具有如下规则:

wraping burst ,burst长度必须是2,4,8,16

burst不能跨4KB边界

不支持提前终止burst传输(可以通过关闭所有数据字段的方式使一段传输数据无效,但传输行为必须完成)

所有的组件都不能提前终止一次突发传输。然而,主机可以通过解断言所有的写的strobes来使非所有的写字节来减少写传输的数量。读burst中,主机可以忽略后续的读数据来减少读个数。也就是说,不管怎样,都必须完成所有的burst传输。

提醒:对于FIFO,忽略后续读数据可能导致数据丢失,必须保证突发传输长度和要求的数据传输大小匹配。

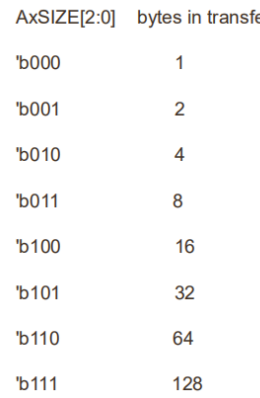

突发尺寸(AxSIZE)

突发尺寸为每次传输的byte数量,与突发传输的地址预测相关性很强。每次的突发尺寸不能超过数据通道的宽度;若突发尺寸小于数据通道宽度,需要指定哪些位数是有效的。突发尺寸为2^AxSIZE[2:0]

ARSIZE[2:0]:读地址通道突发尺寸

AWSIZE[2:0]:写地址通道突发尺寸突发类型(AxBURST)

AXI支持三种突发类型:

FIXED(AxBURST[1:0]=0b00):固定突发模式,每次突发传输的地址相同,用于FIFO访问;

INCR(AxBURST[1:0]=0b01):增量突发模式,突发传输地址递增,递增量与突发尺寸相关(传输过程中,地址递增。增加量取决AxSIZE的值。)

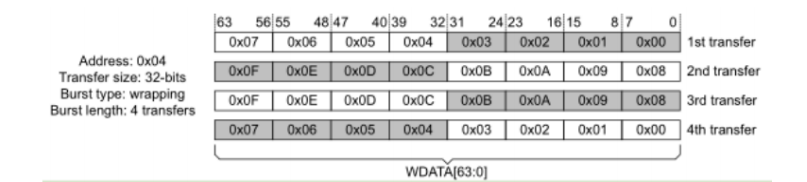

WRAP(AxBURST[1:0]=0b10):回卷突发模式,和增量突发类似,但会在特定高地址的边界处回到低地址处(传输地址不会超出起始地址所在的块,一旦递增超出,则回到该块的起始地址),突发传输地址可溢出性递增,突发长度仅支持2,4,8,16。传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。地址空间被划分为长度[突发尺寸*突发长度]的块,即回环边界等于(AxSIZE*AxLEN)。

(2)。存储类型(AxCACHE)

AXI4可支持不同的存储类型,AxCACHE[3:0]用于描述不同的存储类型,如下图所示

ARCACHE[3:0]AWCACHE[3:0]Memory type

00000000Device Non-bufferable

00010001Device Bufferable

00100010Normal Non-cacheable Non-bufferable

00110011Normal Non-cacheable Bufferable

10100110Write-through No-allocate

1110 (0110)0110Write-through Read-allocate

10101110 (1010)Write-through Write-allocate

11101110Write-through Read and Write-allocate

10110111Write-back No-allocate

1111(0111) 0111Write-back Read-allocate

10111111 (1011)Write-back Write-allocate

11111111Write-back Read and Write-allocate

4.2.数据通道数据结构

(1)。数据选通(WSTRB)

WSTRB的每一位对应数据中的8位(1字节),用于标志数据中的对应字节是否有效。即当WSTRB[n] = 1时,标志数据中WDATA[(8n)+7: (8n)]部分有效。

WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值, WVALID为高时,WSTRB为高的字节线必须指示有效的数据。

(2)。数据(xDATA)

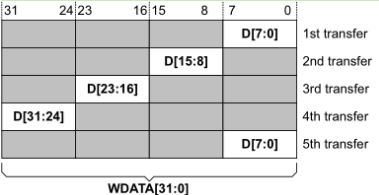

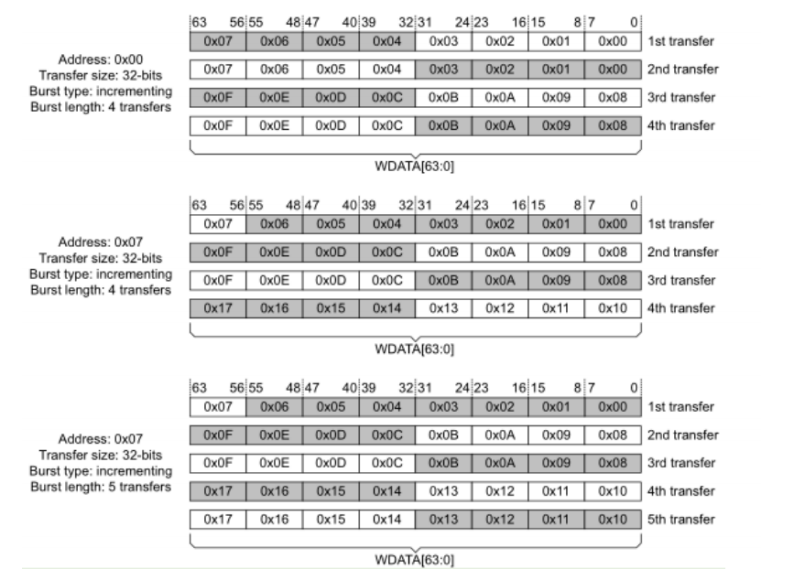

窄带传输(Narrow transfers)

当主机产生比它数据总线xDATA要窄的传输时,为窄带传输,每次使用的数据位数不同,由地址和控制信号决定哪个字节被传输:

固定地址的突发下,使用同一段数据信号线

在递增地址和包装地址的突发下,使用不同段信号线INCR和WRAP,不同的字节线决定每次burst传输的数据,FIXED,每次传输使用相同的字节线。

下图给出了5次突发传输,起始地址为0,每次传输为8bit,数据总线为32bit,突发类型为INCR。

窄传输示例

上图为地址递增突发下,在32位数据信号下使用8bit传输的窄带传输使用的位数图。第一次传输使用0~7位,第二次使用8~15位,依次递增;在第五次传输时回到开头使用0~7位。

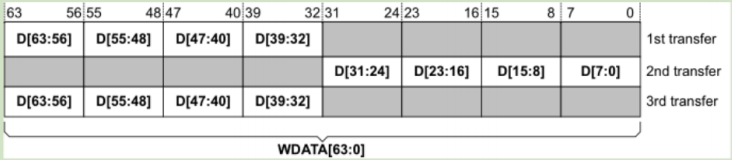

下图给出3次突发,起始地址为4,每次传输32bit,数据总线为64bit。

窄传输示例

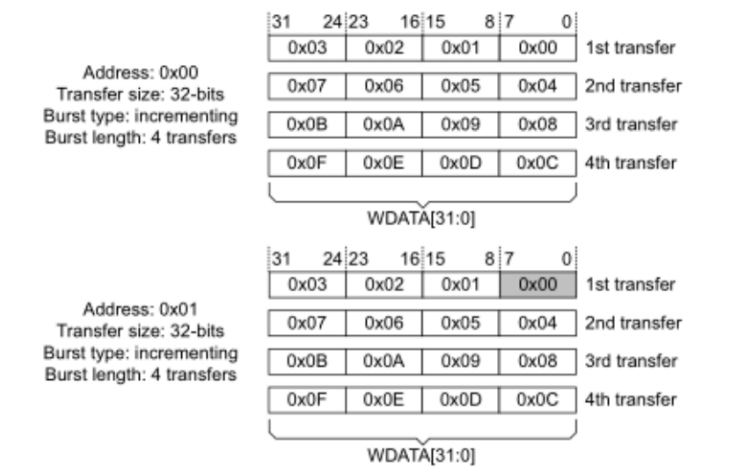

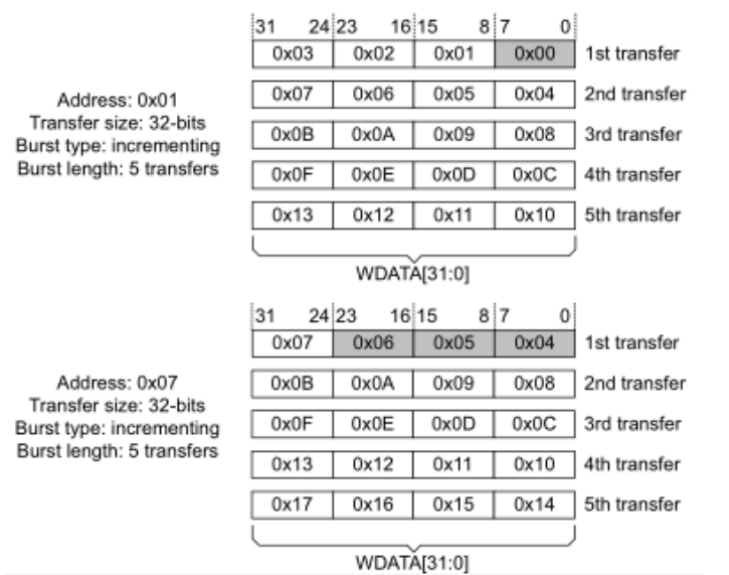

不对齐传输(Unaligned transfers)

AXI支持非对齐传输。在大于一个字节的传输中,第一个自己的传输可能是非对齐的。如32-bit数据包起始地址在0x1002,非32bit对齐。主机可以:使用低位地址线来表示非对齐的起始地址;

提供对齐的起始地址,使用字节线来表示非对齐的起始地址。当传输位宽超过1byte,起始地址不为数据总线硬件带宽(byte单位)整数倍时,为不对齐传输。不对齐传输的时候需要配合数据选通在第一次传输时将某几个byte置为无效,使第二次突发传输的起始地址(从机自动计算)为突发尺寸的整数倍。

对齐非对齐传输示例1-32bit总线

对齐非对齐传输示例2-64bit总线

对齐的回环传输示例

读写响应结构

读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输

BRESP[1:0],写传输

OKAY(‘b00):正常访问成功

EXOKAY(’b01):Exclusive 访问成功

SLVERR(‘b10):从机错误。表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR(’b11):译码错误。一般由互联组件给出,表明没有对应的从机地址。

5. AXI-Stream

AXI-Stream,是一种连续流接口,不需要地址线(类似FIFO,一直读或一直写就行)。对于这类IP,ARM必须有一个转换装置才能对内存映射方式控制,例如AXI-DMA模块来实现内存映射到流式接口的转换。

AXI-Stream适用的场合有很多:视频流处理;通信协议转换;数字信号处理;无线通信等。其本质都是针对数值流构建的数据通路,从信源(例如ARM内存、DMA、无线接收前端等)到信宿(例如HDMI显示器、音频输出等)构建起连续的数据流。这种接口适合做实时信号处理。

用户其实不需要对AXI时序了解太多,因为Xilinx已经将和AXI时序有关的细节都封装起来,官方IP和向导生成的自定义IP,用户只需要关注自己的逻辑实现即可

AXI4-Stream协议是一种用来连接需要交换数据的两个部件的标准接口,它可以用于连接一个产生数据的主机和一个接受数据的从机。当然它也可以用于连接多个主机和从机。该协议支持多种数据流使用相同共享总线集合,允许构建类似于路由、宽窄总线、窄宽总线等更为普遍的互联。

AXI4-Stream接口比较重要的信号线:

ACLK:时钟线,所有信号都在ACLK上升沿被采样;

ARESETn:复位线,低电平有效;

TVALID:主机数据同步线,为高表示主机准备好发送数据;

TREADY:从机数据同步线,为高表示从机准备好接收数据;这两根线完成了主机与从机的握手信号,一旦二者都变高有效,数据传输开始。

TDATA:数据线,主机发送,从机接收。

TKEEP:主机数据有效指示,为高代表对应的字节为有效字节,否则表示发送的为空字节。

TLAST:主机最后一个字指示,下一clk数据将无效,TVALID将变低。

TID,TDEST,TUSER均为多机通信时的信号,不予考虑。

利用AXI总线做转换,可以把PS里DDR4的内容以Stream形式发出去,例如以固定速度送往DA,完成信号发生器的设计;

ZYNQ的PS部分是ARM CortexA9系列,支持AXI4,AXI-Lite总线。PL部分也有相应AXI总线接口,这样就能完成PS到PL的互联。仅仅这样还不够,需要PL部分实现流式转换,即AXI-Stream接口实现。

Xilinx提供的从AXI到AXI-Stream转换的IP核有:AXI-DMA,AXI-Datamover,AXI-FIFO-MM2S以及AXI-VDMA等。

AXI-DMA:实现从PS内存到PL高速传输高速通道AXI-HP到AXI-Stream的转换;

AXI-FIFO-MM2S:实现从PS内存到PL通用传输通道AXI-GP到AXI-Stream的转换;

AXI-Datamover:实现从PS内存到PL高速传输高速通道AXI-HP到AXI-Stream的转换,只不过这次是完全由PL控制的,PS是完全被动的;

AXI-VDMA:实现从PS内存到PL高速传输高速通道AXI-HP到AXI-Stream的转换,只不过是专门针对视频、图像等二维数据的。

AXI总线和接口的区别:

总线是一种标准化接口,由数据线、地址线、控制线等构成,具有一定的强制性。接口是其物理实现,即在硬件上的分配。在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口,均为内存映射型AXI接口。

编辑:lyn

-

AMBA_AXI总线详解2014-04-18 1865

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3334

-

AXI接口协议详解2022-10-14 2961

-

AMBA AXI总线学习笔记2015-11-11 1329

-

从应用角度详解什么是AXI2018-07-13 12994

-

AXI 总线和引脚的介绍2018-01-05 11472

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7650

-

Xilinx zynq AXI总线全面解读2020-12-04 9428

-

你必须了解的AXI总线详解2020-10-09 9317

-

ZYNQ中DMA与AXI4总线2020-11-02 5372

-

AXI总线知识点快速学习2022-03-14 7920

-

AXI总线协议的简单知识2022-07-15 4359

-

AXI总线工作流程2023-05-25 2068

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 14190

-

NVMe简介之AXI总线2025-05-21 970

全部0条评论

快来发表一下你的评论吧 !