怎么解决有关于data保存时间的时序错误?

电子说

描述

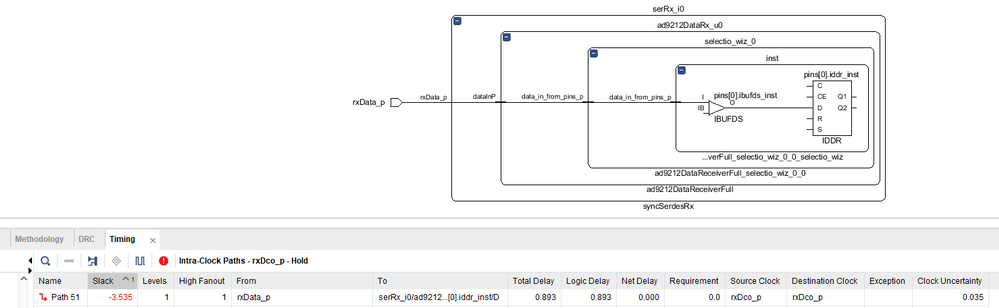

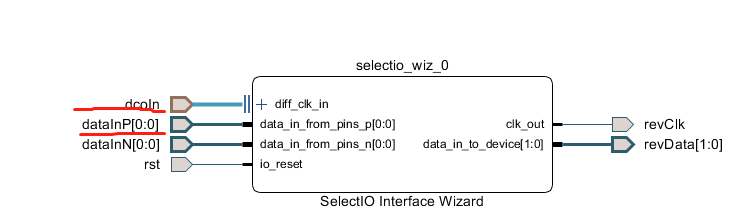

Q: 使用 zynq 器件, select io 解码串行数据, data 和 clock 直接进入, 未进行其他处理, 综合有关于 data 保存时间的时序错误, 请问什么问题? 实测接收功能基本正确

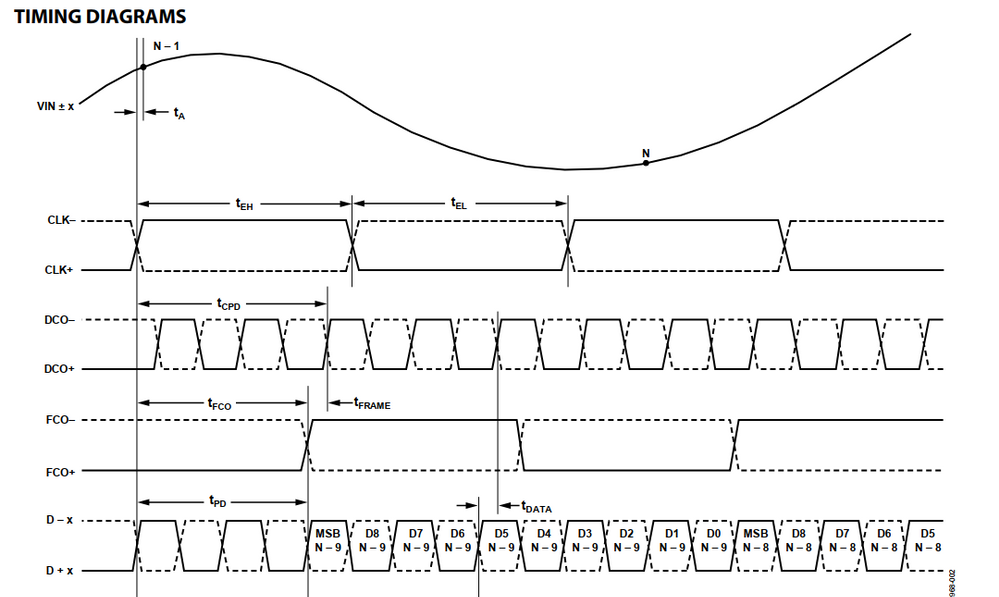

器件时序, 约束采用的是其中的 tframe = 1.3 - 1.9ns

约束:

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -min -add_delay -1.300 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -max -add_delay -1.900 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -min -add_delay -1.300 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -max -add_delay -1.900 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -min -add_delay -1.300 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -max -add_delay -1.900 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -min -add_delay -1.300 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -max -add_delay -1.900 [get_ports rxData_p]

A: 应该是 set_input_delay 约束写错了

参考 vivado language template 的话,这个 data 接口符合 source synchronous--》 center aligned --》 DDR 的模板

其中参数

dv_bre = dv_bfe = 1.3ns

dv_are = dv_afe = (1/2 period - 1.9)ns

所以约束里的

-max 值是(1/2 period - 1.3)

-min 值是(1/2 period - 1.9)

Language template在 vivado 图形界面 tools 菜单里。

关于 template 的介绍,可以先学习 inputdelay/output delay 的理论基础,结合实践琢磨一下,这套 template 使用的方法还是有点巧妙的

经验是通过时序图对比,找到最匹配的 template,确定里面对应参数的值,套用 template里面的约束模板就可以。

可以找出这个 source synchronous --》 centeraligned --》 DDR 模板,看里面的时序图跟用户手册里的时序图对比下

时序图里没有画出 data 有效数据跟无效数据(就是阴影部分)的范围,但 tFRAME 的值之所以是 1.3~1.9,就是因为 data 有有效数据跟无效数据范围的原因,把时序图的有效数据和无效数据范围画出来,就容易跟 template 里的时序图进行匹配了。

原文标题:本周一问 | Select io 解串行数据, 时序约束不通过问题

文章出处:【微信公众号:XILINX技术社区】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

电能质量在线监测装置的相序错误记录功能可以保存多久?2025-12-05 2203

-

关于C程序中10个与内存有关的常见错误2023-06-20 1110

-

FPGA时序约束:如何查看具体错误的时序路径2023-03-17 2278

-

FPGA时序约束一如何查看具体错误的时序路径2022-08-04 1156

-

关于data保存时间的时序错误2022-08-01 2061

-

TensorRT创建层时序缓存以保存层分析信息2022-05-13 4644

-

Verilog中四个基础的时序分析2021-08-25 5505

-

错误时钟偏移计算导致错误时序收敛的解决方案2020-12-24 7753

-

PCB的保存及烘烤时间说明2020-07-12 13249

-

功能,定时模拟和时序约束2020-03-16 1091

-

如何使用RPX文件保存和恢复时序报告2018-11-27 4284

-

关于NAND闪存有哪些观念是错误的?2018-08-30 1232

-

求助:labview 数据采集中关于数据和时间的保存问题2012-07-15 19713

-

设计的保存与时序文件的导出2009-11-19 431

全部0条评论

快来发表一下你的评论吧 !