RISC-V指令集的起源与发展历史

嵌入式技术

描述

本篇文章将介绍:①RISC-V 指令集的起源和发展历史,②讨论各种RISC-V CPU核、SoC设计平台和芯片产品的技术特点及选型要点,③重点阐述RISC-V 给嵌入式系统带来了益处,④RISC-V指令扩展的特点与安全应用。 本期第二篇推文还将介绍:⑤支持RISC-V开源和商业软件开发工具和操作系统的现况,最后⑥展望RISC-V 在教育和产业应用的发展趋势。

引言

过去二十年ARM在移动和嵌入式领域成果丰硕,IOT 领域正逐渐确定其市场地位,其他商用架构(如MIPS)逐渐消亡。ARM在进军Intel所在的x86市场,已经对传统PC和服务器领域造成一定压力。RISC-V 开源指令集的出现,引起了产业界的广泛关注,科技巨头很看重指令集架构(CPU ISA)的开放性,各大公司正在积极寻找ARM之外的第二选择,RISC-V成为必然选择。RISC-V 被全球范围内的大学陆续采纳为教材替代以前的MIPS和X86架构,政府和企业采纳RISC-V为标准指令集,开源的CPU核和SoC芯片不断涌现,生态环境逐渐丰富,开发者社区愈来愈活跃。

什么是RISC-V ?

一个CPU支持的指令和指令的字节级编码就是这个CPU的指令集(ISA),指令集在计算机软件和硬件之间搭起了一个桥梁。不同的CPU家族:X86、PowerPC和ARM,都有不同的ISA,RISC-V 是其中唯一的开源ISA。

RISC-V 是一种开源的指令集架构,它不是一款CPU芯片,甚至不是一个完整的指令集,它是指令集规范和标准。RISC-V 起源于加州大学伯克利分校,在2010年夏季Krste Asanovic教授带领他的两个学生Andrew Waterman , Yunsup Lee启动了3个月项目 ,针对X86和ARM 架构复杂和IP授权的原因,希望开发简化和开放的指令集架构。

RISC-V基金会创建于2015年,是一家非盈利组织。基金会董事会由Bluespec、Google、Microsemi、NVIDIA、NXP、UC Berkeley、Western Digital 7家单位代表组成,主席目前是Krste Asanovi 教授,基金会为核心芯片架构制定标准和建立生态,标准是公开免费下载。基金会旗下有400余家以上的付费成员,包括高通、NXP、阿里巴巴和华为等,RISC-V 基金会成员可以使用RISC-V商标,RISC-V 采用开源BSD 授权 ,任何企业、高校和个人都可以遵循RISC-V架构指南设计自己的CPU。RISC-V基金会总部从美国迁往瑞士,并于2020年3月完成在瑞士的注册,基金会更名为RISC-V国际基金会(RISC-V International Association)2。

十年来RISC-V 蓬勃发展,在CPU IP核,平台、SoC芯片和应用上都有了相当数量的发展,比如,应用上有西部数据设计的SSD和HDD控制器,内核是SweRV Core,中科蓝芯开发的蓝牙耳机芯片,嘉楠科技的K210 AIOT 芯片 ,南京沁恒电子的蓝牙MCU、32位通用MCU和高速接口的MCU,它们的内核都是RISC-V。

开源处理器RISC-V行业展览推荐

2021年9月1-3日,ELEXCON深圳国际电子展暨嵌入式系统展将专门打造『 RISC-V技术专区 』,汇聚行业内领先企业,全面展示RISC-V软硬件开发、RISC-V开发工具、RISC-V处理器应用、开源技术等新技术、新产品和新方案,迎接芯片行业发展的历史性机遇!

▼2021部分参展商

RISC-V指令集介绍

RISC-V的指令集使用模块化的方式进行组织,每个模块使用一个英文字母来表示。RISC-V最基本、也是唯一强制要求实现的指令集是由 I 字母表示的整数指令子集。使用该整数指令子集,便能够实现完整的软件编译器。其他的指令子集部分均为可选的模块,其代表性的模块包括M/A/F/D/C,比如 某款RISC-V 处理器内核是RV32IMAC,即代表实现了I/M/A/C 指令集,。RISC-V 指令集发展变化中,32I和64I 已经冻结,MAFDQC指令扩展是冻结了,指令集如32E,128I,LBJTPV和ZAM原子访问扩展还在开发中,指令集扩展是RISC-V的技术特色,广泛征求会员单位和产业界的意见是RISC-V发展合理的路径 3 。

表1 RISC-V 部分指令集描述

RISC-V 处理器核、SoC 平台 和SoC芯片

3.1 RISC-V 处理器核

在详细阐述RISC-V 处理器嵌入式开发之前,我们首先梳理一下几个概念:RISC-V 处理器核心(Core ,简称核),SoC 平台 和SoC芯片,以及开发者如何选择它们。自RISC V 架构诞生以来出,市场上已有数十个版本的 RISC -V 核和SoC芯片,它们中一部分是开源免费,某些是商业公司开发用于内部项目的 ,还有商业公司开发的 处理器核和平台。西部数据的SweRV架构(RV32IMC)是一个32bit顺序执行指令架构,具有双向超标量设计和9级流水线,采用28nm工艺技术实现,运行频率高达1.8GHz,可提供4.9 CoreMark/MHz的性能,略高于Arm的Cortex A15,已经用在西部数据的SSD和HDD 控制器上使用,SweRV项目是开源的项目。

典型的开源的RISC-V 核有Rocket Core,它是美国加州大学伯克利分校开发一个经典的RV64 设计,伯克利分校还开发一个BOOM Core,它与Rocket Core不同的是面向更高的性能。苏黎世理工大学(ETH Zurich)开发的Zero-riscy,它是经典的RV32 设计,苏黎世理工大学另外一款R15CY Core,可配置成RV32E,面向的是超低功耗、超小芯片面积的应该场景。由Clifford Wolf开发RISC-V Core PicoRV32,重点在于追求面积和CPU频率的优化。

开源的核用于研究和教学很合适,但是用于商业芯片设计还有许多工作要做。SiFive(赛昉科技)由Yunsup Lee创立,他也是RISC-V的创始人之一。2017年公司发布首个RISC-V核和SoC平台家族,以及相关支持软件和开发板,这些芯片包括采用28纳米制造技术的64位多核CPU U500,支持Linux操作系统,以及采用180纳米制造技术的多外设低成本IoT处理器核 E300。开发RISC-V处理器核的厂商还包括Codasip、Syntacore、T-Head(平头哥) Andes (晶芯科技),以及创业公司芯来科技和优矽科技。

3.2 RISC-V SoC平台

知名的RISC-V 处理器SoC 平台有瑞士理工大学的PULPino ,开源项目LowRISC

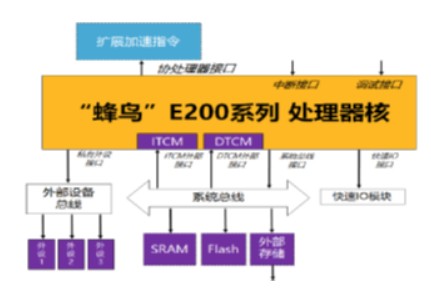

以及Rocket Chip - 伯克利分校基于Chisel开发的开源SoC生成器。芯来科技胡振波发起的蜂鸟E200开源项目4,配合他的图书,是在国内知名度非常高的开源软核SoC平台之一。在64位SoC 平台方面,平头哥半导体发展很快,先后推出了玄铁C906单核和玄铁C910多核高性能64位 RISC-V 处理器。

图1 蜂鸟E200 RISC-V 处理器

3.3 RISC-V SoC 芯片

RISC-V 处理器SoC芯片近年发展迅速,知名度较大的通用性SoC芯片有兆易创新开发的GD32VF103 MCU 芯片, 该芯片基于芯来Bumblebee 内核(RV32IMAC)。GD32VF103系列提供了108MHz的运算主频,16KB到128KB的片上闪存和6KB到32KB的SRAM,有4个16位通用定时器,2个16位基本定时器和2个多通道DMA控制器。GD32VF103 MCU全新设计的中断控制器(ECLIC)提供了多达68个外部中断并可嵌套16个可编程优先级,以增强高性能控制的实时性。

GD32VF103 MCU开发板有GD32VF103V-EVAL全功能评估板以及GD32VF103-START入门级学习板。还有芯来科技开发RV-START ,以及Sipeed Longan Nano 开发板 5 和IAR 最新的 IAR RISC-V GD32 EVAL 评估套件6,见下图。

图2 IAR RISC-V GD32V 评估套件

嘉楠科技K210 是一个AIOT SoC 芯片,K210 包含 RISC-V 64 位双核 CPU,采用双RV64 GC Core,MAFD ISA 指令标准扩展。K210 包含KPU 通用神经网络处理器,内置卷积可以对人脸或物体进行实时检测,K210 的FFT 加速器是用硬件的方式来实现7 。

NXP RV32M1 集成了4个核: RISC-V RI5CY 核, RISC-V ZERO-RISCY 核, ARM CortexM4 核和 ARM Cortex-M0+ 核。从专业人士视角看,RV32M1 更像是工程实验样品,用来给开发者评估使用,为此NXP 为开发者创建https://open-isa.org/ 社区,维护工具链和软件生态,通过赠送开发板和举办大赛为开发者学习RISC-V 嵌入式开发提供了便利,在早期市场培育期发挥重要的作用 8,见下图。

图3 NXP RISC-V 织女星开发板

Microchip PolarFire SoC芯片是一款低成本, 多核RISC-V SoC FPGA,包含了4个 64-bit RV64GC RISC-V 应用核,可运行Linux, 一个单核 RV64IMAC 做实时和监控任

务, 这是一款适合工业控制和物联网应用的开发平台。

3.4 RISC-V核、平台和芯片究竟该如何选择呢?

近期关注RISC-V处理器研究、开发和教学的人士开始增多,建议:

(1)。芯片设计者可选择RISC-V 核 和SoC 平台 构建自己的芯片。比如,使用 PULPino 平台开发 SoC 芯片,内核使用 RI5CY和Zero-risky,国内企业和高校研究项目都有在使用。

(2)建议嵌入式和物联网系统开发者使用 RISC-V SoC 芯片。比如,选择GD32VF103 系列 MCU芯片做嵌入式项目开发,GD32VF103有多款开发板和开发工具链支持。AIOT 应用可以选择 K210 ,K210开发软件SDK 非常成熟,支持freertos 和裸机,最近Linux 5.8 正式将K210 RISC-V 纳入主线, K210 已经成功应用在人脸识别和智能抄表等机器视觉和机器听觉领域。

(3)高校和研究机构可以选择开源RISC-V 核 在FPGA 平台上进行计算机体系架构、操作系统 ,编译技术以及嵌入式系统教学和研究工作。比如,Arty FPGA 开发板上实现一个 SiFive 开源Freeedom E310 微控制器的技术已经非常成熟,相应软件工具链支持的很好 9, 见下图。

图4可以配置RISC-V 软核的Arty FPGA 开发板

RISC-V 给嵌入式系统带来的优势

我们上一节讨论了RISC-V 处理器核、平台和芯片 。很明显,嵌入式与物联网以及AIOT 是RISC-V 最活跃的应用市场,RISC-V给嵌入式系统带来许多优势,我仅就以下三点做个阐述:

(1)开源和免费。开源是新的经济方式,是成功的商业之道, 也学生和工程师学习最佳途径。ISA开源意味着开发者可以针对特定应用场景,创造自己的芯片架构,免费则可以降低芯片设计门槛,让草根开发者进入芯片设计领域。

(2)简单和灵活。RISC-V基础的指令集有50条,模块化的4个基本指令集能让设计者。开发出很简化的RISC-V CPU,代码密度低功耗很小的芯片,覆盖从8051-ARM A系列 各种嵌入式处理器。

(3)高效和安全。RISC-V 通过预留编码空间和用户指令支持扩展的指令集,通过指令集扩展实现运算加速和物联网安全。物联网保护的一种通用的途径是分层,分为信任执行环境(TEE)和非信任环境。RISC-V ISA的设计将TEE硬件要求定义为标准规范的一部分,可以在任何RISC-V 芯片上实现,包括配置物理内存保护(PMP), PMP类似 ARM处理器内存保护单元(MPU)。

HEX-FIVE 公司在RV32 Core 做了IoT 分区保护的应用案例 10,见下图4,软件可参考开源代码https://github.com/hex-five/multizone-secure-iot-stack 。从图中我们可以看到,SOC 芯片是X300 Bitstream ,采用是开源Rocket RV32IMAC 内核。Digilent ARTY A7 FPAG开发板 ,配有以太网。软件上 MultiZone 安全可信执行环境 配置成4区:

(1) Zone 1 区,运行FreeRTOS 有三个任务,分别是CLI任务, PWM LED任务,机器人手臂控制任务。

(2) Zone 2区,移植以太网,运行 PicoTCP 软件协议,TCP信道进行了TLS 加密。

(3) Zone 3区: 运行WolfSSL TLS 1.3 ,存储信任根,加密密钥,密码以及受保护的文件等放在这个区域。

(4) Zone 4区,UART 本地终端应用。

图5 MultiZone Security IoT Stack RISC-V 平台应用案例

更多技术干货

更多内容关于:⑤支持RISC-V开源和商业软件开发工具和操作系统的现况,最后⑥展望RISC-V 在教育和产业应用的发展趋势。请见姊妹篇推文!

责任编辑:tzh

-

浅谈RISC-V指令集架构的来龙去脉2020-01-24 7261

-

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集2024-01-31 871

-

RISC-V指令集说明哪里有?2024-04-30 2409

-

RISC-V基础整数指令集2024-07-27 1040

-

risc-v的发展历史2024-07-29 1686

-

RISC-V指令集的特点总结2024-08-30 1210

-

RISC-V和arm指令集的对比分析2024-09-28 1741

-

RISC-V的指令集位宽的几点学习心得2024-10-31 1870

-

RISC-V指令集概述2024-11-30 1165

-

RISC-V指令集架构微控制器相关知识2021-12-16 1468

-

RISC-V 的起源与发展,以及学习资料推荐2022-03-11 4260

-

RISC-V 发展2023-04-14 1096

-

印度确立RISC-V为国家指令集 中国CPU指令集还在孤芳自赏2017-12-19 8224

-

简单讲讲RISC-V指令集CPU的参数2022-08-07 5082

-

一个基于精简指令集原则的开源指令集架构RISC-V2023-01-30 4794

全部0条评论

快来发表一下你的评论吧 !