RISC-V快速入门指南

嵌入式技术

描述

近年来,整个电子行业似乎都为 RISC-V 感到疯狂。但什么是RISC-V?您将能如何参与其中?如果您曾经阅读过相关资料,您会知道它是一种处理器,并且目前市场上已经有相关芯片可以使用。您可能还知道它是“自由和开放的”,主要是因为它令人兴奋并拥有庞大的粉丝群。

让我们拨开迷雾,找出这项技术的真正意义所在。

首先,我们必须弄清楚,RISC-V是一种指令集体系结构或ISA ,而不是处理器。这意味着,如果您选择基于RISC-V ISA,则RISC-V背后的社区已经对处理器设计的工作方式进行了描述。当我们说“设计”时,实际上是指创建具有所有寄存器,累加器,数学运算,存储器总线以及其他所有部件的处理器。

ISA记录了受支持的操作,内存寻址功能,堆栈的功能以及发生中断时的情况,仅举几例。关于支持的操作,它说明了使用多少位对指令进行编码以及使用哪些位对所需的任何操作数的源进行编码。

RISC V让人兴奋的原因在于其ISA是免费开放的。开放意味着任何人都可以为它的发展做出贡献,而自由意味着它不需要花钱就可以使用。

但是,就像Arduino电路板设计是开放和免费使用的一样,这并不意味着不需要花钱就可以买到一块电路板,并且同样适用于构建基于RISC-V的理想设计。

RISC-V在竞争什么?

每个处理器都有一个ISA;几乎所有专利都是专有的,而其实有些是可许可授权使用 的。Microchip生产的器件使用8位和16位PIC处理器,并且在某处有一个ISA来描述它们。这些是专有的内核,属于Microchip并在其微控制器中出售。

如果您想构建自己的微控制器,则可能要看一下Arm和MIPS。这些专有核心可作为知识产权(IP)许可。他们背后的企业将把ISA转换为良好的处理器设计,开发支持它们的工具,创建其他相关基础结构并向您收取使用费。但这些ISA面临的挑战是这些选项不能完全满足您的期望。

您的新应用可能需要非常快地执行一项任务(例如加密),但功耗却很小。潜在的可许可处理器IP可能以100条指令执行您的任务。如果现在希望降低功耗,则需要找到专门用于低功耗的硅制造设施(fab),这可能比“通用”制造工艺昂贵,从而导致您难以置信的产品对于您的目标市场而言过于昂贵。

但是,您可能会有一些聪明的工程师,可以通过为处理器创建新指令来优化代码的执行时间,但是由于ISA是专有的,因此您不允许对其进行修改。因此,您陷入了需要用制造方法解决的处理器性能问题。稍后对此进行更多讨论。

开箱即用的RISC-V

RISC-V的出现,基本解决了上述问题。当前,他们定义了32位和64位ISA,并且也正在使用128位ISA。这些基本定义被命名为RV32I和RV64I。如果选择RV32I,将有49条指令供您使用。顺便说一句,“ I”代表“整数”。其中包括所有基本的整数算术和逻辑指令(ADD,SUB,AND,OR,XOR),移位,比较,跳转和链接,以及一些系统指令。如果您希望支持紧凑代码,则可能对“ C”选项感兴趣。这提供了16位指令编码,类似于Arm Thumb模式。也可以添加乘法和除法(M),原子(A)和浮点(F,D和Q)指令。

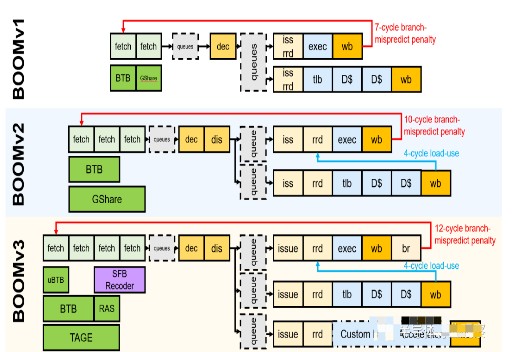

下一步是根据硬件描述语言[(HDL)(例如VHDL或Verilog)中所选选项的规范来设计处理器内核。由于这并不容易,所以这就是社区所关注的方面。设计处理器需要很多技巧,因此有很多人和企业为您提供现成的设计。如果您想走“免费”路线,由ETH Zurich和Bologna大学创建。他们的CV32E40P RV32IM C实现可在GitHub 上找到,如果您想了解如何实现这种的方法,指令解码器也在其上。另一个实现是BOOM项目,这是由加利福尼亚大学伯克利分校开发的高性能且可参数化的体系结构研究核心。

图1:使用RISC-V实现的 BOOM项目 开发过程。

如果您急于需要一些支持,那么您将需要花一些钱,并从SiFive 之类的企业处获得实现的许可。它们具有可用的32位和64位设计,你们也可以对其进行定制。

如何试用RISC-V?

尽管RISC-V已经存在了一段时间,但没有太多可供我们测试的芯片。在行业背景下,RISC-V还是相对较新的。如果您热衷于微控制器,那么您将了解整个行业中大多数人是如何采用Arm的,而不再使用其专有的内核。那是一项战略性的长期投资。现在转向RISC-V只会节省支付给Arm的特许权使用费,并且不会给用户带来什么好处。他们还需要使他们的开发团队在RISC-V上达到最新,将其与所有其他IP(模拟,计时器,总线,接口,内存)集成,更新开发IDE,编译器,调试器等。

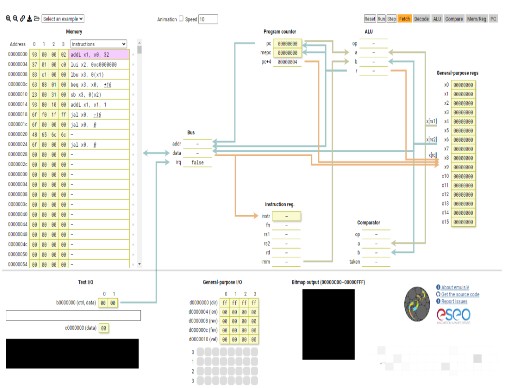

如果您拥有Seagate或Western Digital硬盘驱动器,则可能已经在“使用” RISC-V 。但是您实际上是想在此内核上运行代码,而不仅仅是拥有使用它的产品。最快的方法是使用模拟器,例如ESEO提供的emulsiV ,该模拟器 使用其RISC-V核心实现“ Virgule”( 图2 )。

图2:使用emulsiV模拟器,任何人都可以在其Web浏览器中试用RISC-V。

除了处理器之外,模拟器还提供一些指令输入/输出,位图输出和一些通用I / O(GPIO)。七个示例涵盖了基础知识,从添加和输出ASCII文本到控制GPIO。“ animation”(动画)选项(复选框的顶部中间)是一个不错的选择,它显示了所有数据的来源以及代码执行时的去向。

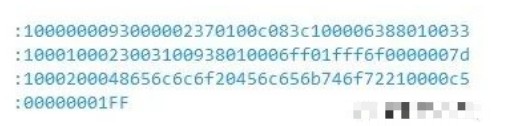

如果愿意,你可以尝试将 清单1中 的代码复制到文本编辑器中,然后将文件另存为program.hex,然后将其上传到模拟器中。

清单1:用于emulsiV模拟器的原始HEX代码,将其保存并上传为program.hex。

如果您想以Arduino格式体验RISC-V,则可通过CrowdSupply 获得HiFive1 RevB 。它使用SiFive FE310-G002微控制器。这是一款仅具有数字外设(I 2 C,UART,SPI,PWM,GPIO)和某些SRAM的准系统设备,依靠片外QSPI闪存实现非易失性存储。该评估板包括Wi-Fi和蓝牙模块以及用于USB调试的Segger J-Link。

性能范围的另一端是Microchip PolarFire SoC 它将四个64位RISC-V内核与一个FPGA一起放置。这提供了一个高度可配置的平台,该平台可以运行Linux,同时支持硬实时应用程序。

如何自定义我的RISC-V?

之前,我们提到RISC-V的实际好处是您可以调整指令集以满足个别应用的需求。这意味着,如果找到的处理器能满足95%的需求,那么则可以添加一些漂亮的额外功能来实现剩余的5%。假设您的应用大量使用ChaCha 流密码,如Imperas的应用笔记中所述,Imperas是另一种提供验证,分析和性能分析工具的RISC-V播放器。

您已经在RISC-V内核上运行了ChaCha实现,并且注意到它正在消耗大量的处理时间。您不仅希望缩短执行时间,而且还希望受益于由于执行时间减少而带来的功耗下降,也许可以使用它进入低功耗睡眠模式。

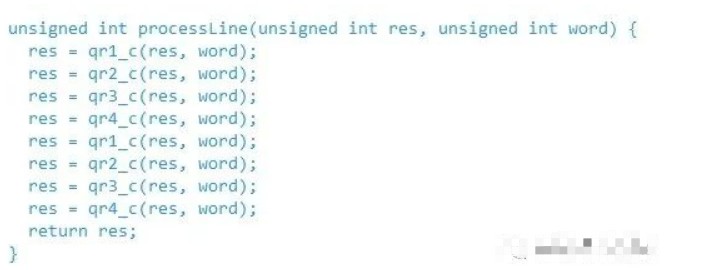

清单2:实现ChaCha流密码的C代码。

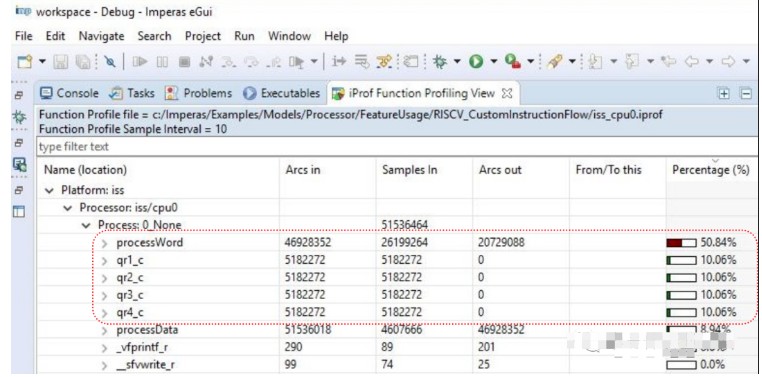

代码( 清单2 )在称为“quarter rounds”的步骤中广泛使用XOR和旋转指令,为此已编写了四个C qrX_c()函数。甲ProcessLine从()函数调用这四个函数来执行加密。对执行时间的分析表明,处理器在此任务上花费了大约55%的时间,其中大约32%的时间分布在quarter-round 功能中( 图3 )。

图3:使用标准C编译的代码,ChaCha密码流需要大约55%的处理器时间。

使用RISC-V,我们可以简单地实现四个专用的quarter-round指令,这些指令在一个周期内执行,而不必依赖C编译器强制生成的代码。这是因为ISA中保留了一部分,用于自定义说明。

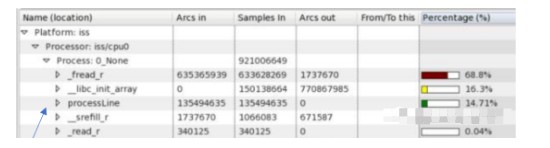

最初,我们可以将指令添加到RISC-V设计中,并用C编写该指令的实现。这可以模拟新指令以测试其功能,并检查性能是否可以提高。在这种情况下,借助定制的RISC-V内核上可用的专用quarter-round指令,processLine()函数所需的可用处理器性能不到15%( 图4)。 )。如果这被认为是成功的,则开发团队可以在Verilog中开发指令的硬件实现。

图4:通过使用专用的,新开发的指令,ChaCha密码流处理器的负载下降到不足15%。

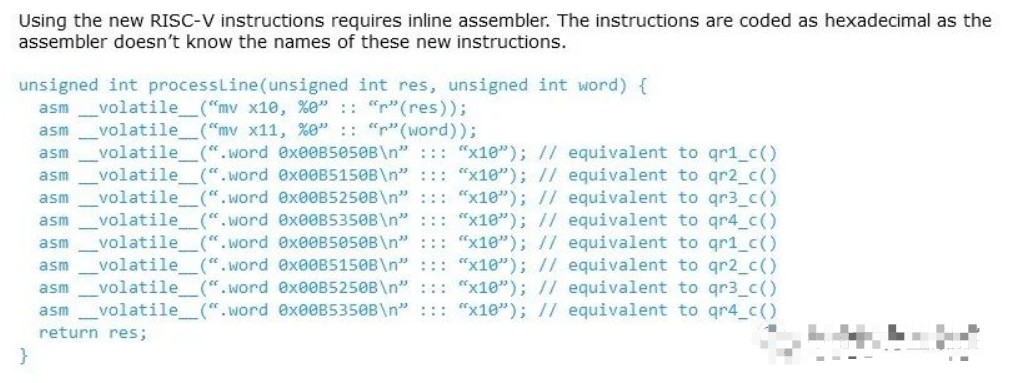

遗憾的是,使用新指令并不像重新编译C代码那样容易( 清单3 )。修改RISC-V编译器以利用新指令是一项巨大的工作。取而代之的是,使用内联汇编器以与手工优化代码相同的方式调用十六进制编码的指令。

清单3:使用新的RISC-V指令。

我该如何对此贡献?

如果您有兴趣帮助RISC-V的持续开发,那么您很幸运!RISC-V International 是负责开发和推广RISC-V的所有事物的值得信赖的组织( 图5 )。个人可以作为社区成员加入,或者,如果您想在此基础上发展职业,那么有很多企业和大学都在积极参与其中。

图5:RISC-V International的官方徽标,该徽标促进和支持ISA的开发。

如果您期望各种各样的RISC-V微控制器进入市场,您可能会感到失望。GigaDevice提供了一些设备,还有俄罗斯供应商针对智能电表市场提供的另一种设备。但是,他们表现欠佳。因为Arm对大型企业根深蒂固,即使没有处理器使用费的加工商的财务利益,初创企业也将难以在这个饱和的市场中竞争。

取而代之的是,我们更有可能看到RISC-V用于专门的应用,在这些应用中,定制内核的能力带来了巨大的好处,例如超低功耗。

RISC-V面临着有关向中国授予技术许可的问题,它正在证明是从美国获取IP企业的一种流行替代方案。阿里巴巴宣布以16纳米制程制造的16核,2 GHz,64位RISC-V ,并表示正在考虑将该核用于服务器基础架构。最后,欧洲处理器倡议一直在研究异构架构,这些架构可以同时看到Arm和RISC-V(或其他内核)。这里的目的是通过为多核设计中的每个计算难题使用最佳处理器来获得两全其美的效果。

RISC-V并不是首次免费开放尝试使用处理器IP,但是迄今为止,它是最成功的尝试。凭借其悠久的历史,灵活性,开放的态度,学术界的兴趣以及广泛的行业支持,这项技术将在整个职业生涯中陪伴一代或更多的工程师。

责任编辑:tzh

-

RISC-V MCU入门2024-11-27 1563

-

rIsc-v的缺的是什么?2024-07-29 1215

-

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?2024-04-28 2297

-

RISC-V MCU智能配置程序用户指南2024-01-30 454

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 854

-

RISC-V vector intrinsic编程入门指南2023-06-19 5973

-

《RISC-V体系结构编程与实践》试读2023-04-03 1334

-

RISC-V-Reader-Chinese-v2p1 RISC-V手册(中文) RISC-V开源指令集的指南2022-04-22 13043

-

从零开始写RISC-V处理器2022-03-17 3292

-

如何入门RISC-V嵌入式2022-01-07 1270

-

如何促进RISC-V loT行业应用的发展2021-06-23 3043

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4408

-

基于 RISC-V 的微控制器入门指南2020-08-21 2398

全部0条评论

快来发表一下你的评论吧 !