浅析在PYNQ框架下可视化的验证HLS算法实现

电子说

描述

在上篇文章中,我们发布了热门 HLS小橙书-pp4fpgas 的第二次校订。文中提到的习题案例现均已集成到 PYNQ 框架中,特向大家分享。

那么这些案例通过 PYNQ 框架会带来哪些便利呢?本文给大家做一个简单的类比:

过去

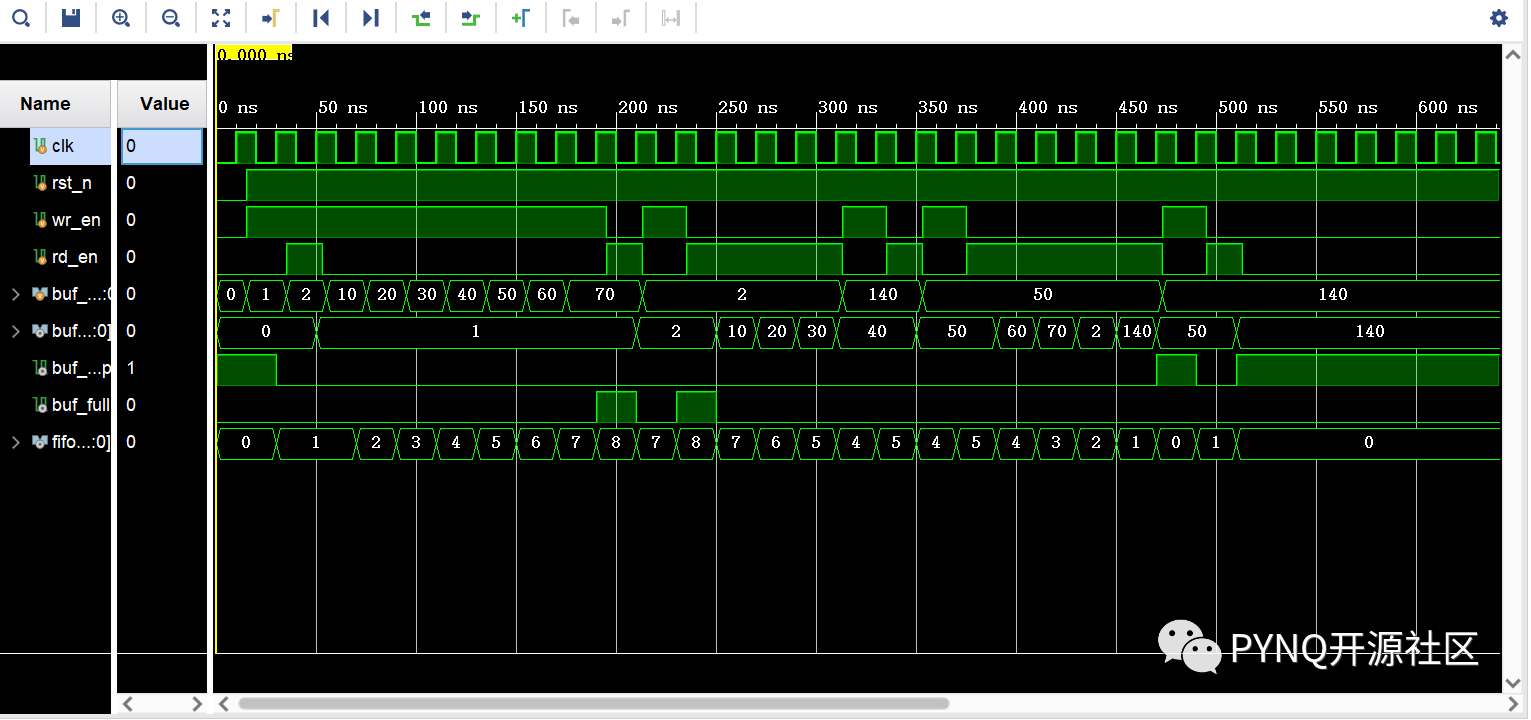

在完成项目的 HLS 优化之后,若要对其进行功能正确性的验证,通常我们先对设计进行仿真,这样比较方便看到设计的波形。但大型设计往往对运行的平台有较高的要求,同时 co-simulation 等软件层面的仿真并未使项目中的运算在硬件上运行,所得的延时等指标仍较真实值有一定差距。

当然我们也可以在设计中插入 ILA 或者借助逻辑分析仪等信号处理仪器进行实际硬件电路的观测。但专用仪器往往在实验室才能获取,且较为昂贵,因此给整个开发流程带来了极大的不便。

现在

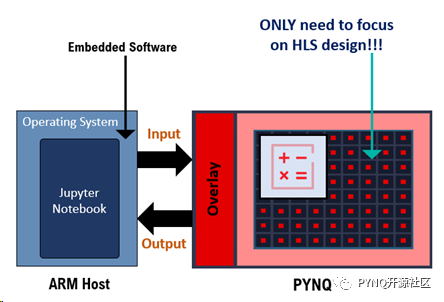

PYNQ 框架在测试中可以理解为:

在 ARM 处理上运行了一套利用 Jupyter Notebook 和 Python 构建的软件测试激励产生和结果显示的框架。

在 FPGA 上利用部分资源构建了一套时序精准的测试接口。

这样用户可以方便的完成测试激励产生和显示,同时可以实时的观测结果。尤其是对于此次 pp4fpgas 的数字信号处理案例,我们可以在 Jupyter Notebook 上非常直观的观测到时域频域的转换,信号波形等等。用户只需关注 HLS 设计即可。通过 PYNQ,可编程逻辑电路将作为硬件库导入并通过其 API 进行编程,其方式与导入和编程软件库基本相同。

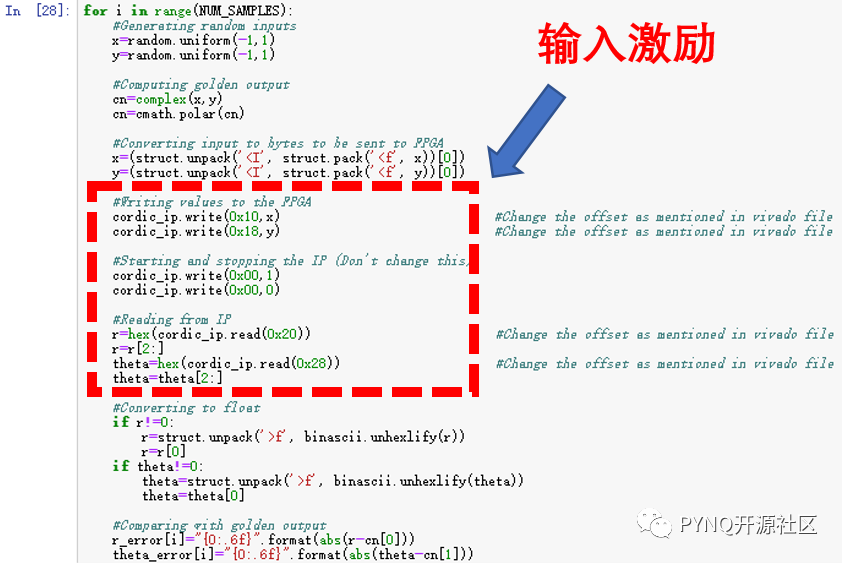

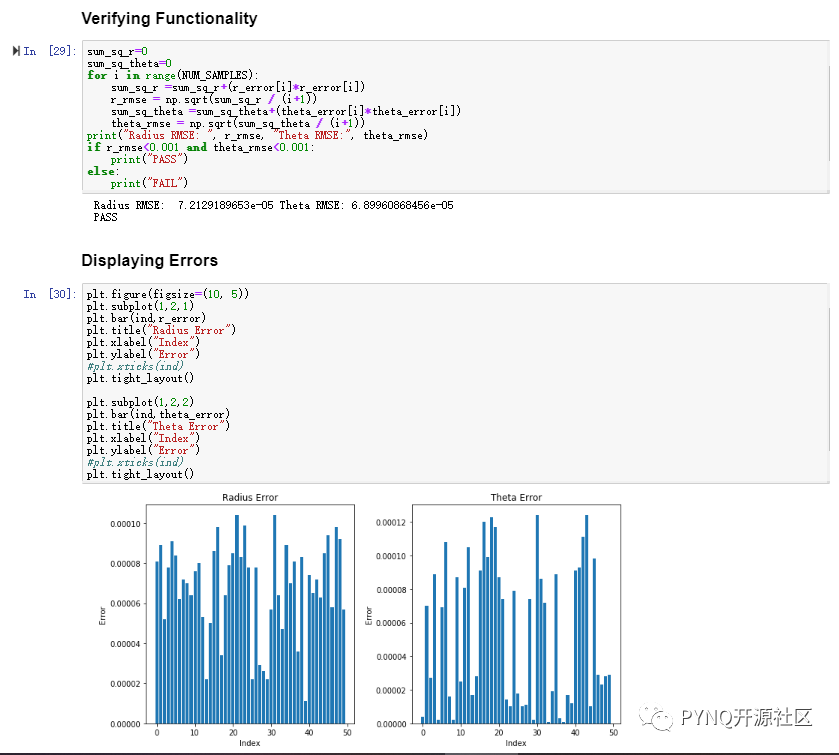

以 CORDIC 算法为例,首先我们需要对 HLS 优化后的 CORDIC 算法生成IP核,随后就可以在PYNQ 框架内,通过内存映射 I/O 与 ARM 处理器的 IP 进行通信。如上图所示,我们仅需创建一个 Jupyter Notebook,编写 Python 代码给 IP 发送数据,执行该核心,就可以在 Notebook 中得到通过硬件计算出的答案,从而完成验证。

包括 CORDIC 在内,pp4fpgas目前配套了7个 project 练习,覆盖了许多信号处理领域的重要内容,对提高 HLS 的运用能力,增加对 HLS 的理解十分有帮助。Project 内容如下:

FIR Filter Design

CORDIC

Phase Detector

Discrete Fourier Transform (DFT)

Fast Fourier Transform (FFT)

OFDM Receiver

FM Demodulator

编辑:lyn

-

新手求助,HLS实现opencv算法加速的IP在vivado的使用2017-01-16 6022

-

在MCFW框架下,有OSD(SWOD)的图像叠加的算法在DSP端执行,请问这样的算法是不是应该符合Ti的XDM标准?2018-05-25 2524

-

可视化MES系统软件2018-11-30 3406

-

如何把AD中非可视化区域物件移到可视化区域?2019-09-10 2487

-

三维可视化的应用和优势2020-12-02 2779

-

VR与三维可视化在电厂中的作用2020-12-03 1816

-

PYNQ框架下如何快速完成3D数据重建2021-01-07 1934

-

如何在Ubuntu下实现可视化代码跟踪调试2021-12-14 1169

-

VegaGIS可视化系统的设计和实现2009-04-10 638

-

MapReduce框架下的Skyline结果优化算法_马学森2017-03-19 883

-

柔性动态可视化在医学图像可视化中应用2018-01-05 1114

-

管线可视化管理怎么实现呢?2020-03-11 1702

-

基于IIoT-EDDP开源平台和PYNQ软件框架的电机控制2020-10-30 5837

-

Charts.css是用于数据可视化的新的开源框架2021-04-13 2828

-

如何实现园区大屏可视化?2024-06-19 1294

全部0条评论

快来发表一下你的评论吧 !