浅谈一种折迭共源共栅运算放大器的设计

电子说

描述

本文介绍了一种折迭共源共栅的运算放大器,采用TSMC0.18混合信号双阱CMOS工艺库,用HSpice W-2005.03进行设计仿真,最后与设计指标进行比较。

1 引言

随着集成电路技术的不断发展,高性能运算放大器广泛应用于高速模/数转换器(ADC)、数/模转换器(DAC)、开关电容滤波器、带隙电压基准源和精密比较器等各种电路系统中,成为模拟集成电路和混合信号集成电路设计的核心单元电路,其性能直接影响电路及系统的整体性能,高性能运算放大器的设计一直是模拟集成电路设计研究的热点之一,以折衷满足各种应用领域的需要。

许多现代集成CMOS运算放大器被设计成只驱动电容负载。有了这样只有电容的负载,对于运放放大器,就没有必要使用电压缓存器来获得低输出阻抗,因此,有可能设计出比那些需要驱动电阻负载的运算放大器具有更高速度和更大的信号幅度的运算放大器。通过在一个只驱动电容负载的运算放大器输出端只有一个高阻抗节点,可以获得这些提高,这些运算放大器在其他节点看到的导纳与MOS管的跨导在一个量级上,因此他们具有低阻抗。

有了所有相对低阻抗的内部节点,运算放大器的速度得到最大化,这里还应该提到的是:这些低节点阻抗使得所有节点而不是输出节点的电压信号降低,然而,各种晶体管的电流信号可能非常大,对这些运算放大器,应看到补偿通常是由负载电容达到的,这样,当负载电容变大,运算放大器通常变得更稳定也更慢,这些现代晶体管最重要的参数之一是他们的跨导值(即输出电流和输入电流的比)。因此,一些设计者称这些现代运算放大器为跨导运算放大器或者运算跨导放大器(OTA)。

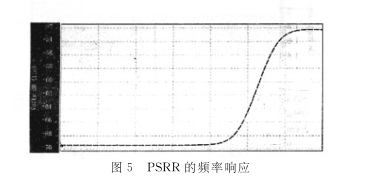

在各种OTA结构中,折叠共源共栅运放结构的运算放大器可以使设计者优化二阶性能指标,这一点在传统的两极运算放大器中是不可能的,特别是共源共栅技术对提高增益、增加PSRR值和在输出端允许自补偿是有用的。这种灵活性允许在CMOS工艺中发展高性能无缓冲运算放大器,目前,这样的放大器已被广泛应用无线电通信的集成电路中。

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC,AC及瞬态分析,最后与设计指标进行比较。

2 电路结构分析

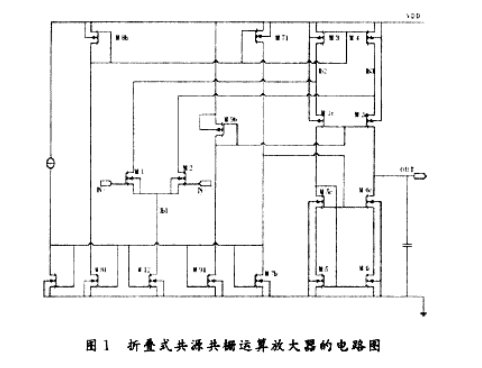

如图1所示,该图是一个差动输入单端输出设计,他的基本思想是将共源共栅MOS管应用于输出差动对中,但使用的MOS管与输入级中使用的那些MOS管类型相反,例如,图中由M1和M2组成的差动对MOS管为N沟道。而由M1c和M2c组成的共源共栅MOS管是P沟道MOS管,这种相反类型MOS管得安排允许这个单增益级放大器的输出在相同偏置电压水平上作为输入信号。应该提到的是:即使一个折叠式共源共栅放大器基本上是一个单增益级,他的增益也可能非常合理,约为700-3000。出现这样一个高增益是因为增益是由输入跨导和输出阻抗的情况决定的,输出阻抗由于使用了共源共栅技术而非常高。

图中显示的差动到单端的转变是由M5,M5c,M6,M6c。组成的宽幅镜像电流源实现的,在差动输出设计中,这些可能被2个宽幅共源共栅电流吸收器所代替,并且可以添加共模反馈电路。

补偿通过负载电容CL实现,并实现了主要极点补偿。在负载电容非常小的应用中,有必要添加附加的补偿电容与负载并联来保证稳定性。如果想要超前补偿,可以添加一个电阻与CL串联,当在一些应用中不可能实现超前补偿时,例如当补偿电容主要由负载电容提供时,这种方法在很多情况下都适用,而许多设计者似乎没有意识到这一点(也就是说,在很多情况下,都可以在负载电容上串联一个电阻)。

输入差动对MOS管的偏置电流等于Ib1/2。P沟道共源共栅MOS管在任意一个(M1c或者M2c)的偏置电流,等于M3或者M4的漏极电流减去Ib1/2,因为(W/L)3=(W/L)4=(W/L)8b,所以这个漏极电流由Ib和(W/L)81/(W/L)11比率确定,由于共源共栅晶体管之一的偏置电流由电流相减得到,所以他要准确建立,需要Ib2和Ib3从一个单偏置网络得到。此外,得到这些电流的任何镜像电流源应由单位大小的MOS管并联形成的MOS管组成,这种方法可以消除宽度不同的MOS管引起的二阶效应造成的误差。

3 测试分析

Vdd=3V,Ib=62.5μA,CL=5pF

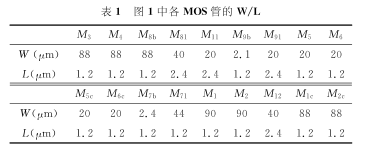

图1中各MOS管的参数如表1所示。

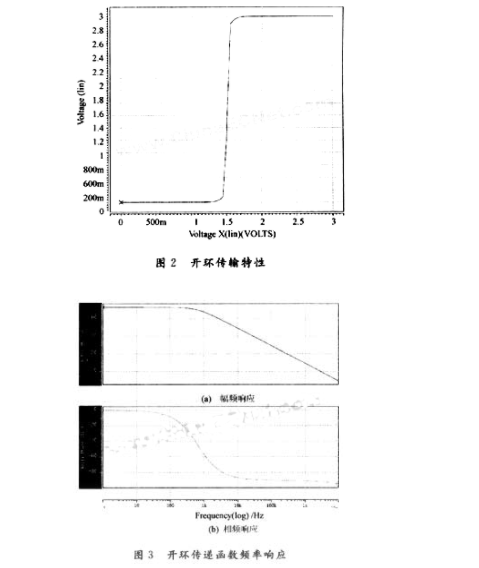

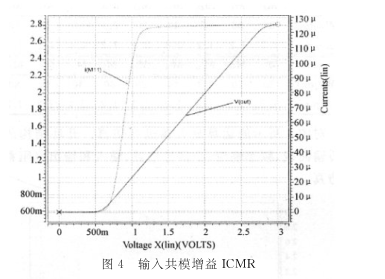

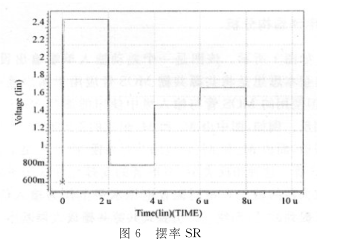

对图1所示的运算放大器进行仿真,开环结构的电压传输曲线、频率响应、小信号增益、输出和输出电阻都可以仿真。

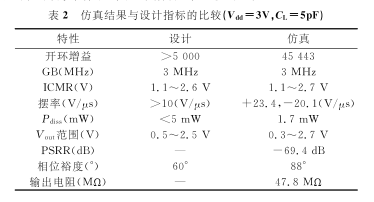

从图2中看出:开环输出电压摆幅从0.3-2.7V,最后得到仿真结果与设计指标的比较,见表2。

4 结语

本文解释的运放是一种折叠共源共栅运放,具有高直流开环增益、低输入失调电压、高速等特点,TSMC0.18混合信号双阱CMOS工艺的BSIM3(V3.2)模型参数,利用HSpice W-2005.03等仿真工具对其进行了DC,AC及瞬态分析。

仿真结果表明,本文实现的运放具有73dB的直流开环增益,在5pF的负载电容条件下,运放的单位增益频率为3MHz,相位裕度为88°,输出电阻为47.8MΩ。

可以看出,设计几乎是令人满意的,微小的调节可以通过改变W/L比或直流使放大器工作在指定的范围。

编辑:jq

-

共源共栅放大器的特点是什么2024-09-27 2581

-

共源共栅放大器电路图分享2024-02-19 9293

-

共源共栅放大器工作原理及应用特点2023-09-28 7536

-

为什么共源级和共栅级放大器的输出阻抗是一致的?2023-09-20 3444

-

单级,共源共栅和调节型共源共栅型放大器的优缺点是什么?2023-09-18 5452

-

折叠共源共栅运算放大器的设计2022-07-08 1357

-

请问怎么设计一种单级全差分增益增强的折叠共源共栅运算放大器?2021-04-20 3271

-

共源共栅跨导运算放大器的设计2017-03-05 847

-

增益增强共源共栅放大器的设计2011-06-29 12603

-

一种高增益CMOS全差分运算放大器的设计2010-07-29 660

-

折叠共源共栅运算放大器原理及设计2010-03-12 13135

-

一种低压低功耗CMOS折叠-共源共栅运算放大器的设计2009-12-14 1481

全部0条评论

快来发表一下你的评论吧 !