减法计数器的结构原理

电子说

描述

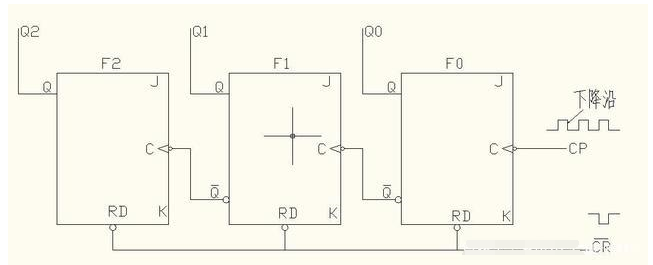

异步二进制减法计数器如图1-1所示

减法计数器的结构原理

1-1减法计数器的结构原理

该计数器是一个3位二进制异步减法计数器,它与前面介绍过的3位二进制异步加法计 数器一样,是由3个JK触发器组成,其中J、K端都悬空(相当于J=1、K=1),两者的不同 之处在于,减法计数器是将前一个触发器的Q非端与下一个触发器的CP端相连。

电子时代

计数器原理

计数器的工作过程分为两步。

第一步:计数器复位清零。

在工作前应先对计数器进行复位清零。在复位位控制端CR非送一个负脉冲到各触发器Rd 端,触发器状态都变为“0”,即Q2Q1Q0=000 。

数字时代

第二步:计数器开始计数。

当第1个时钟脉冲的下降沿到触发器F0的CP端(即C端)时,触发器F0开始工作,由 于J=K=1, JK触发器的功能是翻转,触发器F0的状态由“0”变为“1”,即Q0=1, Q0由“1” 变为“0”,这相当于一个脉冲的下降沿,它送到触发器F1的CP端,触发器E的状态由“0” 变为“1”,即Q1=1, Q由“1”变为“0”,它送到触发器F2的CP端,触发器F2的状态由 “0,变为“1”,Q2=1, 3个触发器的状态均为“1”,计数器的输出为Q2Q1Q0=111。

当第2个时钟脉冲的下降沿到触发器F°的CP端时,触发器F。状态翻转,Qo由“1”变 为“0”,Qo则由“0”变为“1”,触发器Fi的状态不变,触发器F2的状态也不变,计数器 的输出为Q2Q1Q0=110。

当第3个时钟脉冲下降沿到触发器F0的CP端,时F0触发器状态又翻转,Q0由“0”变为“ 1 ”, Q0则由“1”变为“0”(相当于脉冲的下降沿),它送到F1的CP端,触发器F1状态翻转,Q1 由“1”变为“0”,Q则由“0”变为“1”,触发器F2状态不变,计数器的输出为101.

同样道理,当第47个脉冲到来时,计数器的Q2Q1Q0依次变为100、011、010、001。 由此可见,随着脉冲的不断到来,计数器的计数值不断递减,这种计数器成为减法计数器。当 再给输入一个脉冲时,Q2Q1Q0又变为000,随着时钟脉冲的不断到来,计数器又重新开始对脉 冲进行计数。

3位异步二进制减法计数器的时钟脉冲输入个数与计数器的状态见表1-1.

表1-1计数器状态表

责任编辑人:CC

- 相关推荐

- 热点推荐

- 计数器

-

计数器输入的计数脉冲源结构与工作方式详解2018-01-22 20020

-

30进制加法计数器和30进制减法计数器2012-10-07 7956

-

求十二进制减法计数器2013-04-28 3955

-

求 改进 六十进制减法计数器2013-05-09 3833

-

十位制减法计数器2016-06-19 3532

-

定时器/计数器的结构和工作原理2009-03-29 20450

-

可逆、可预置计数器CD4029构成的任意N分频减法计数电路2009-06-22 6313

-

环形计数器和扭环形计数器2010-01-12 10420

-

异步二进制减法计数器时序分析2011-04-19 22588

-

机械计数器结构及原理图2018-02-24 51478

-

计数器原理2019-01-24 67862

-

"stm32f0按键计数器程序_数字系统设计, 8个经典计数器电路方案合辑"2021-11-25 1701

-

同步计数器和异步计数器的区别主要在哪里2023-12-13 16280

-

同步计数器和异步计数器各有什么特点2023-12-15 3518

-

计数器的结构和工作原理2024-05-23 10821

全部0条评论

快来发表一下你的评论吧 !