riscv如何实现自定义指令并用qemu运行详解

描述

1.说明

riscv支持指令集自定义扩展,这大大增加了riscv的可玩性,同时对于一些实际应用中,自己通过一条指令来实现特定的功能,效率非常高,当然,前提是硬件平台需要对该指令的支持。

本文主要利用qemu模拟硬件平台,实现特定指令解析,同时写裸机代码来测试该指令的运行情况。当然,如果实现的很好,是需要修改riscv的gcc的,让自己的扩展指令加入。这里不做修改,后面会详细描述细节。

自定义指令实现完成后,用qemu对功能进行仿真,然后通过fgpa验证具体的行为,最后流片,一个完整的riscv,并支持自定义指令的芯片就可以完成了。

这里可以实现一个cube指令,并定义该指令的含义是将传入的值进行三次幂,得到最后的结果。

qemu模拟的硬件平台是sifive_u。

2.riscv扩展指令的添加

目的:

实现cube指令,传入一个数,比如2,那么该指令返回的结果是8,如果是3,则返回3^3=27。

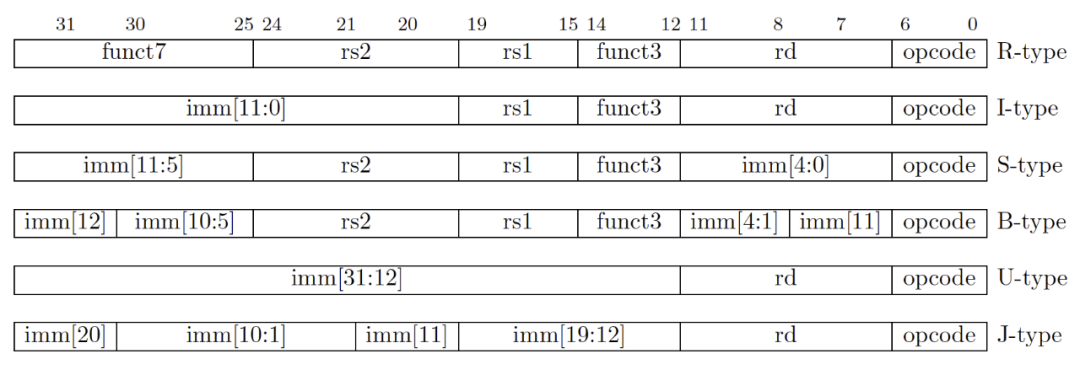

riscv指令的类型:

对于riscv,其指令按照特定的类型分为一下几种。

目前的实现只基于R-type。

其扩展指令集的格式如下

.insn r opcode, func3, func7, rd, rs1, rs2

按照其语法规则opcode表示操作码,目前是7位,对于非压缩指令来说,最后两位是1。所以自己可以定义一个操作码,当然有一些操作码已经使用了,具体可以查看下面的仓库。

https://github.com/riscv/riscv-opcodes

也可以在riscv官网上

的第Chapter 24 RV32/64G Instryction Set Listings查看目前riscv定义的指令码。

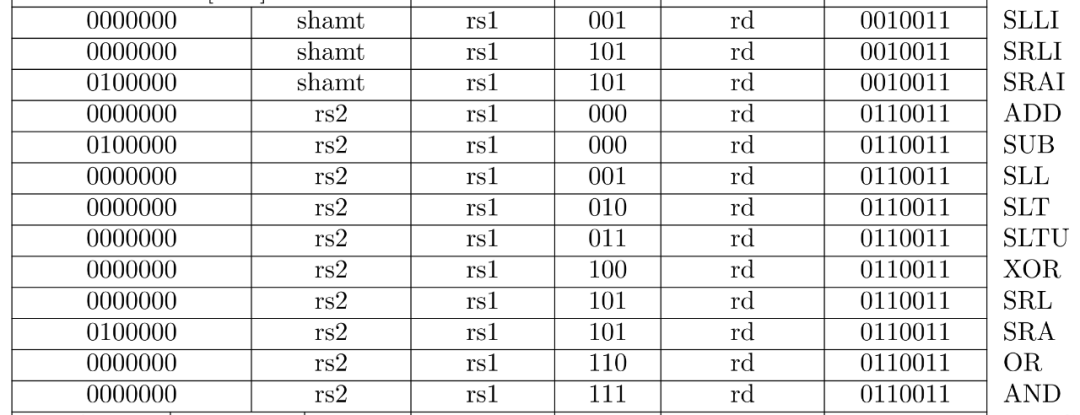

比如关于算数的指令集定义如下:

自己设计一条指令要在这些标准指令之外的,比如操作码为0x7b。

内联汇编格式如下:

asm volatile(“.insn r 0x7b, 6, 6, %0, %1, x0” : “=r”(cube) : “r”(addr));

于是,按照语法解析如下:

* func7 rs2 rs1 func3 rd opcode

* 31---------25--------19------15------12----------------6----------0

* | 000110 | 00000 | ***** | 110 | ***** | 1111011 |

* |------------------------------------------------------|----------|

上图中,*表示的是任意值,所以该指令在翻译的时候,实际上就是取出rs1表示的是寄存器地址,然后返回的是rd,也是寄存器地址。最后,从寄存器中存放的地址取数据则得到相应的值。

3.裸机代码编译

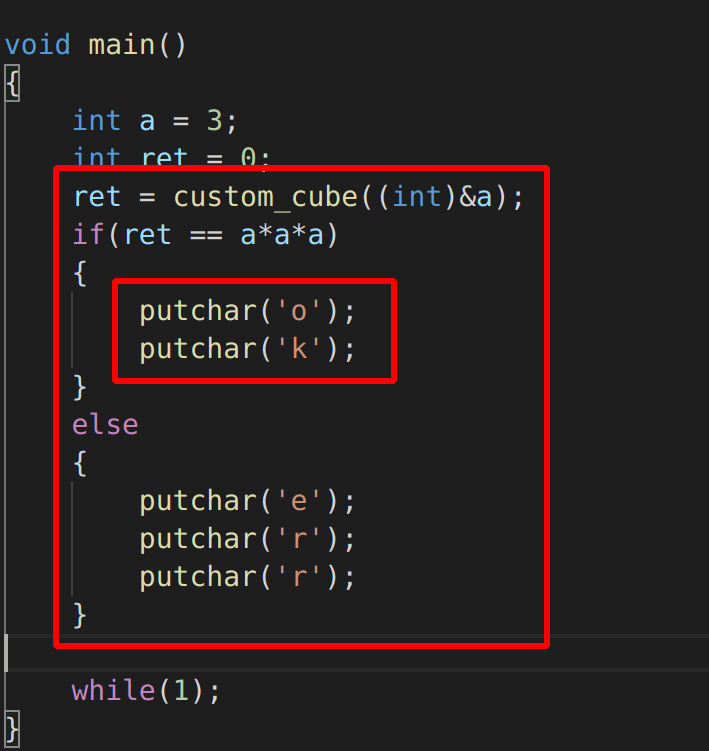

下面一段非常简单的针对sifive_u的裸机代码,并在进入main函数后,直接调用custom_cube计算得到结果。

#include 《stdio.h》

static int custom_cube(int addr)

{

int cube;

asm volatile (

“.insn r 0x7b, 6, 6, %0, %1, x0”

:“=r”(cube)

:“r”(addr)

);

return cube;

}

void main()

{

int a = 3;

int ret = 0;

ret = custom_cube((int)&a);

if(ret == a*a*a)

{

putchar(‘o’);

putchar(‘k’);

}

else

{

putchar(‘e’);

putchar(‘r’);

putchar(‘r’);

}

while(1);

}

程序非常简单,就是判断custom_cube得到计算结果是否与a*a*a的值相等。

代码可以在下面的地址中找到

https://github.com/bigmagic123/riscv-hello-c

下载sifive的交叉编译工具链即可,不需要自己编译工具链,添加到系统环境变量,即可编译。

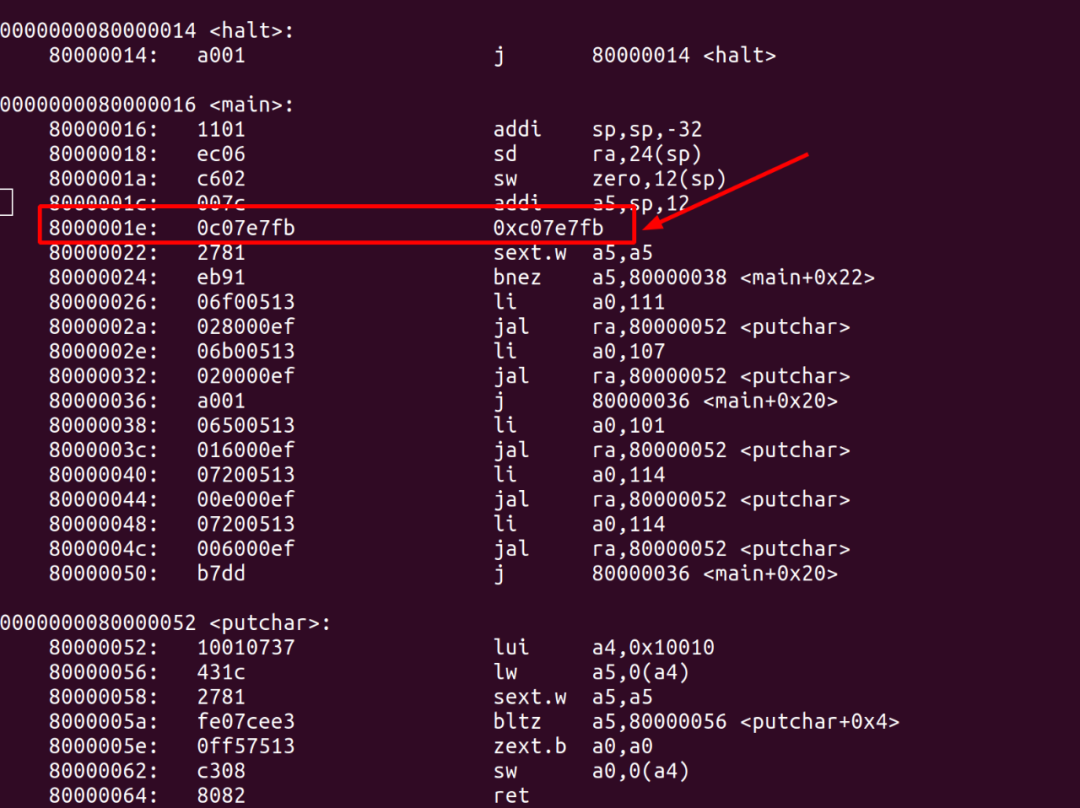

通过反汇编查看

riscv64-unknown-elf-objdump -D build/bin/rv64imac/qemu-sifive_u/hello 》 1.txt

可以看到如下的信息:

可以看到gcc并不认识这条指令,没法翻译成伪代码,所以直接变成机器码了。

手动分析一下这个机器码

* func7 rs2 rs1 func3 rd opcode

* 31---------25--------19------15------12----------------6----------0

* | 0000110 | 00000 | 01111 | 110 | 01111 | 1111011 |

* |------------------------------------------------------|----------|

通过上述分析,主要关注传递的参数rs1与rd。其值都是01111,因为寄存器一共是32位,所以用五位来表示,此时使用了x15寄存器传递参数同时作为返回值。

4.qemu编译和指令的扩展

本机测试环境是Ubuntu20.04,首先需要从官方网站上下载最新的代码。

执行下面的命令,安装编译环境。

sudo apt-get install -y git build-essential pkg-config zlib1g-dev libglib2.0-0 libglib2.0-dev libsdl1.2-dev libpixman-1-dev libfdt-dev autoconf automake libtool librbd-dev libaio-dev flex bison make

sudo apt-get install ninja-build

并进入qemu目录并创建build目录,进入build,输入下面语句开始编译。

。./configure --prefix=your_path/linux_qemu --target-list=riscv32-softmmu,riscv64-softmmu && make -j8 && make install

其中your_path/linux_qemu是自己存在的目录。编译完成后,qemu在该目录下。

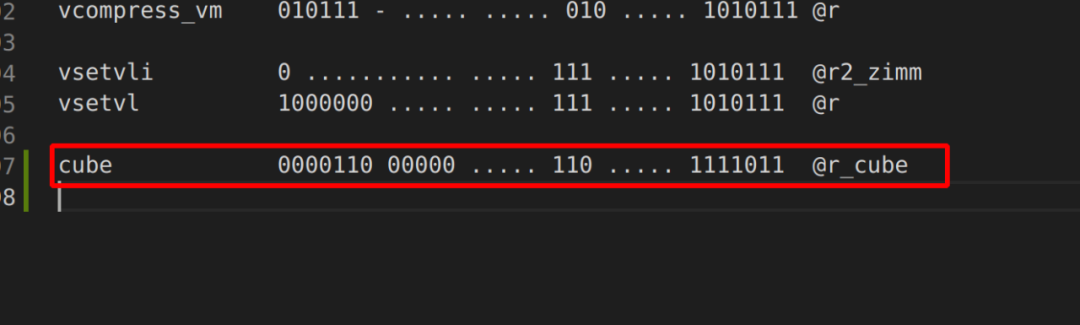

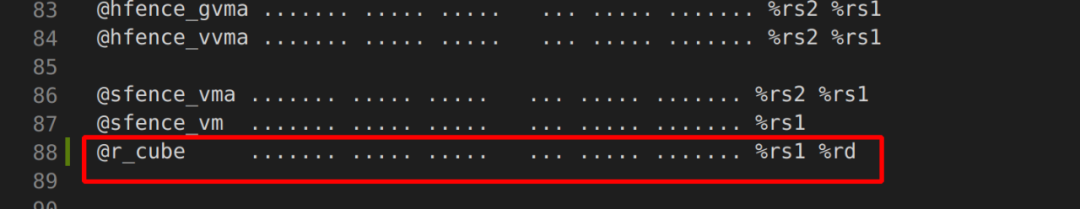

4.1 添加扩展指令的decodetree

由于riscv指令格式具有一定的规律,所以有人根据语法规则写了一个通用的python脚本来生产对应指令解析函数,这也是非常值得学习。qemu是通过指令集解析的,目前只需在decodetree中增加一条cube指令的实现即可。

在target/riscv/insn32.decode中。

只需要按照规定的格式排版即可

定义其格式

4.2 添加扩展函数

在扩展函数实现上可以在target/riscv/insn_trans/trans_rvi.c.inc中添加

static bool trans_cube(DisasContext *ctx, arg_cube *a)

{

gen_helper_cube(cpu_gpr[a-》rd], cpu_gpr[a-》rs1]);

return true;

}

当指令集解析时,匹配上操作码后,可以执行该函数。

另外也需要在target/riscv/helper.h函数中添加函数定义

DEF_HELPER_1(cube, tl, tl)

其中第一个参数为名称,第二个是返回值,第三个是参数传递值。

4.3 解析函数实现

可以在target/riscv/op_helper.c中添加具体指令的实现。

target_ulong helper_cube(target_ulong rs1)

{

target_ulong val;

cpu_physical_memory_rw(rs1, &val, 4, 0);

return val*val*val;

}

由于该指令是实现立方乘法,所以返回乘法值即可。

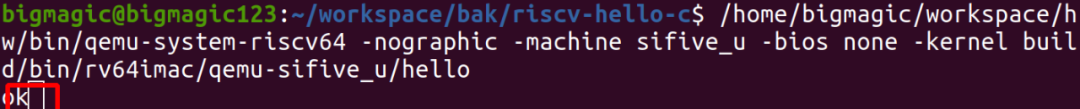

5.功能测试与验证

qemu重新编译后,执行第二章节的代码。

当指令执行正确会输出ok。

qemu-system-riscv64 -nographic -machine sifive_u -bios none -kernel build/bin/rv64imac/qemu-sifive_u/hello

实际执行效果如下:

此时,可以正常的执行成功。

编辑:lyn

-

采用汇编指示符来使用自定义指令2025-10-28 248

-

riscv实现自定义指令并用qemu运行2025-10-31 272

-

自定义外设和自定义指令在SOPC系统中是如何运行的?2021-05-26 2497

-

RISCV自定义指令编译生成.verilog文件后如何修改其中的地址?2023-08-12 581

-

riscv实现自定义指令并用qemu运行的过程2023-08-16 1426

-

SOPC中自定义外设和自定义指令性能分析2009-03-29 1915

-

NIOS II自定义指令设计之实例篇2010-03-27 3606

-

1602自定义字符2016-01-20 972

-

如何通过LUA实现自定义串口指令设置2019-10-17 1676

-

自定义视图组件教程案例2022-04-08 992

-

自定义算子开发2022-04-07 5637

-

labview超快自定义控件制作和普通自定义控件制作2023-08-21 1047

-

串口屏LUA教程10-自定义串口指令2021-04-29 1340

-

LabVIEW运动控制(三):EtherCAT运动控制器的高效加工指令自定义封装2025-04-08 3874

-

HarmonyOS应用自定义键盘解决方案2025-06-05 2588

全部0条评论

快来发表一下你的评论吧 !