请问怎样去设计串口收发模块仿真模型?

电子说

描述

本实验,为ZX-2开发板的综合实验,该实验利用ZX-2开发板上的ADC、独立按键、UART等外设,搭建了一个具备丰富功能的数据采集卡,ZX-2开发板负责进行数据的采集并将数据通过串口发送到PC机上,PC端,利用强大的串口调试工具——串口猎人,来实现数据的接收分析,并将数据分别以波形、码表、柱状图的形式动态显示出来,以让使用者能够直观的看到ADC采集到的信号细节。同时,用户也可以使用串口猎人通过串口给下位机(FPGA)发送指令,下位机将对接收到的指令进行解码,然后依据解码结果来配置FPGA中各个子模块的控制寄存器,以实现通过串口控制FPGA中子模块工作状态的功能。

本实验中,涉及到的应用模块和知识点如下所示:

串口收发模块的设计和使用;

串口收发模块仿真模型的设计;

串口简单数据帧的解码;

串口帧转Memory Mapped总线的设计;

Memory MappedSlave模块的设计;

线性序列机设计思想的应用(ADC驱动);

独立按键消抖的分析与实现;

直接数字频率合成(DDS)的设计与实现;

使能时钟对系统间模块协调工作的重要性;

串口猎人的详细使用;

完整系统的仿真验证设计;

头文件在设计中的运用;

Quartus II软件中可定制化存储器ROM的使用;

本实验不仅注重可综合的代码编写,同时更注重代码的仿真验证。通过仿真,我们能够寻找设计中可能存在的问题并修正。最终,在整个系统仿真无误的基础上,下载到开发板上一次性成功。

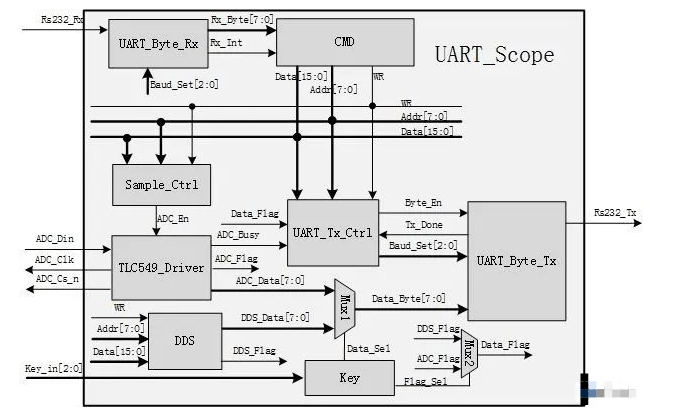

下图为本设计的框架结构图:

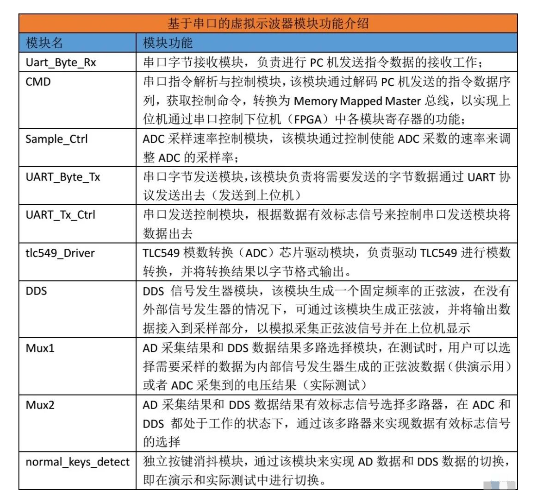

系统采用模块化设计,在模块划分的过程中,重点考虑了系统的可扩展性,下表为对系统中各模块功能的简单介绍。

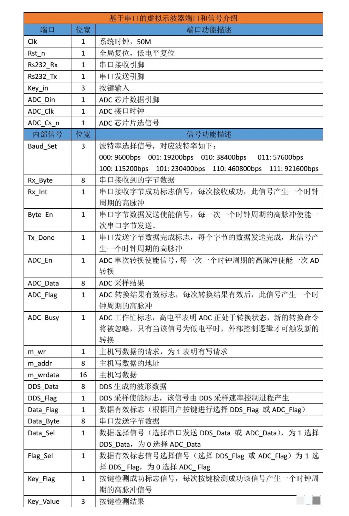

系统中各端口和信号的功能介绍如下:

本实验为综合性实验,代码量较大,因此这里只针对部分代码进行讲解。

责任编辑:lq6

-

怎样使用FIFO去实现串口数据的收发功能呢2022-01-27 1563

-

请问大神怎样去使用STM32串口+DMA呢2021-12-13 1012

-

怎么使用DMA去收发串口的数据?2021-12-10 1527

-

怎样去设计一种STM32串口中断收发的应用接口呢2021-12-08 1093

-

怎样去搭建一种PMSM滞环电流控制仿真模型2021-10-08 2588

-

如何对双母线结构模型进行仿真2021-09-24 2499

-

请问怎样去搭建一种模糊控制器系统的数学模型2021-08-18 1481

-

怎样去搭建一种基于PI调节器的PMSM矢量控制系统模型?2021-07-27 1174

-

请问怎样去设计一种基于MATLAB的小型电力系统模型?2021-07-11 1813

-

怎样通过EWB去构造DAC的仿真模型?2021-04-21 1240

-

SFP光收发模块的工作原理及其设计与仿真2017-11-13 2552

全部0条评论

快来发表一下你的评论吧 !