探究FPGA与ARM的无人机陀螺仪数据接口设计

电子说

描述

无人机系统对于地面站发送的控制信号以及飞行器传回的姿态数据有着极高的实时性、可靠性与稳定性要求,这对无人机通信系统设计提出了新的挑战。对于采用ARM作为微处理器的无人机系统来说,系统往往需要协调基于ARM处理器的高速陀螺仪模块与相对低速的外部无线数据传输模块间的工作。在通信高稳定性与低误码率的要求下,处理器不得不花时间运行空操作来等待外部相对低速的传输模块完成一帧数据的收/发。由于等待所浪费的处理器运算周期无形中降低了整个飞控系统的实时性,进而带来许多潜在的不稳定因素。

本设计结合无人机系统发展需求,采用FPGA FIFO[1]作为高速数据缓冲,提出一种基于FPGA内建FIFO的无人机陀螺仪前级通信接口。通过高速异步FIFO缓冲,将无人机陀螺仪姿态数据经由FPGA准确无误地发送给地面站,保证了传输质量,架起了高速芯片与低速设备之间沟通的桥梁。

1 FPGA内建FIFO的基本工作原理

FIFO即先进先出队列,采用环形存储电路结构,是一种传统的按序执行方法。先进入的指令先完成并引退,随后才执行第二条指令,是一种先进先出的数据缓存器。根据FIFO的读写时钟频率是否相同,可将FIFO分为同步FIFO与异步FIFO[2]。FIFO的应用可以很好地协调不同时钟、不同数据宽度数据的通信,满足高/低速时钟频率要求。与普通存储器相比,FIFO没有外部读写地址线,使用方便。

本文设计采用FPGA异步FIFO连接基于ARM处理器的高速无人机陀螺仪模块与相对低速的无线数据传输外设。从硬件的观点来看,FIFO实质上就是一块数据内存。异步FIFO采用2个时钟信号控制其读写操作,分别为写时钟(wrclk)和读时钟(rdclk)。一个用来写数据,即将数据存入FIFO;另一个用来读数据,即将数据从FIFO中取出。

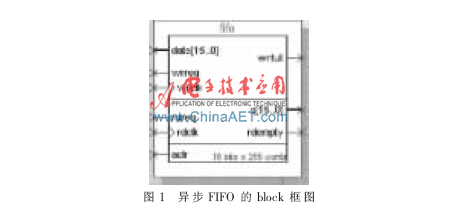

与FIFO操作相关的有两个指针:写指针指向要写的内存部分;读指针指向要读的内存部分。FIFO控制器通过外部的读写信号控制这两个指针移动,并由此产生FIFO空信号或满信号。读写时钟相互独立设计,有效地保证了FIFO两端数据的异步通信,其模块框图[3]如图1所示。其中,异步FIFO模块共有9个端口,分别为数据输入(datda[15..0])、写请求(wrreq)、写时钟(wrclk)、缓冲器满信号(wrful)、读请求(rdreq)、读时钟(rdclk)、数据读出(q[15..0])、缓冲器空信号(rdempty)、缓冲器清空信号(aclr)。

2 基于ARM的无人机陀螺仪接口结构

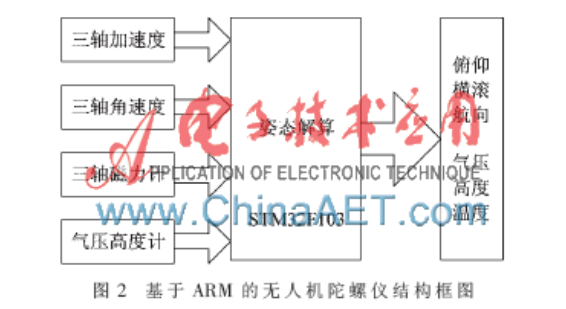

由于机载燃油和电能储备的制约,无人机载设备要求小巧轻便,能效比高,因此对芯片的选型及电路结构提出了较高的要求。综合稳定性、数据精度、工作温度、封装体积以及能耗等各方面因素,对无人机陀螺仪传感器经行严格筛选,确定了如图2所示的陀螺仪方案。

无人机陀螺仪的主控芯片选用ARM 32 bit CortexTM M3内核的STM32F103T8处理器。其内建64 KB的闪存存储器和20 KB的运行内存,以及7通道的DMA、7个定时器、2个UART端口等。通过板载的8 MHz晶体和STM32内部的PLL,控制器可以运行在72 MHz的主频上,为姿态解算[4]提供强大的硬件支持。

三轴加速度与三轴角速度传感器采用Invensense公司的MPU-6050单芯片方案,此芯片为全球首例整合性6轴运动处理组件,相比其他多芯片实现方案,免除了整合陀螺仪与加速度器轴间差的问题,大大减少了封装空间。

三轴磁力计采用Honeywell公司的HMC5883L芯片,此芯片内部采用先进的高分辨率HMC188X系列磁阻传感器与行业领先的各向异性磁阻技术(AMR),具有轴向高灵敏度和线性高精度的特点,测量范围从毫高斯到8高斯(gauss),稳定可靠。

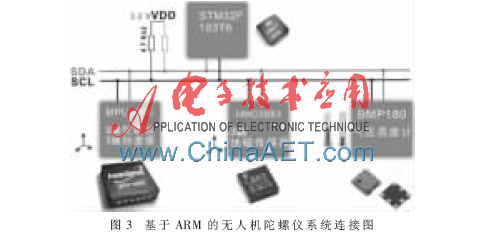

气压传感器采用博世公司的BMP180芯片,该芯片性能卓越,绝对精度可以达到0.03 hpa,并且功耗极低,只有3 ?滋A。传感器采用强大的7 pin陶瓷无引线芯片承载(LCC)超薄封装,安装使用方便。各传感器与ARM处理器采用I2C总线连接,示意图如图3所示。

3 FPGA FIFO与陀螺仪的连接

结合无人机ARM陀螺仪的特点,为了适应过程的复杂性,实现操作的简便性,设计选用Altera公司的CycloneII系列芯片EP2C8Q208C8N,在QuartuesII平台上进行Verilog代码设计,使用Altera公司提供的FIFO IP核[5]。此方案稳定高效,易于开发。

3.1 陀螺仪与FIFO及FPGA的连接

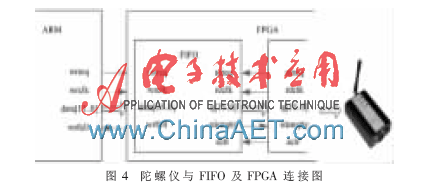

处理器采集各传感器信号,在ARM内部进行姿态解算,进而得到俯仰角、横滚角、航向角、气压、高度和温度信息。为了及时将解算得到的数据发送回地面站,处理器控制写请求信号wrreq和写时钟wrclk将这些数据高速写入FIFO,然后回到飞行控制程序,进行下一周期的姿态解算。FIFO在数据写满后,写满标志位wrfull会置高电平,ARM处理器通过检测写满标志位的状态来判断是否继续写入数据。

与此同时,在FPGA中通过检测所读取FIFO是否为空标志位rdempty来判断是否继续读取数据。读空标志位为低电平代表FIFO中有数据,可以读取,则配合读请求信号rdreq和读时钟rdclk及时读取数据,直到将数据全部读出,标志位变为高电平,此时FIFO中已经没有数据。基于ARM的陀螺仪与FIFO及FPGA的连接如图4所示。

3.2 FIFO的配置与读写操作

针对上述ARM陀螺仪接口特点,对FIFO进行配置如下。

FIFO Width : 16 bit

FIFO Depth : 2 048 words

Synchronize reading and writing clock : YES

Asynchronous clear : YES

设计采用位宽为16 bit、深度为2 048且带有同步清零端[6]的异步FIFO结构,其写时序与读时序分别如图5、图6所示。

状态机跳转部分控制代码如下:

always@(posedge SYSCLK or negedge RST )

begin

if(!RST)

state 《= idle;

else

case(state)

idle:

begin

data[15:0] 《= 16′d0;

wrreq 《= 1′b1;

rdreq 《= 1′b0;

aclr 《= 1′b0;

state 《= write;

end

read:

if(rdempty != 1′b1 && rdreq ==1′b1)

read_start 《= 1′b1;

else

begin

read_start 《= 1′b0;

wrreq 《= 1′b1;

state 《= idle;

end

write:

if(wrfull!= 1′b1 && wrreq == 1′b1)

write_start 《= 1′b1;

else

begin

write_start 《= 1′b0;

rdreq 《= 1′b1;

state 《= read;

end

default: state 《= idle;

endcase

end

4 系统仿真效果

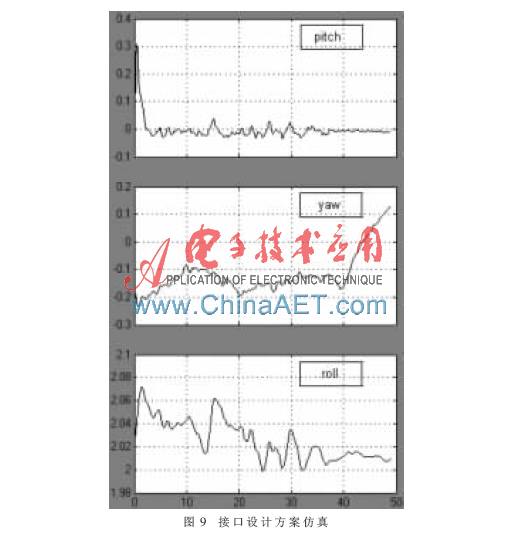

综合运用QuartuesII[9]与ModelSim SE[10]先进仿真工具,结合FPGA内建FIFO与基于ARM的无人机陀螺仪接口设计方法,仿真结果如图8、图9所示。

从图8中仿真结果得知,在写入时钟频率为100 MHz、写满标志位为低电平时,待写入数据data在每个写入时钟上升沿来临后被准确写入FIFO的存储区;随后在读出时钟频率为5 MHz且读空标志位为低电平的情况下,待读出数据q在每个读时钟上升沿来临后被正确读出,系统读写数据稳定准确,符合设计需求。

图9为通过此通信接口读取得到的无人机飞行姿态数据,包括俯仰角、偏航角、滚转角,以图表形式予以显示。数据精度与实验结果理想,验证了FPGA与ARM无人机陀螺仪数据接口设计方案稳定可靠。

本文提出了基于FPGA内建FIFO与ARM的无人机陀螺仪数据接口设计方法,解决了无人机ARM处理器与相对低速无线发送模块直接数据传输时传输速度不匹配的难题,实现了ARM处理器将无人机姿态数据高速写入FIFO后就可以立即返回、无需等待的功能,节约了处理器资源,使得无人机系统的可靠性与稳定性得到大幅提升。仿真验证表明,读写数据准确无误,显著提高了数据传输速度与数据质量,证明了本方案的可行性与正确性。面对高速数据传输的需求,该系统还可广泛应用于其他需要高无线数据传输的领域,有较高的理论意义和应用价值。

参考文献

[1] 秦鸿刚,刘京科,吴迪。基于FPGA的双口RAM实现及应用[J]。电子工程设计,2010,2(2):72-74.

[2] 夏宇闻.Verilog数字系统设计教程[M]。北京:北京航空航天大学出版社,2008.

[3] BAKER R J,LI H W,BOYEE D E.CMOS电路设计布局与仿真[M]。陈中建,译。北京:机械工业出版社,2006.

[4] PAVLLOV A.CMOS SRAM circuit design and parame tric test in Nano-Scaled technologies[M].New York:Springer,2008.

[5] 单立超,谢雪松。基于FPGA的一种可变帧数字分接技术[J]。电子技术应用,2013,32(2):27-30.

[6] 何涛。基于软硬件协同技术的FPGA测试平台设计及测试实现[D]。成都:电子科技大学,2009.

[7] 徐国强,张萌。基于FPGA的高性能视频信号采集系统设计与实现[J]。微型机与应用,2012,31(6):72-75.

[8] BRIAN D,ANDREW S,CHAN K.RAM with configurable depth and width[P].US:6578 104.1 8.22,June 2003.

编辑:jq

-

无人机流行和快速增长背后,对无人机开发平台了解多少?2019-02-21 4971

-

【uFun试用申请】无人机控制2019-03-22 2420

-

加速度传感器和陀螺仪如何让无人机飞的更稳2020-05-18 2955

-

一种适用于小型无人机的加速度计与陀螺仪的矫正方法2022-02-10 2404

-

无人机飞行电脑V1.0的资料分享2022-09-06 1509

-

电子陀螺仪怎么工作的?怎么使四轴无人机平衡的 ?2023-11-10 1477

-

无人机陀螺仪主控芯片STM32应用详解2015-05-13 12428

-

无人机干扰器是否会导致无人机坠毁2021-04-19 4422

-

无人机的陀螺仪是什么作用 无人机控制系统原理2023-07-21 9521

-

MEMS陀螺仪在无人机中扮演的角色有多重要?2025-01-08 1830

-

MEMS陀螺仪如何成为无人机精准飞行的核心引擎?2025-07-04 1065

-

为什么三轴MEMS陀螺仪是无人机飞控系统的核心传感器?2025-08-07 1532

-

什么是光纤陀螺仪?陀螺仪有哪些作用?2025-08-26 2747

-

陀螺仪在无人机中的应用:无人机精准飞行的关键保障2025-10-09 1235

-

精准感知,稳控未来:MEMS陀螺仪助力无人机飞控新高度2026-02-14 778

全部0条评论

快来发表一下你的评论吧 !