探究CPCI总线的PMC载板设计

电子说

描述

摘 要:设计了一种基于CPCI总线标准的PMC接口载板。载板以FPGA为核心,集成了CPCI接口模块和DPRAM(双口RAM)模块,CPCI接口模块采用FPGA+PCI IP核(软核)解决了系统集成的问题,DPRAM模块为系统提供了数据缓存功能。环回测试和中断测试解决了在没有子卡PMC模块的情况下,读写、验证DPRAM空间数据和测试中断响应的问题。此外,还支持子卡PMC模块后出线到CPCI总线。调试结果表明,该载板在嵌入式实时操作系统VxWorks下可以稳定运行,正确地读写DPRAM空间的数据,及时地响应中断,满足了对载板的性能需求。

在工业和嵌入式领域实际工程应用中,模块化的设计思想已深入人心。针对不同使用场合的具体应用以及为方便后续的维护和升级,将其中具有通用性和可持续利用的部分单独设计成载板,载板配合不同的应用模块就可以组合成具有不同功能的专业I/O模块。

Compact PCI(Compact Peripheral Component Interconnect)简称CPCI,中文又称紧凑型PCI,是国际工业计算机制造者联合会PICMG(PCI Industrial Computer Manufacturer′s Group)于1994提出来的一种总线接口标准,是以PCI电气规范为标准的高性能工业用总线[1]。CPCI规范改进自PCI电气规范2.1,应用于工业和嵌入式领域。当前最新的CPCI规范是PICMG 3.0。PICMG 3.0主要将应用在高带宽电信传输上,以适应未来电信的发展,PICMG 2.x则仍是目前CPCI的主流,并将在很长时间内主宰CPCI的应用。

PCI夹层卡PMC(PCI Mezzanine Cards)是IEEE P1386.1的标准,作为一个IEEE标准,PMC确保了任何符合该标准的主板或者模块能够与其他按照该标准设计的主板或者模块兼容[2]。这样就为用户提供了很大的柔性,用户可以任意组合和搭配不同的主卡和模块。PMC是个开放标准,它为Multibus II、VME和Compact PCI带来了前所未有的大量I/O产品和高性能。

本文结合实际的工程项目,设计实现一个基于CPCI总线并符合PICMG 2.0规范的6U(233.35 mm×160 mm)通用型PMC载板FTC-C920并开发其在VxWorks 5.5下的驱动软件。

1 载板总体结构设计

本着简洁和通用的前提,此载板主要由电源模块(Power)、PMC接口模块(J11~J14)、CPCI总线接口模块(J1、J4、J5)和FPGA组成,总体结构如图1所示。

2 PMC接口和CPCI总线接口模块设计

PMC接口的特性为:前两个(“P11”和“P12”)用于32位PCI信号,第3个(“P13”)是64位PCI信号需要。一个额外的总线连接器(“P14”),可用于非指定的I/O信号[2]。本设计中,PMC接口模块采用4个(J11~J14)PMC(PCI Mezzanine Cards)8 mm高标准连接器,支持用户子卡PMC后出线到CPCI总线接口J4和J5。图1给出了板卡的CPCI连接器情况,J1用作32位PCI,J4和J5用作后面板I/O,可自定义[1]。

3 FPGA设计

从图2中可以清楚地看到,FPGA主要被设计集成了PCI接口模块(PCI Slave IP CORE)和DPRAM模块。

3.1 PCI接口模块设计

3.1.1 几种PCI接口设计方案及选择

常见的设计方案有:(1)专用的PCI接口芯片+CPLD;(2)ASIC+CORE;(3)专用的FPGA+PCI IP CORE(硬核);(4)专用的FPGA+PCI IP CORE(软核);(5)带PCI接口的DSP[3]。

几种方案各有利弊,本文结合项目的实际应用需求选择了第4种方案,这个方案满足了系统集成的需求,并可自由添加接口逻辑,降低了成本,减小了设计风险。

3.1.2 具体设计

此模块主要实现33 MHz工作时钟、32 bit总线宽度的PCI接口功能,支持内存空间及配置空间的读写和PCI中断功能。

PCI配置空间分配[4]:Vendor ID(厂商号)1206,Device ID(设备号)0920,BAR0(基地址)映射为1 MB内存空间,其中0x0000~0x3FFF为DPRAM空间,0x4000~0x7FFF为DPRAM环回测试空间,0x8000以后为控制寄存器。

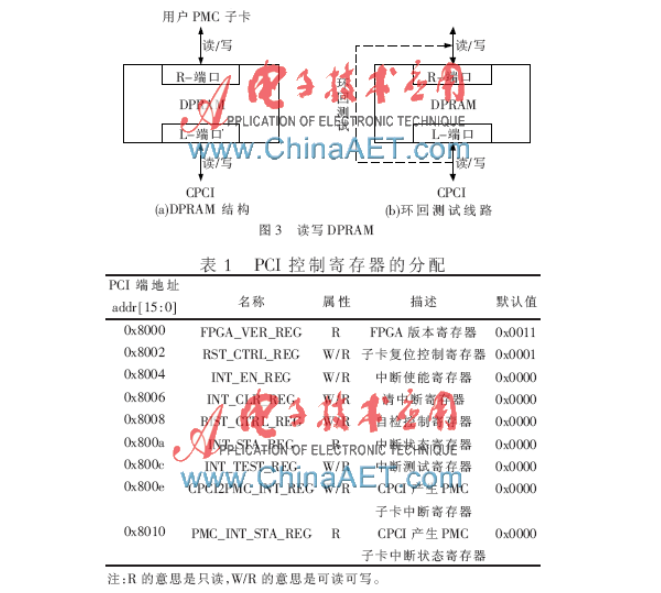

正常情况下(配合用户PMC子卡使用时),CPCI通过DPRAM左(L)端口对DPRAM空间进行读写,用户子卡则通过DPRAM右(R)端口对DPRAM空间进行读写;环回测试情况下(即没有用户PMC子卡的情况下),CPCI可以通过环回测试空间对DPRAM进行读写,即模拟用户子卡对DPRAM空间进行读写。

需要注意的是,0x0000~0x3FFF为DPRAM 16 KB空间,对应DPRAM空间大小为8K×16 bit,而0x4000~0x7FFF为DPRAM环回测试空间,不是FPGA另外开辟的RAM空间,只是软件通过这个空间地址在环回测试下读写DPRAM空间(8K×16 bit)。示意图如图3所示。

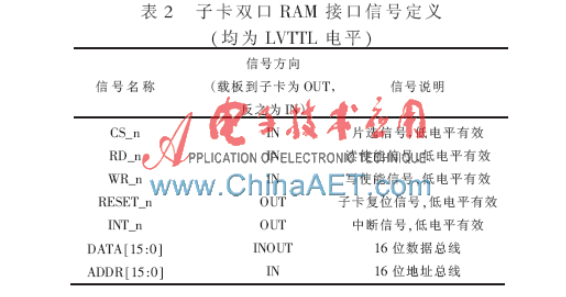

PCI控制寄存器的分配如表1所示。

3.2 DPRAM模块设计

双口RAM模块是FPGA调用内部的IP核实现的,其为数据处理提供缓存功能,总线宽度为16 bit,容量为8 K×16 bit。在没有用户PMC子卡的情况下,为了验证对数据处理的可用性及准确性,通过FPGA逻辑设计支持双口RAM R端口环回自检,如图3(b)中虚线所示,即模拟用户子卡对双口RAM进行读写数据的操作。

CPCI和用户PMC子卡通信采用双口RAM方式,双口RAM用户PMC子卡侧总线定义如表2所示。

4 VxWorks下设备驱动程序设计

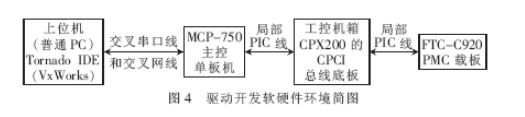

开发此PMC载板Vxworks 5.5下的驱动,硬件选用了Motorola公司的实时主控单板机MCP-750、工控机箱CPX2000 series和此PMC载板FTC-C920,操作系统则选择了美国风河公司的VxWorks嵌入式实时操作系统,使用普通的PC,在Tornado IDE(集成开发环境)下进行驱动的开发。以良好的可靠性和卓越的实时性着称的VxWorks可以满足系统对于高实时性和高可靠性的要求[5]。驱动开发软硬件环境简图如图4所示。

对驱动程序的设计主要有3个部分:载板自检测试模块、FTC-C920和系统控制器互通测试模块以及CPCI中断测试模块。

4.1 载板自检测试模块

载板自检测试主要是载板检测自身器件是否正常工作,功能是否可以实现。

4.1.1 查找C920载板

对于Vxworks下PCI设备调试来说,其有专门的函数可供调用,查找FTC-C920载板可以通过调用函数pciFindDevice()来实现,它包含在pciConfigShow库函数中,此库函数专门用来帮助显示一些PCI设备的信息。此函数可以根据PCI设备给定的供应商标识(VENDOR ID)和设备标识(DEVICE ID)找到相应的设备,并以此返回设备的总线号(busNO)、设备号(deviceNO)和功能号(funcNO)。

4.1.2 读取FTC-C920上的配置资源信息

根据获得的设备的总线号(busNO)、设备号(deviceNO)和功能号(funcNO),通过调用操作系统库函数pciConfigLib中的函数pciConfigInLong和pciConfigInByte访问C920的配置空间,获得设备映射的内存基地址(memBase)和I/O基地址(ioBase)以及中断号irq,分辨对基地址空间是I/O操作还是内存操作,获得的基地址要分别与存储器屏蔽位PCI_MEMBASE_MASK和I/O屏蔽位PCI_IOBASE_MASK相“与”,才能得到真正板卡的内存基地址和I/O基地址。

4.2 FTC-C920和系统控制器互通测试模块

互通测试主要是:

(1)系统控制器(MCP-750)读取用户PMC子卡数据:用户PMC子卡向双口RAM中写入数据,系统控制器(MCP0750)从双口RAM中读取数据,并验证数据是否正确。

(2)用户PMC子卡读取系统控制器(MCP-750)数据:系统控制器(MCP-750)向双口RAM中写入数据;用户PMC子卡从双口RAM中读取数据,并验证数据是否正确。

由于FTC-C920是通用型PMC载板,为了在没有用户PMC子卡的情况下验证互通测试,在FPGA的设计上进行了支持DPRAM R端口环回自检的设计,如图2中虚线所示。

正常情况下(配合用户PMC子卡使用时),环回测试空间不可使用,此时FPGA内部环回自检控制寄存器的相应位为默认值0。如进行环回自检(没有用户PMC子卡时),需往环回自检控制寄存器的相应位写1,此时,系统控制器可对环回测试空间进行读写。

4.3 CPCI中断测试模块

CPCI中断测试主要是用户PMC子卡通过写寄存器的方式产生CPCI中断;系统控制器响应中断,读取数据并验证数据是否正确。

在没有用户PMC子卡的情况下,可以通过产生内部中断的方式进行测试,具体的方法是在FPGA中设置中断使能寄存器,中断测试寄存器,中断状态寄存器和清中断寄存器。程序流程图如图5所示。

本文详细描述了某项目中PMC载板FTC-C920的设计方法及其在VxWorks操作系统下驱动程序的开发流程。在没有用户PMC子卡的情况下,通过环回测试空间的设计,解决了互通测试的要求,通过中断测试寄存器的设计,解决了中断测试的要求。调试结果表明,此PMC载板在VxWorks 5.5下可以稳定地运行。本文的设计方法具有一定的通用性,可为相关工程技术人员提供可以参考的设计经验。

参考文献

[1] PICMG.PICMG2.0 Rev.3.0. PICMG2.0 D3.0 Compact PCI Specification[S]。

[2] IEEE. IEEE P1386.1.Draft Standard Physical and Environmental Layers for PCI Mezzanine Cards: PMC[S]。

[3] 郑毅。基于PMC(PCI背卡)接口的实时数据采集卡[D]。成都:电子科技大学,2003.

[4] 李贵山,陈金鹏.PCI局部总线及其应用[M].西安:西安电子科技大学出版社,2003.

[5] 唐晓平,何峰,梁甸农。基于VxWorks的PCI总线驱动设计[J]。嵌入式操作系统应用,2008,11(2):79-81.

编辑:jq

-

pmc转cpci载板转接卡2024-09-06 458

-

基于CPCI总线的CPCI6320视频播放板2023-12-11 608

-

基于CPCI总线CPU主控模块的设计与实现2023-10-18 599

-

基于CPCI总线的航天器通信信号设备故障检测2021-06-23 924

-

基于CPCI总线的四通道总线通讯模块设计2021-06-22 1156

-

怎么实现基于CPCI总线的多网口卡设计?2021-06-02 1714

-

如何设计一款基于CPCI总线的通用FPGA信号处理板?2021-05-07 1756

-

基于DSP的CPCI总线2018-06-21 1528

-

LTC4240实现CPCI总线接口设计2011-09-09 1072

-

基于CPCI总线的PowerPC主处理板设计2011-07-22 3099

-

CPCI数据总线接口的设计与实现2011-07-17 15826

-

基于CPCI总线的多网口卡设计2010-09-10 2095

-

基于CPCI总线的通用FPGA信号处理板的设计2009-11-28 1429

-

cpci总线请教2008-12-29 4715

全部0条评论

快来发表一下你的评论吧 !