关于Xilinx中DDS IP的运用与讲解

电子说

描述

项目简述

本次项目我们主要是为了讲解DDS,所以我们使用了混频这个小项目来讲解。DDS自己手写是比较简单且灵活,但是Xilinx给我们提供了相应的IP核,那么这次我们将直接讲解使用IP来产生不同频率的正弦波。这篇博客我们也首次引入了Xilinx中block design的设计方法,由于AXI4总线的出现,我们使用block design的设计概念特别简单。本次的项目主要是:利用两个DDS产生两个不同频率的正弦波,然后进行***相乘***混频,利用Modelsim进行仿真验证我们实验的正确性。本次实验所用到的软硬件环境为:

1、VIVADO 2019.1软件环境

2、Modelsim仿真环境

DDS IP的定制及讲解

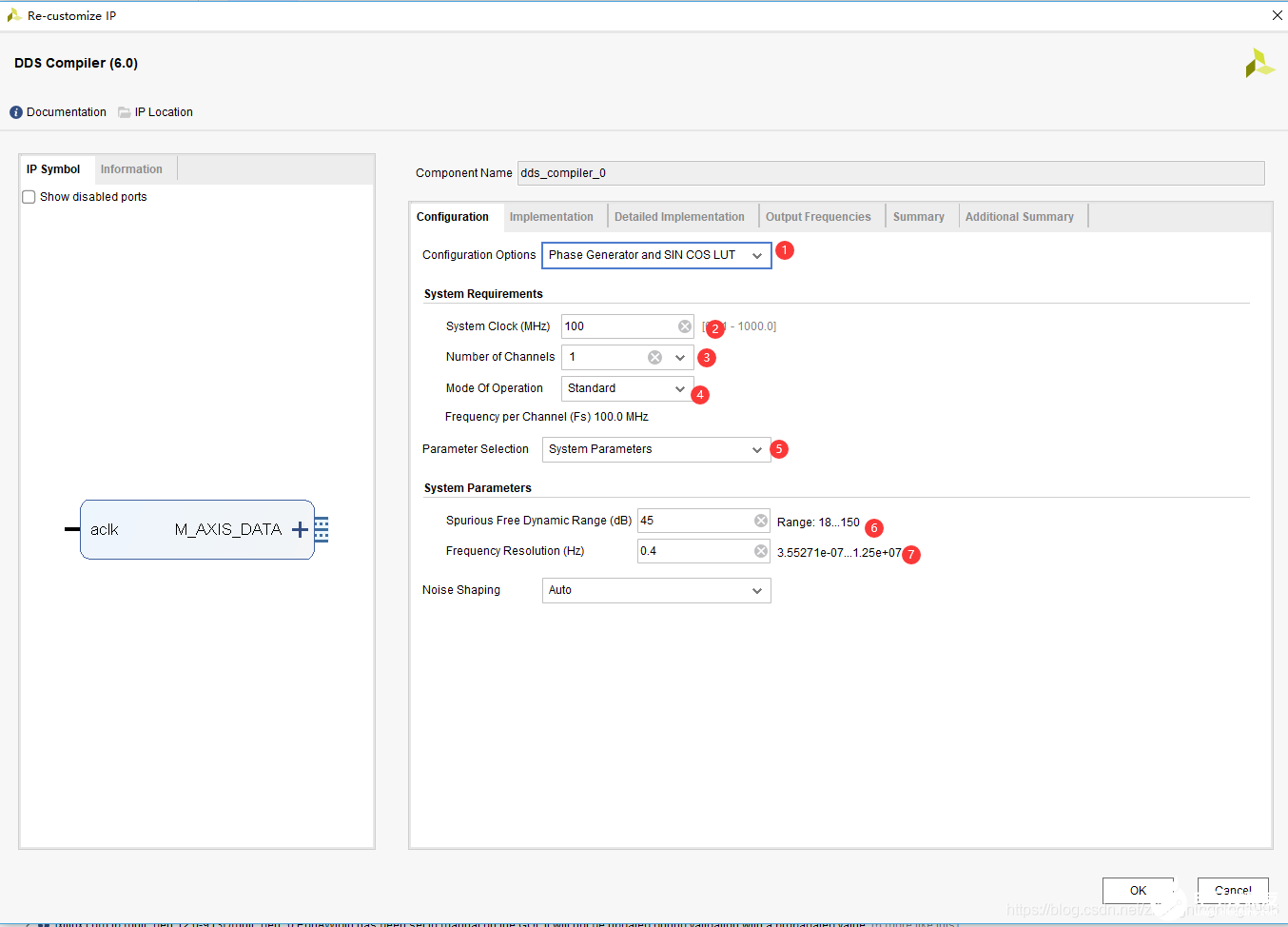

1、我们选择波形与相位同时存在的情况。

2、选择DDS IP输入的系统时钟频率,这里我们选择100MHz。

3、DDS通道的数目,我们这里选择一个。

4、整个IP配置的模式,我们这里选择标准模式即可。

5、参数选择的模式,我们这里选择系统参数,这个选择主要影响IP的定制界面所涉及到的参数。

6、频率的动态范围,主要和DDS内部RAM的数据位宽有关,计算方法是20log2n,其中n为RAM的位宽。

7、选择DDS的最小的频率分辨率。

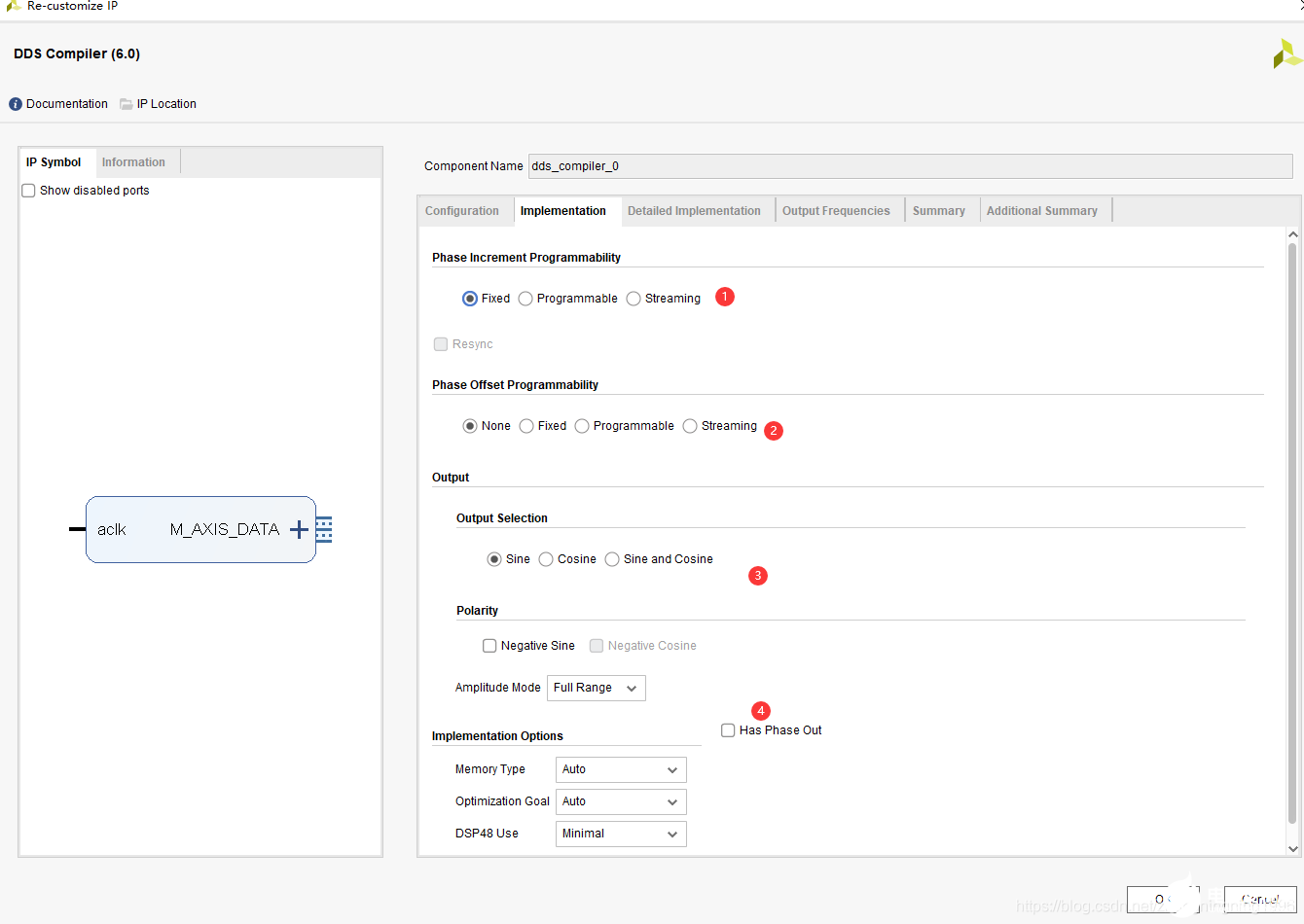

1、相位增量我们选择固定

2、相位偏执我们也选择成固定,这两个参数可以动态控制输出的频率。

3、我们这里产生正弦波

4、因为我们只考虑正弦波的频率,座椅这里不再输出相位信息

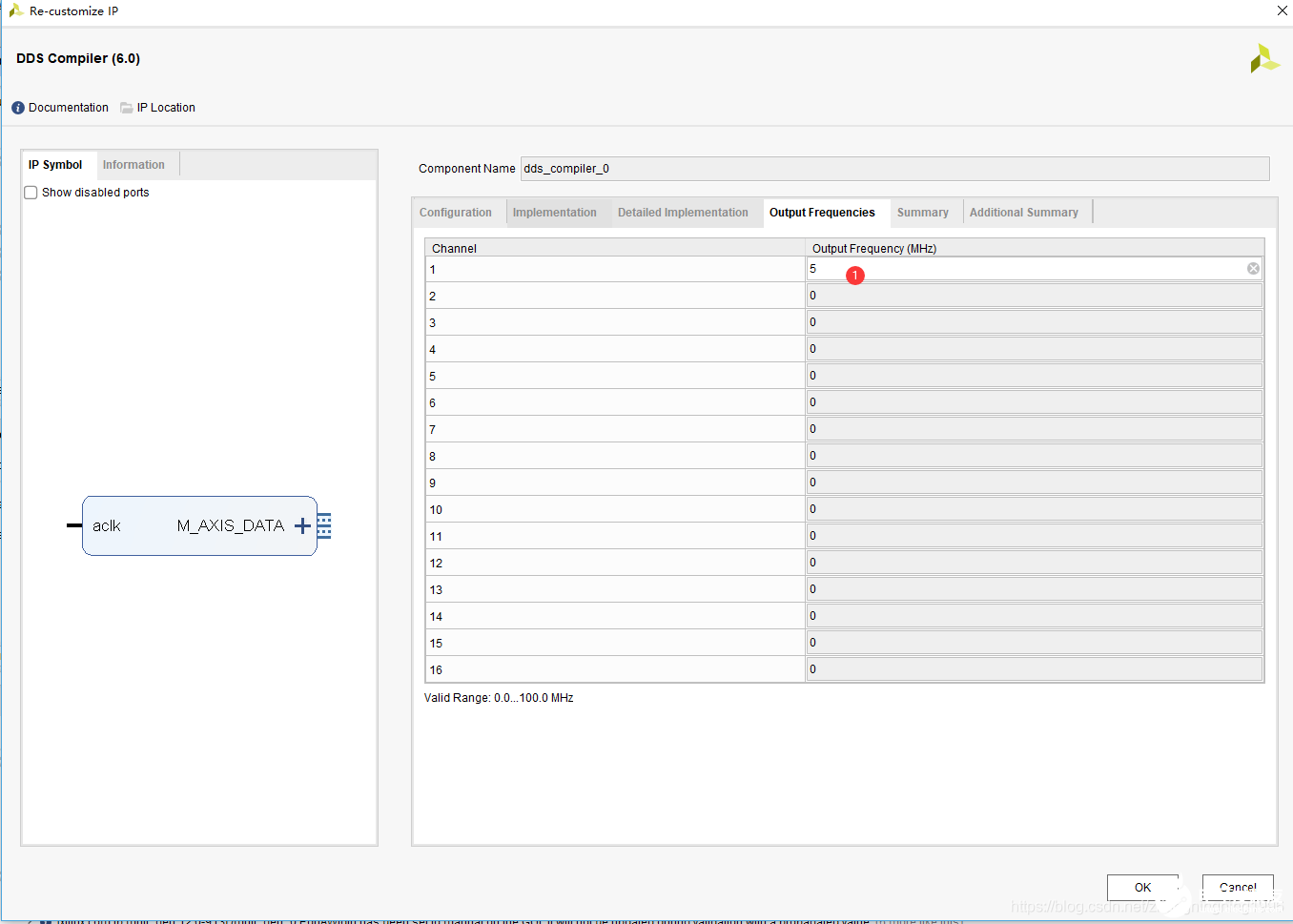

1、输入我们需要DDS输出的频率,这里我们输入5MHz。

其余选项,我们选择默认即可。这样,我们便定制了一个完整的DDS IP核,接下来的博客我们会自己手写相应的DDS的功能,感兴趣的同学可以保持关注。

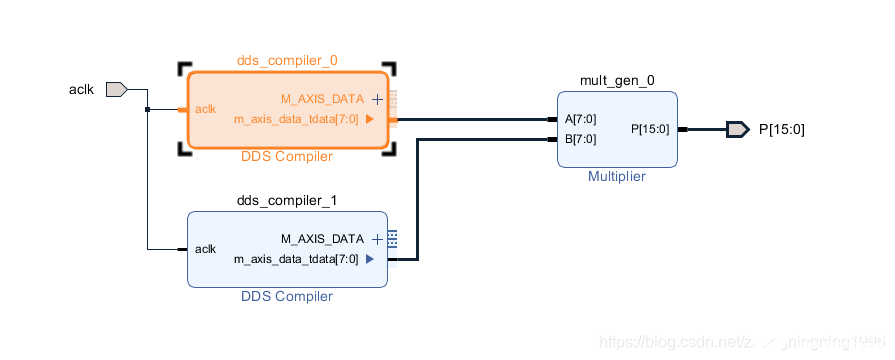

Block Design涉及

我们这边博客首次引入了block design的设计方法,但是这个设计方法特别重要,希望同学们可以好好学习。进行block design的连线图如下:

然后验证设计的有效性,产生输出工程,生成相应的top文件,供我们接下来的设计使用。

测试文件代码

这里我们为了验证我们实验的正确性,给出相应的测试模块。

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2020/04/03 22:39:17 // Design Name: // Module Name: tb // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module tb; wire [15:0] P ; reg aclk ; initial begin aclk = 1‘b0; end always #5 aclk = ~aclk; system_wrapper system_wrapper_inst( .P (P ), .aclk (aclk ) ); endmodule

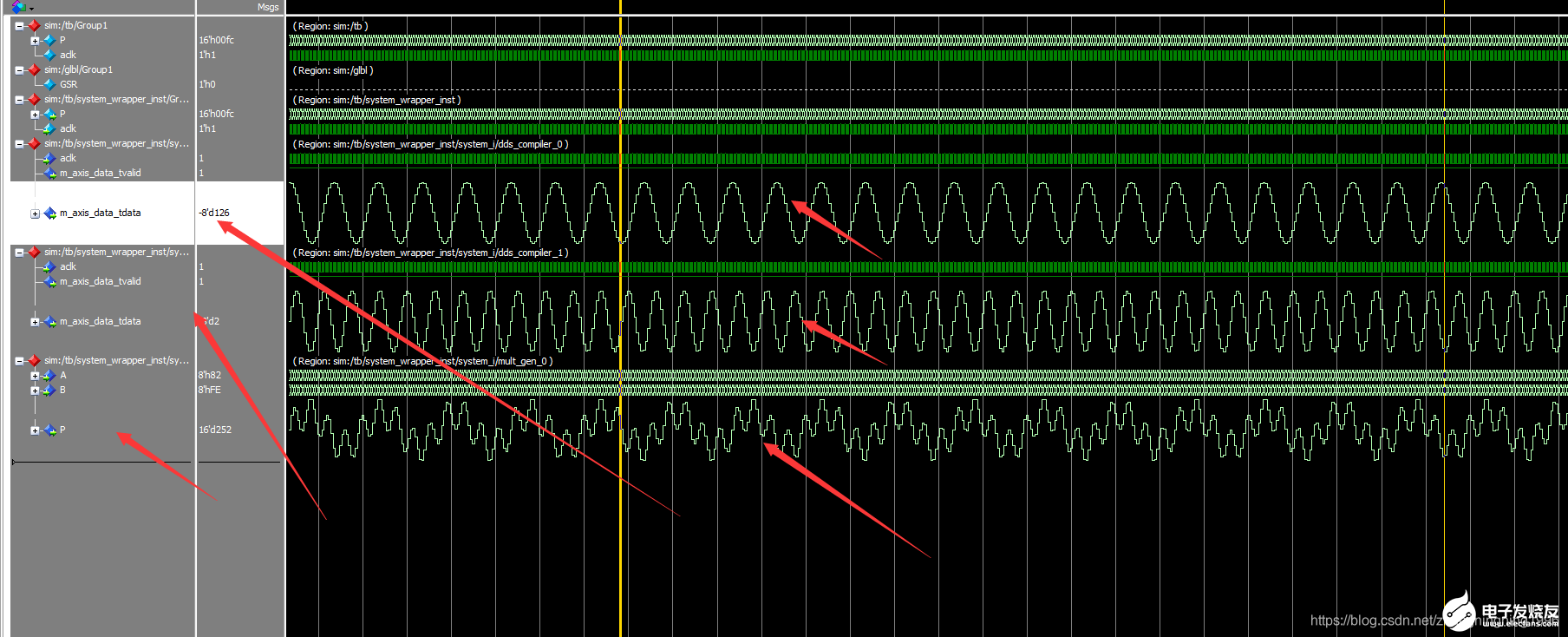

仿真结果

我们进行Modelsim仿真测试的结果如下:

从上面的仿真波形可以验证我们实验的准确性。

编辑:lyn

-

Xilinx DDS IP核的使用和参数配置2024-10-25 6653

-

XILINX FPGA IP之DDS Compiler_ip例化仿真2023-09-07 5017

-

Xilinx Vivado DDS IP使用方法2023-07-24 8946

-

如何使用Xilinx DDS Compiler IP并把它运行在Ultra96板上的可编程逻辑中?2023-02-08 1599

-

关于Ultra96的Xilinx DDS编译器IP教程2022-12-13 1388

-

Gowin DDS IP用户指南2022-09-16 796

-

Vivado中xilinx_courdic IP核怎么使用2021-03-03 6959

-

Xilinx Logicore IP直接数字合成器DDS的用户手册免费下载2019-09-09 1354

-

请问DDS ip是否允许控制生成波形的相移?2019-04-04 1984

-

如何使用DDS IP核生成任意波形?2019-02-12 6275

-

Xilinx CORE生成器IP列表名称及说明详解2017-11-18 5635

-

xilinx dds IP核输出能不能改为无符号数2015-09-29 7433

-

我用的是xilinx ISE 12.4 ,想问一个关于dds IP 核的问题2015-02-18 5595

-

IP core调用DDS2013-03-20 3035

全部0条评论

快来发表一下你的评论吧 !