为什么有时候FIF不能正常工作?

描述

同步控制信号

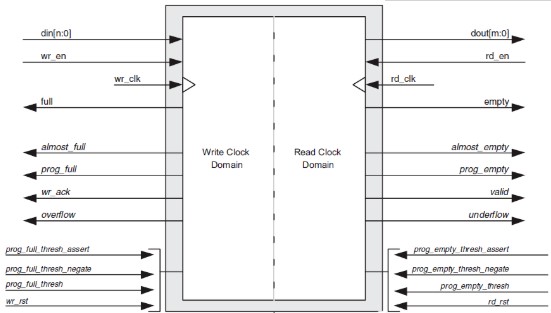

对于读/写时钟相互独立的FIFO(读/写时钟独立意味着这两个时钟是异步的,例如来自于不同的MMCM),要确保相应的控制信号只在与之对应的时钟域内被使用。如下图所示,除了rst对整个FIFO进行异步复位外,其余信号都与各自的时钟同步。例如:写使能wr_en、写数据din都与写时钟wr_clk同步;读使能rd_en、读数据dout都与读时钟rd_clk同步。和“满”相关的状态信号如full/almost_full等都与wr_clk同步;和“空”相关的状态信号如empty/almost_empty等都与rd_clk同步。

复位信号 对于读/写时钟独立的FIFO,FIFO Generator提供了复位信号,用于对所有的状态输出信号进行复位,如下图所示。这里复位信号是可选的。如果下图选项1不勾选,那么选项2和选项3则不可见,此时FIFO没有复位信号。如果勾选1,此时选项2和选项3可见,且默认均被勾选,这意味着rst尽管是异步的,但在使用时会被wr_clk和rd_clk先同步到各自的时钟域。如果勾选1,但不勾选2,此时读/写时钟域会分别有各自的复位信号wr_rst和rd_rst。当wr_rst有效时(高有效),写时钟域处于复位状态;当rd_rst有效时,读时钟域处于复位状态。由此可见,对于读/写时钟独立的FIFO,异步复位rst和同步wr_rst/rd_rst是可选的。这意味着FIFO可以没有复位信号,也可以只用一个异步复位信号rst,或者用同步复位wr_rst/rd_rst。

原文标题:你的FIFO为什么不能正常工作

文章出处:【微信公众号:Lauren的FPGA】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

ADS1191采集内部测试信TEST1Hz方波,有时候hen正常有时候不正常,是哪里出了问题?2024-12-30 359

-

MCUISP下载时候为什么有时候能下载成功 有时候不行2014-11-23 2859

-

为什么有时候覆铜的时候不能连接到器件的GND引脚 还有怎么解决这个问题2016-04-28 15124

-

动态事件注册,事件停止的句柄放入功能型全局变量,程序有时候能正常停止,有时候使用就无法正常停止是什么原因?2018-05-28 3265

-

动态调用 x40 x80,有时候不能正常退出是什么原因?2018-06-11 3131

-

28335有时候不能正常上电,程序跑飞2018-09-14 7930

-

怎么有时候发帖审核有时候又不审核啊?2018-12-27 1429

-

AD7606为什么有时候读的数据全为0,有时候正常采集2018-12-28 7076

-

为什么以太网有时候不能通ping?2019-09-10 2532

-

STC15W1K16S单片机程序为什么有时候会掉2020-04-01 1930

-

FPGA程序烧录有时候成功有时候失败2021-06-21 6477

-

为什么CH376识别U盘的时候有时候很快就能识别,有时候基本识别不了 ?2022-07-11 1683

-

AD7708转换结果时而正常,有时候变得特别慢的原因?怎么排查?2023-12-04 504

-

为什么AD7606有时候读的数据全为0,有时候正常采集?2023-12-18 754

-

晶振有什么作用,如何选择合适的晶振,为什么有时候用内部晶振?2023-11-27 2379

全部0条评论

快来发表一下你的评论吧 !