浅谈PYNQ中的Vitis HLS前端开源

描述

目前,虽然基于C/C++等高层次综合相较于手写RTL层级HDL语言已大幅提升了开发效率,但随着相关技术的不断进步,以及算法迭代的日益频繁,人们似乎并不满足于此。

不少刚刚接触到Pynq的用户第一个问号

Pynq是不是用Python编程FPGA的新物种?

在Pynq的FAQ中,我们强调的第一个重点就是PYNQ是一个开源框架而不是一个直接用Python编程FPGA的工具。但是,在不远的将来,我们也许就要修改这条FAQ了。

因为在2月28日,Vitis HLS工具前端开源了!!!

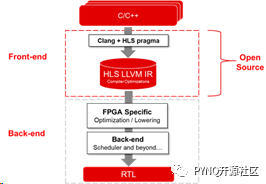

这是Xilinx的开源战略和承诺的一部分,通过Vitis HLS工具链前端开源可以

Add support for new high-level languages beyond C/C++ and OpenCL

Add new domain-specific optimization pragmas or compiler directives

Customize the transformations to the LLVMIR (new LLVM passes)

这意味着,软硬件开发人员可以灵活地使用标准的 Clang / LLVM 基础架构,支持自由扩展,也可以定制高层次综合 (HLS) 编译过程的前端。

例如,自定义语言支持和全新特定于应用的编译器指令,以及更多的可能性。

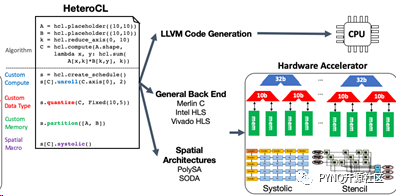

研究人员早就在开始探索增加Python高层次综合。例如2019年,Themefisher和康奈尔大学联合推出了HeteroCL。

HeteroCL是一种编程基础结构,由基于Python的域特定语言(DSL)和编译流程组成,其编译器在CPU上生成LLVM代码。

因此可通过结合最新的HLS优化(例如用于脉动阵列的PolySA和用于模板的SODA与数据流体系结构),产生高效的空间体系结构。

将来要发生的事情,大家应该都有自己的想象空间了

编辑:lyn

-

使用AMD Vitis Unified IDE创建HLS组件2025-06-20 2554

-

如何使用AMD Vitis HLS创建HLS IP2025-06-13 2252

-

Vitis HLS移植指南2023-09-13 595

-

如何在Vitis HLS GUI中使用库函数?2023-08-16 2487

-

AMD全新Vitis HLS资源现已推出2023-04-23 1934

-

带有PYNQ和Vitis HLS的SHA256加密加速器2023-02-09 1543

-

使用Vitis HLS创建属于自己的IP相关资料分享2022-09-09 5561

-

FPGA高层次综合HLS之Vitis HLS知识库简析2022-09-07 3857

-

Vitis HLS知识库总结2022-09-02 4962

-

Vitis HLS前端现已全面开源2022-08-03 1817

-

开启无限可能的世界:Vitis HLS 前端现已全面开源2022-08-02 1720

-

Vitis HLS工具简介及设计流程2022-05-25 3748

-

基于Vitis HLS的加速图像处理2022-02-16 3462

-

Vitis HLS前端现已在GitHub上全面开源,开启了无限可能的新世界2021-03-24 4595

全部0条评论

快来发表一下你的评论吧 !