关于SoPC的星载微波辐射计的数据采集系统

电子说

描述

摘 要: 应用MC8051软核处理器,在FPGA上设计实现了基于软核的辐射计的科学数据采集,并通过1553B总线将数据传送到地面接收的采集系统。该方案在Xilinx公司FPGA芯片XC2V3000上得到了验证,满足航天星载微波辐射计多通道高分辨率的要求。

微波辐射计是一种高灵敏度的接收机,其对科学数据和温度等辅助数据的采集精度和速度都要求较高。片上可编程系统的高效性和灵活性可以充分满足微波辐射计的高分辨率、高采样率的多通道快速数据采集要求,提高了辐射计数据采集和控制的效率。

1 系统结构

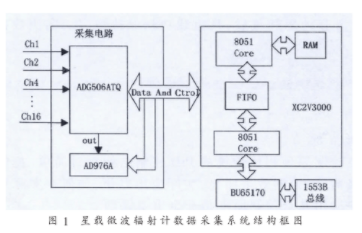

所述多通道高分辨率辐射计采集系统共16个输入通道,Ch1~Ch16为16路采集通道输入,采集模拟电平范围为-10 V~10 V。其系统结构框图如图1所示,由多路选通AD转换电路、FPGA电路和通信电路3个部分组成,多路选通AD转换电路部分由多路选通芯片ADG506ATQ和AD转换芯片AD976A组成。通道采集电信号由ADG-506ATQ选择需要采集的电信号输出到AD转换芯片进行转换,这样只需要使用1片AD芯片即可分时采集16个通道的信号,大大节省了AD的芯片数,降低了硬件的成本和复杂度。

AD976A是ADI公司生产的模数转换器,具有功耗低、速度快、精度高等特点,采集精度达到16 bit。单通道最高采样速率达200 kS/s,16 bit的分辨率,最大积分非线性误差仅为2 LSB,并可做到16 bit不失码,在输入电压为-10 V~10 V的条件下达到的采集精度为0.003 V,高灵敏度的星载微波辐射计需要的采集精度为±3 mV,采用该芯片有效地保证了采集的精度。

1.1 MC8051 IP核的结构

嵌入式片上可编程系统SoPC包括硬核处理器和软核处理器两种类型[1],本星载辐射计多通道高分辨率数据采集系统采用的处理器属于软核处理器。

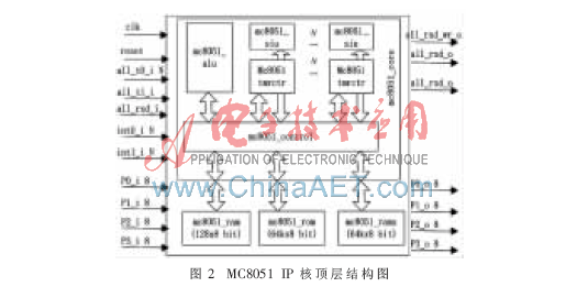

MC8051 IP核顶层结构图如图2所示,核心由定时器/计数器、ALU、串行接口和控制单元各模块组成。ROM 和RAM 模块不包括于核心内,处于设计的顶层,方便不同的应用设计及仿真。

图3为综合后时序报告的一部分,给出了Mc8051_core的时序。可以看到,虽然设计中处理器以12 MHz的时钟频率运行,但其最大路径延时仅为3.359 ns,所以处理器软核在此芯片中理论上最高可达到297.681 MHz的频率。

1.2 数据采集系统电路实现

1.2.1 FPGA部分电路设计

FPGA电路部分由两个8051软核、RAM和FIFO组成。其中第一个软核处理器负责分时选择16路通道的数据并控制AD转换芯片转换成数字信号,按顺序存储到FIFO中,供第二个8051软核处理器读取。第二个软核处理器则负责将存储到FIFO的采集数据按照一定的数据格式形成数据包,通过BU65170控制的1553B总线下传给地面接收站供后期使用和处理。1553B是目前通用的星上设备通信总线,通过该总线进行通信保证了数据的可靠传输。

1.2.2 多通道AD转换电路设计

多通道选择AD转换电路如图4所示。电路的供电为±12 V两路,输入通道信号为±10 V的电压,经ADG506选通一路输入到AD976,由8051核处理器给一个转换脉冲启动AD转换,转换结束后AD976的数据线即输出转换后的数字信号,再由8051核处理器读取,存储到FPGA内部的FIFO里[2]。

1.2.3 1553B通信接口设计

1553B通信接口的实现选用了DDC′s ACE/Mini-ACE系列的BU-65170芯片。该芯片在FPGA和MIL-STD-1553B总线之间提供了完整、灵活的接口,完整的BC/RT/MT多协议、存储器管理和中断逻辑,4K×16字(每字16 bit)的静态分配内存作为到处理器总线的接口。本文选用的是BU-65170的远程终端模式(RT)[3]。

Bu-65170可选择在12 MHz和16 MHz两种时钟频率下工作,集成了编码/解码器,双收发器和协议处理器,数据按一定的协议经编码/解码器处理,通过双收发器A/B 来完成与1553B总线间的数据传递,数据的传输速度最大可达1 Mb/s[4]。

2 数据采集系统软件设计

软件采用汇编语言开发,使用MedWin平台。选择汇编语言的原因是:它可以直接对寄存器进行操作,与自定义的51软核处理器可以进行更好的配合。另外,汇编语言的每一条命令执行时间可以准确判断,这使其可以更好地满足设计中对于精确时间控制的要求。

指令执行时间为1~4个时钟周期,如果采用12 MHz频率的时钟,一个时钟周期为83 ns左右。两个8051核处理器之间有一个握手的过程,其中采集8051软核处理器会给出一个通知读取数据包的中断信号,通知通信的8051软核处理器读取FIFO的采集数据包。采集软核处理器程序流程图如图5所示,FPGA程序流程图如图6所示。

采用最通用Modelsim进行仿真。图7为FIFO数据读写仿真结果。两幅图中自上至下的信号依次为输入数据、输出数据、空标识、满标识、半满标识、读时钟、读使能、写时钟、写使能。图7(a)为向FIFO写数据的过程,读时钟不变,空标识在有数据输入之后变为‘0’。图7(b)为从FIFO读数据的过程,在半满标识有效后,通信模块处理器开始输出读时钟读出数据。从图中可以看到写入和读出的数据相符。

3 数据采集系统仿真与调试

图8是对BU-65170芯片寄存器区写入初始化参数的一部分。图中S_SELECT信号为片选信号,strbd为数据有效信号,最后一组信号为写入数据。由于持续为写状态,所以RD信号保持不变。

结果表明,FPGA各模块工作正常,符合设计要求。

本文结合航天应用的星载微波辐射计工程实现的要求,讨论了基于微波辐射计的多通道、高分辨率数据采集系统的原理,并采用现场可编程门阵列(FPGA)和片上可编程系统SoPC的8051软核处理器实现了该数据采集系统的硬件设计和FPGA模块设计,进行了部分模块的功能仿真和时序仿真,通过了系统调试仿真验证,实现了设计的目的。

参考文献

[1] 郭兵,沈艳,林永宏,等.SoC技术原理与应用[M]。北京:清华大学出版社,2006.

[2] 孙茂华,郑震藩,张升伟,等。风云三号卫星微波湿度计数据处理与系统控制的冗余设计方案[J]。遥感技术与应用,2007,22(2):147-151.

[3] DDC公司.ACE/Mini-ACE series BC/RT/MT advanced communication engine Integrated 1553 terminal user′s guide[Z].2007.

[4] DDC公司.MIL-STD-1553 designer′s guide[Z].1998.

编辑:jq

-

基于ARM和FPGA的气象微波辐射计测控系统2021-06-11 879

-

基于C8051F020单片机实现多波段光谱辐射计采集系统的设计2020-06-27 1450

-

采用单片机实现微波辐射计数控单元2019-06-03 2340

-

微波辐射计论文资料2019-03-04 2295

-

微波辐射计定标注入噪声特性分析与校正2018-04-03 999

-

天线转动的微波辐射计数控单元设计2017-12-10 1367

-

一种简便的全极化微波辐射计天线方向图校正算法2017-10-31 1329

-

微波辐射计新型检波器研究(以ADL5391为核心)2017-10-28 1331

-

基于SOPC技术的数据采集系统设计2016-02-17 1197

-

基于FPGA的狄克型辐射计数据采集系统设计2015-12-18 679

-

基于SOPC的数据采集与处理系统设计2012-05-23 2236

-

SOPC基础上的数据采集系统设计2011-07-04 1504

-

基于FPGA的微波辐射计数控系统设计与实现2010-07-28 540

-

基于51单片机控制的高精度微波辐射计天线伺服系统2010-07-13 559

全部0条评论

快来发表一下你的评论吧 !