浅述ZYNQ-AXI总线的信号接口要求以及时序关系

描述

学习内容

学习关于AXI总线的信号接口的具体要求(包括不同通道之间的关系,握手机制说明等)和AXI4-Lite的相关信息,在文章后半部分对AXI读写时序进行了简要讲解,主要针对ARM公司的IHI0022D进行阅读总结。

Clock and Reset

前面也提到了信号和复位的功能,这里对AXI全局时钟(ACLK)和复位信号(ARESETn)做进一步的解释说明。Clock:每个AXI组件都要使用时钟信号(ACLK)。

所有的输入信号都在ACLK的上升沿上采样。

所有输出信号的变化必须发生在ACLK上升沿之后。

在主机接口和从机接口上,输入和输出信号之间不能有组合路径。

Reset:AXI使用一个单独的低复位信号(ARESETn)。复位信号可以进行异步复位,但是复位完必须与ACLK的上升沿同步。在复位过程中,要求:

主机接口必须驱动ARVALID、AWVALID、和WVALID为低电平。

从机接口必须驱动RVALID和BVALD 为低电平。

所有其他信号可以为任何值。

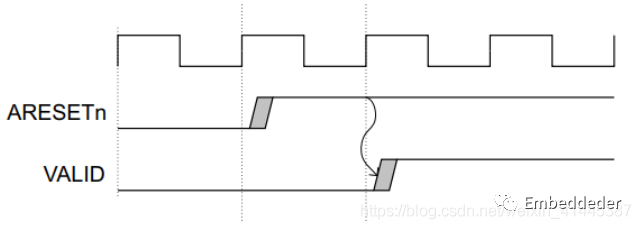

在完成复位后,允许master驱动ARVALID,、AWVALID、WVALID为高。但是上升沿信号是在ARESETn是拉高之后而且要在ACLK上升沿。如下图:

Basic read and write transactions

在基本的读写传输中,要完成正常的传输功能要进行握手并且遵守协议中对每个通道的信号的要求。

握手机制

所有五个通道都使用相同的VALID/READY握手处理来传输地址、数据和控制信息。这种双向握手机制表示主机和从机都可以控制信息在主机和从机之间传输的速率。

源端(master)生成VALID信号来指示地址、数据或控制信息何时传输可用。目的端(slave)生成READY信号来表示它可以接受该信息。传输只发生在VALID和READY信号都为高电平时。在主机接口和从机接口上,输入和输出信号之间不能有组合路径。

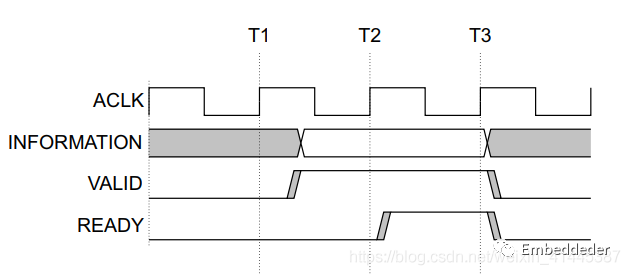

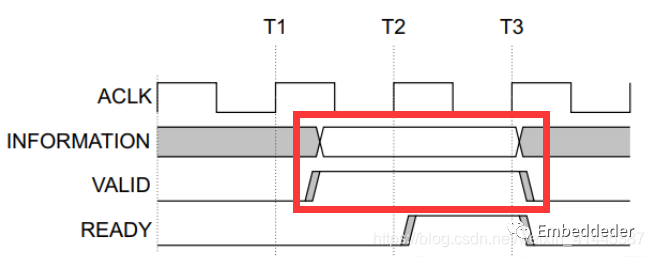

双向握手协议表示主机和从机都可以控制信息在主机和从机之间传输的速率。换句话说也就是在传输中VALID和READY,都可以进行等待对方从而完成数据传输。如下图所示,下图的VALID的上升沿在T1时刻之后完成拉高,在T2时刻VALID信号为高,而READY信号为低,所以要继续等待READY信号拉高。在T2时刻的上升沿之后,READY拉高,在T3时刻上升沿时,READY和VALID信号都为高,所以数据传输发生。也就是下图的数据传输发生在T3时刻。

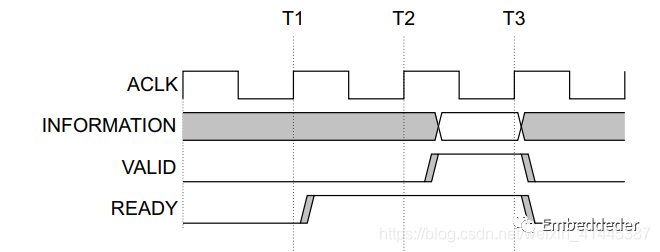

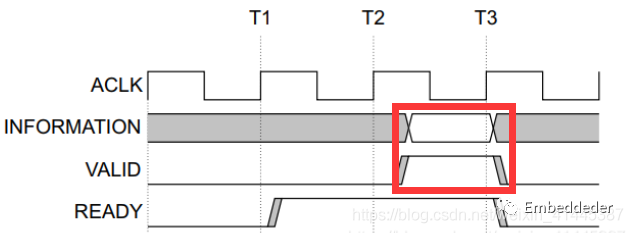

下图的分析方法同上,在T1时刻READY和VALID信号都为低,不进行数据传输;在T2时刻READY和VALID信号分别为高、低,不进行数据传输;在T3时刻READY和VALID信号都为高,进行数据传输。

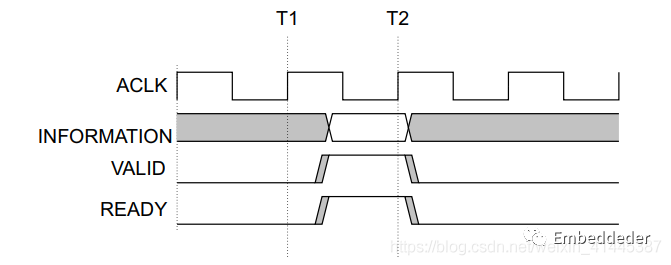

并且,READY和VALID可以同时设置为高进行数据传输,如下图,在T2时刻发生数据传输。

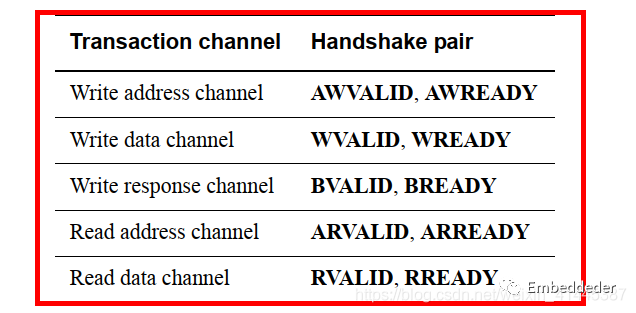

针对不同的信号通道,握手信号加上不同的前缀加以区分,如下表:

对于不同通道的握手信号,AXI协议有具体的建议要求:Write address channel主机可以在地址和控制信息都有效的时候拉高 AWVALID。当AWVALID拉高后要保持不变,直到AWREADY也拉高并且时钟产生上升沿之后。换句话说,在握手传输的时,我们的数据信息和地址信息要保持不变,这样才能确保传输的数据为有效可靠的。也就是AWVALID和信息数据是同步变化的。下面给出两个示例:

AWREADY的默认状态可以是高或者低。AXI协议建议的默认状态为高。当AWREADY为高时,从机能够接受任何提供给它的有效地址。不建议默认AWREADY状态为低,因为它强制进行握手传输,至少需要两个时钟周期,一个周期拉高AWVALID,另一个周期拉高AWREADY。

Read address channel和上面的写地址通道要求类似,主机可以在地址和控制信息都有效的时候拉高 AWVALID。当AWVALID拉高后要保持不变,直到AWREADY也拉高并且时钟产生上升沿之后。WREADY的默认状态可以是高或者低。AXI协议建议的默认状态为高。当AWREADY为高时,从机能够接受任何提供给它的有效地址。不建议默认AWREADY状态为低,因为它强制进行握手传输,至少需要两个时钟周期,一个周期拉高AWVALID,另一个周期拉高AWREADY。

Write response channel当它驱动有效的写响应时,从机才能拉高BVALID信号。当BVALID拉高后要保持不变,直到BREADY也拉高并且时钟产生上升沿之后。BREADY的默认状态可以是高电平,但前提是在主机总是能够在一个周期内接受写响应的情况下。

Write data channel:在写突发传输期间,当主机驱动有效的写数据时,才需要拉高WVALID信号。当WVALID拉高后要保持不变,直到WREADY也拉高并且时钟产生上升沿之后。WREADY的默认状态可以是高电平,但前提是从机总是能在一个周期内接受写数据。当主机在突发传输中进行最后一个数据传输时,必须拉高WLAST信号,用于指示传输结束。

Read data channel:当它驱动有效的读数据时,从机才能拉高RVALID信号。当RVALID拉高后要保持不变,直到RREADY也拉高并且时钟产生上升沿之后。即使从机只有一个读数据信息,它也必须在响应数据请求时拉高RVALID信号。主机接口使用RREADY信号来表示它接受数据状态。RREADY的默认状态可以为高电位,但前提是无论何时启动读操作,主机都能立即接受读数据。当从机在突发传输中进行最后一个数据传输时,必须拉高RLAST信号,用于指示传输结束。

通道之间的关系

AXI协议中需要保持以下关系:

在写操作中,写响应必须始终跟随它是其中一部分的最后一个写传输。

读取数据必须始终跟在与数据相关的地址后面。

通道握手必须符合在通道握手信号之间的依赖关系。

通道握手信号之间的依赖关系

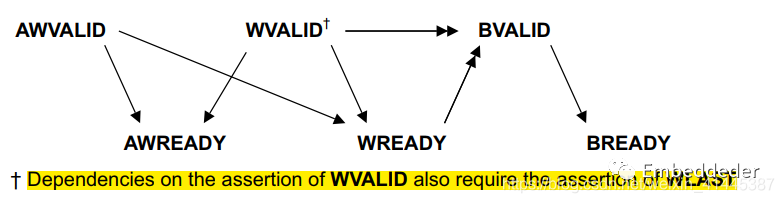

通道握手信号之间的依赖关系,,由下面的流程图进行描述,这里先进行图示说明:在依赖关系图中,单箭头指向可以在箭头指向的信号之前或之后拉高信号;双箭头指向的信号必须在箭头指向的信号断言之后才能拉高。

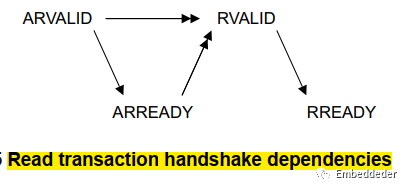

读操作依赖关系

上图显示读操作握手信号的依赖关系,在读操作中:

从机必须等待ARVALID和ARREADY都拉高后,RVALID才能进行拉高指示数据有效。

对于ARVALID和ARREADY的顺序,可以任意设置先后顺序,从机可以等待ARVALID拉高后,再拉高ARREADY,也可以相反,也可以同时拉高。

对于RVALID和RREADY不用关心顺序,主机可以任意设置先后顺序。可以先后,可以同时。

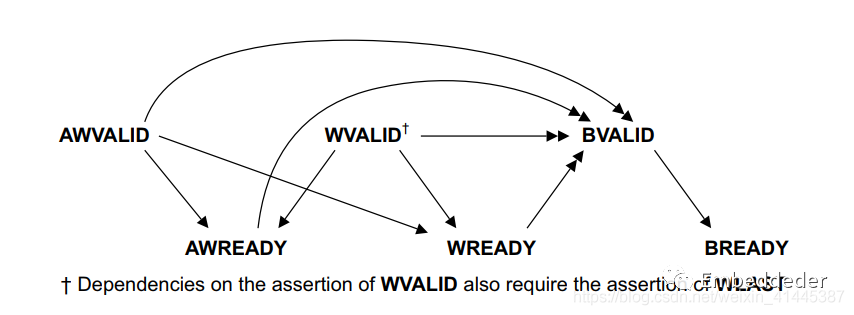

写操作依赖关系

上图显示写操作握手信号的依赖关系,在写操作中:

主机在拉高AWREADY or WREADY不需要关心从机AWVALID or WVALID先后顺序。

从机在BVALID拉高之前,WVALID和WREADY必须被拉高。

从机必须WLAST拉高之后,才能拉高BVALID,因为写响应(BRESP)在写操作的最后一次数据传输之后,才发出信号。

从机不用关心BVALID和BREADY的先后顺序。

写响应依赖关系

上图显示写响应握手信号的依赖关系,在写响应中:

单头箭头指向可以在箭头指向的信号之前或之后拉高信号

从机须等待AWVALID、AWREADY、WVALID和WREADY都拉高之后,BVALID才能拉高使能。

从机必须WLAST拉高之后,才能拉高BVALID,因为写响应(BRESP)在写操作的最后一次数据传输之后,才发出信号。

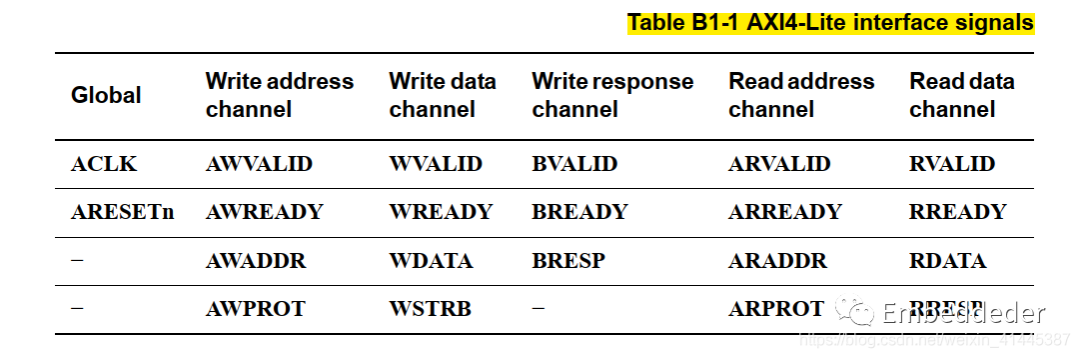

AXI4-Lite协议

AXI4-Lite和AXI4类似,当不需要完整AXI4功能的时,进行一些简单的控制寄存器的读写。AXI4-Lite协议简单描述如下:

AXI4-Lite协议的所有传输的突发长度都是1(相当于不支持突发传输)。

所有数据访问都使用数据总线的全部位宽,支持32位或64位的数据总线宽度。

所有访问都是不可修改的,不可缓冲的。

不支持独占访问。

接口定义

相比前面介绍的AXI4-Full,这里的信号端口就少了很多。但对于相同名字的接口信号含义是相同的,功能相同。

AXI总线协议时序

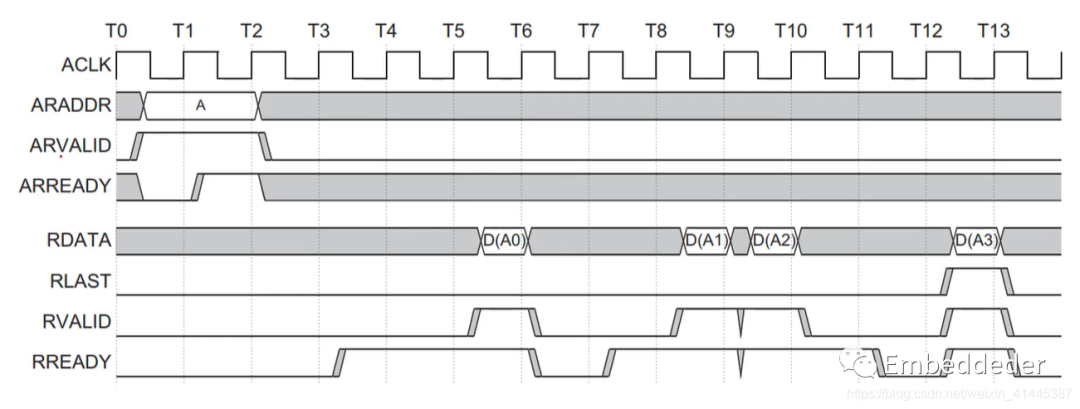

AXI突发读

下图所示,当ARVALID信号和ARREADY信号都拉高时地址有效(地址信息和ARVALID是同步的),也就是在T2时刻读取到所要读取的地址,然后等待RVALID和RREADY都拉高,即可读取到数据,也就是在T5时刻内读取到第一个数据A0(数据和RVALID是同步的),依次读取A1、A2、这里的时序图定义A3为最后一次传输,所以RLAST也被拉高。

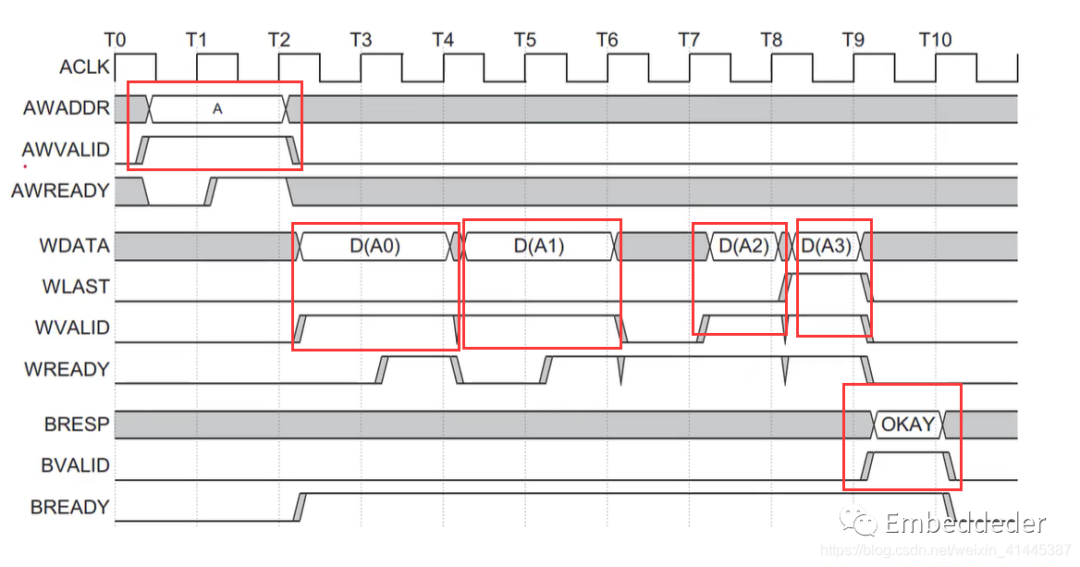

突发写

下图所示,当AWVALID信号和AWREADY信号都拉高时地址有效(地址信息和AWVALID是同步的),也就是在T2时刻上升沿读取到所要写入的地址。然后主机发送写入的数据(数据和WVALID信号是同步的),依次写入A0、A1、A2、A3,当写入最后一个数据时,WLAST信号也要拉高,当写操作完成后,从机要发送一个响应信号,这个信号也是在BVALID和BREADY为高时有效。

编辑:jq

-

AXI总线工作流程2023-05-25 2018

-

ZYNQ-7000系列MIO、EMIO、AXI_GPIO接口2022-07-25 3736

-

AXI接口协议详解2022-04-08 6029

-

浅谈ZYNQ-AXI总线的信号接口要求以及时序关系2021-06-01 3718

-

全面介绍ZYNQ-AXI互联IP2021-05-11 8198

-

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口2021-01-31 1876

-

Xilinx zynq AXI总线全面解读2020-12-04 9382

-

ZYNQ中DMA与AXI4总线2020-11-02 5334

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7582

-

玩转Zynq连载38——[ex57] Zynq AXI HP总线带宽测试2019-11-28 4926

-

玩转Zynq连载37——[ex56] 基于Zynq的AXI HP总线读写实例2019-11-26 4208

-

玩转Zynq连载34——[ex54] 基于Zynq的AXI GP总线的从机接口设计2019-11-12 5365

-

AXI总线协议的几种时序介绍2019-05-12 11903

-

玩转Zynq连载3——AXI总线协议介绍12019-05-06 2799

全部0条评论

快来发表一下你的评论吧 !