探讨VHDL和Verilog模块互相调用的问题

描述

1、关于如何在VHDL模块调用一个Verilog模块

在VHDL模块声明一个要与调用的Verilog模块相同名称的元件(component),元件的名称和端口模式应与Verilog模块的名称和输入/输出模式相同。注意Verilog区分大小写,VHDL不区分,所以模块名字一定要完全一致,不能搞混。

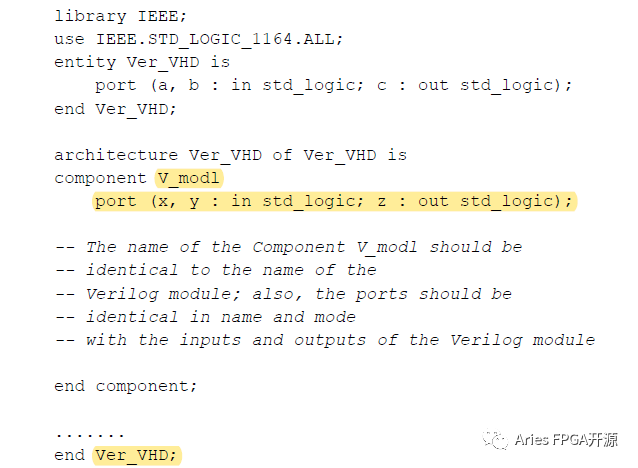

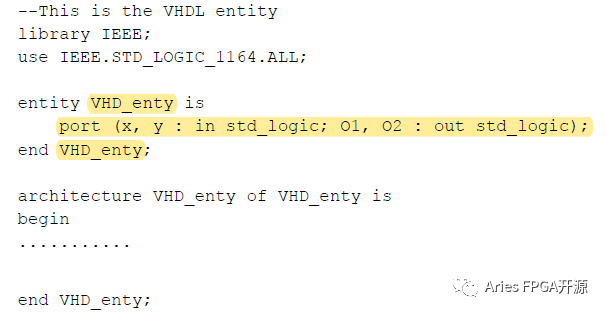

举个例子:下面是一个VHDL模块,在里面声明了一个元件(component)

看Verilog模块再

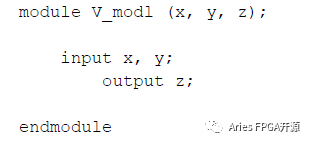

VHDL的模块就是通过声明一个元件(component)来调用这个Verilog模块,将元件声明提出来讲,如下图:

对比这个Verilog模块和VHDL中声明的元件不难发现,模块名/端口/输入输出模式完全一样,这和VHDL自己调用用VHDL的元件(component)基本一样。

2、关于如何在Verilog中调用VHDL模块

在Verilog中,通过在Verilog模块中输入其名称(标识符)及端口来调用VHDL实体。模块的参数应该与实体的类型和端口的方向匹配,可以映射到Verilog模块的VHDL端口为:in,out和inout;在某些模拟器中,不允许使用缓冲区。Verilog模块只能使整个VHDL实体可见。

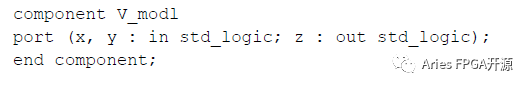

举个例子:下图是一个Verilog模块调用了VHDL模块(高亮处)

下图是一个VHDL模块

Simulator(模拟器,注:这个是英文原版使用的词语,我的理解就是一些EDA)首先在Verilog模块中查找,以查看是否有任何名为VHD_enty的Verilog模块。如果找不到,模拟器将在VHDL实体中查找。当模拟器找到名称为VHD_enty的实体时,它将该实体绑定到Verilog模块。在代码中,输入a被传递到输入端口x;输入b传递给输入y。VHDL实体计算输出O1和O2;这两个输出分别传递到Verilog输出c和d。调用VHDL模块与调用功能或任务非常相似。

例子举完了,下面验证一下

验证:在Verilog中调用VHDL模块实体(VHDL调用Verilog考虑到比较简单,大家用的更多是Verilog,就不举例子了)

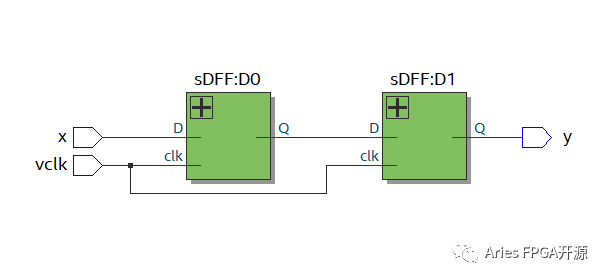

验证内容:使用Verilog调用两个VHDL写的D触发器模块实现打两拍。

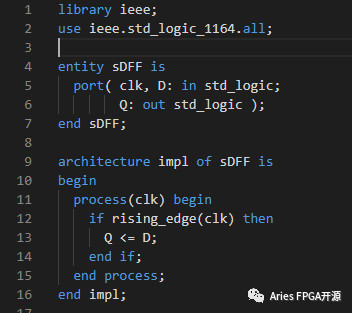

这个代码是一个用VHDL语言写的D触发器模块,在FIFO中也写过。

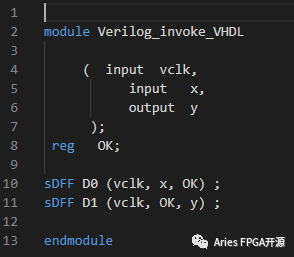

这个代码是Verilog写的,在内部调用两个由VHDL写的D触发器,实现两级D触发器。

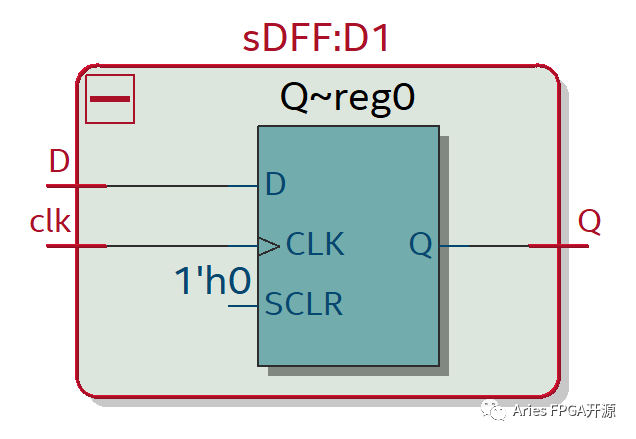

上图是VHDL写的D触发器综合出的原理图,注意对应的端口。

上图是Verilog代码综合出来的原理图,从代码上看,定义了vclk、x、y三个端口,连接VHDL写的两个D触发器,基本的调用过程就是这样。

总结:两者的互相调用过程都不复杂,举个基础的例子只是为了大家熟悉这个过程。在实际中难免会遇到有互相调用的地方。

编辑:jq

-

verilog模块的调用、任务和函数2025-05-03 1765

-

Verilog与VHDL的比较 Verilog HDL编程技巧2024-12-17 3473

-

verilog如何调用其他module2024-02-22 8911

-

例说Verilog HDL和VHDL区别2023-12-20 6321

-

verilog无法直接调用vhdl的ngc文件咋办?2023-03-30 1858

-

vhdl转换为verilog_VHDL和Verilog谁更胜一筹2020-08-25 7819

-

在verilog中调用VHDL模块2018-07-03 2912

-

VHDL与Verilog互转的软件2016-06-03 748

-

nTrace中的信号添加的nWave中报路径错误(Verilog VHDL mix)2016-01-10 3871

-

用VHDL调用verilog时遇到一个神奇的问题2015-01-14 4372

-

vhdl顶层模块可以调用子模块内部定义的信号吗?2013-08-08 7549

-

怎样在Verilog写的testbench测试VHDL模块??2013-08-01 7817

-

顶层调用子模块的VHDL例程2011-05-27 2694

-

VHDL和Verilog HDL语言对比2010-02-09 10954

全部0条评论

快来发表一下你的评论吧 !