RTL中多时钟域的异步复位同步释放

描述

1 多时钟域的异步复位同步释放

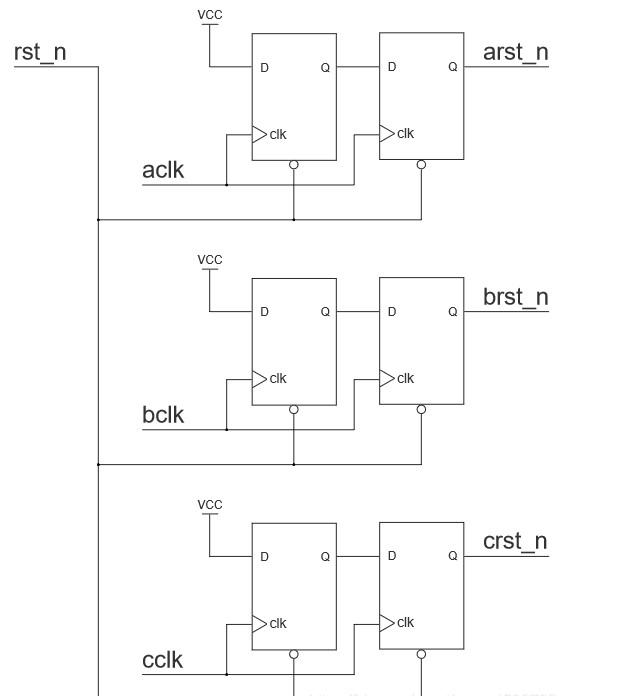

当外部输入的复位信号只有一个,但是时钟域有多个时,使用每个时钟搭建自己的复位同步器即可,如下所示。

verilog代码如下:

module CLOCK_RESET( input rst_n, input aclk, input bclk, input cclk, output reg arst_n, output reg brst_n, output reg crst_n );

reg arst_n0,arst_n1;reg brst_n0,brst_n1;reg crst_n0,crst_n1;

always @(posedge aclk or negedge rst_n) if(rst_n==0) begin arst_n0《=1‘b1; arst_n1《=1’b0; arst_n《=1‘b0; end else begin arst_n《=arst_n1; arst_n1《=arst_n0; end always @(posedge bclk or negedge rst_n) if(rst_n==0) begin brst_n0《=1’b1; brst_n1《=1‘b0; brst_n《=1’b0; end else begin brst_n《=brst_n1; brst_n1《=brst_n0; end always @(posedge cclk or negedge rst_n) if(rst_n==0) begin crst_n0《=1‘b1; crst_n1《=1’b0; crst_n《=1‘b0; end else begin crst_n《=crst_n1; crst_n1《=crst_n0; end endmodule

2 多时钟域的按顺序复位释放

当多个时钟域之间对复位释放的时间有顺序要求时,将复位同步器级联起来就可以构成多个时钟域按顺序的复位释放(实际上就是延迟两拍)。

verilog代码:

module CLOCK_RESET( input rst_n, input aclk, input bclk, input cclk, output reg arst_n, output reg brst_n, output reg crst_n );

reg arst_n0,arst_n1;reg brst_n0,brst_n1;reg crst_n0,crst_n1;

always @(posedge aclk or negedge rst_n) if(rst_n==0) begin arst_n0《=1’b1; arst_n1《=1‘b0; arst_n《=1’b0; end else begin arst_n《=arst_n1; arst_n1《=arst_n0; end always @(posedge bclk or negedge rst_n) if(rst_n==0) begin brst_n1《=1‘b0; brst_n《=1’b0; end else begin brst_n《=brst_n1; brst_n1《=arst_n; end always @(posedge cclk or negedge rst_n) if(rst_n==0) begin crst_n1《=1‘b0; crst_n《=1’b0; end else begin crst_n《=crst_n1; crst_n1《=brst_n; end endmodule

原文标题:RTL设计- 多时钟域按顺序复位释放

文章出处:【微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

异步复位异步释放会有什么问题?FPGA异步复位为什么要同步释放呢?2024-01-24 2958

-

FPGA学习-异步复位,同步释放2023-09-09 2407

-

浅析异步复位同步释放与同步复位打拍模块2023-08-21 1965

-

同步复位与异步复位的区别2023-08-14 8971

-

异步复位同步释放有多个时钟域时如何处理 异步复位同步释放的策略2023-07-20 2973

-

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?2023-06-21 2397

-

复位中的同步复位和异步复位问题2022-01-17 720

-

详细讲解同步后的复位是同步复位还是异步复位?2021-04-27 5974

-

异步复位同步释放的基本原理与代码举例2019-11-20 4947

-

FPGA设计中的异步复位同步释放问题2018-06-07 2646

-

关于异步复位同步释放理解与分析2017-11-30 25532

-

同步复位与异步复位,同步释放的对比疑问2014-04-16 2854

-

异步时钟域的亚稳态问题和同步器2010-07-31 1143

全部0条评论

快来发表一下你的评论吧 !