晶体管物理结构实现的两类协同优化技术探究

电子说

描述

当前,通过常规的晶体管尺寸微缩越来越难以获得理想性能增益,每一次集成电路工艺的进步都凝聚着产业链上下各个环节的辛劳成果。加州大学圣迭戈分校研究团队近期报导了针对CFET这一被认为是3nm以下必然采用的新型晶体管结构进行的前沿研究,探究了晶体管物理结构实现的两类协同优化技术,其成果有望加速CFET技术的成熟和应用落地。

研究背景

随着技术节点的不断进步,已服役十年的FinFET集成电路器件,其工艺单元设计工艺协同优化(DTCO)*由于布线空间和p-n横向排布间距受限而逐渐达到了工艺微缩的极限。因此,系统工艺协同优化(STCO)*概念被提出来,其典型应用代表是三维结构的Complementary-FET (CFET)晶体管,这种新型结构通过将p-FET堆叠在n-FET上实现工艺单元集成,减少单个工艺单元的面积占用。然而,CFET的标准单元(standard cell,以下采用文中简称“SDC”)设计要求从全局考虑以克服堆叠结构带来的高度限制,从而实现面积多小对晶体管性能最大化增益。

传统晶体管结构与互补型堆叠晶体管结构

针对CFET结构设计的问题,加利福尼亚大学圣迭戈分校(以下简称UCSD)的研究团队提出了一个基于可满足模性理论(SMT)的CFET标准单元的综合架构,解决了后端布局布线的优化问题。其成果以以“Complementary-FET (CFET) Standard Cell Synthesis Framework for Design and System Technology Co-Optimization Using SMT”为题发表于IEEE Transactions on VLSI Systems,UCSD计算机科学与工程学院与电子计算机工程学院联合团队的Chung-Kuan Cheng(陈中宪)、Chia-Tung Ho、Daeyeal Lee, Bill Lin, and Dongwon Park五人为共同通讯作者。

*设计工艺协同优化,全称Design Technology Co-optimization,是指芯片设计与制造共同合作,合作适配最适合芯片设计的晶体管结构和工艺的整体优化方案,以达到器件PPAC最优解的一种研发合作模式。

*系统工艺协同优化,全称System Technology Co-optimization,是指在系统集成层次进行优化的技术概念,一般STCO与系统级设计意义相近,即在先进封装中实现对die-to-die互连线路的微缩优化,而本文中讨论的则是单元(Cell)级内部线路优化和后道工艺中区块级(block-level)布线优化。

*Complementary-FET,一种新型晶体管结构,通过在垂直方向堆叠p型和n型晶体管实现CMOS结构。

*标准单元,standard cell是数字集成电路设计中最基本的逻辑单元。

*可满足模性理论,Satisfiability Modulo Theories,简称SMT,数学理论概念,在SAT布尔表达式(由运算符AND、OR、NOT和“()”构成,又称命题逻辑公式)可满足性理论基础上拓展了其他一阶逻辑表达式,常用于计算机科学领域研究。

研究内容

UCSD研究团队开发了一个自动化CFET SDC综合微缩框架,该框架支持track数量减少、设计规则改变和晶体管堆叠方案,优化了不同CFET SDC结构和设计规则,在以布通率为导向的研究思路下,最大限度利用了pin可达性(pin accessibility)和布通率(routability)。

除此之外,团队还研究了集成CSP问题*的SMT解决方案、针对MPL(最小I/O引脚长度)和MPO(最小I/0引脚孔)的单元优化技术等工作,并分析了p-on-n和n-on-p结构下2-4T布线高度*对于器件结构的影响并与传统晶体管结构进行了对比,以及DTCO在前沿技术节点中各类优化手段与后端工艺实现结果的相互作用。

*CSP问题,全称Constraint Satisfaction Problem,中文意为约束满足问题,CSP问题将其问题中的单元(entities)表示成在变量上有限条件的一组同质(homogeneous)的集合, 这类问题透过“约束补偿方法”来解决,是人工智能和运筹学的热门课题。

*布线高度,指一个标准单元的高度,用“数字+T”来表示,T指track,电信号的传输线路必须走在track上,数字表示track数量,即单元高度内允许布线的数量。

优化方案的整体框架

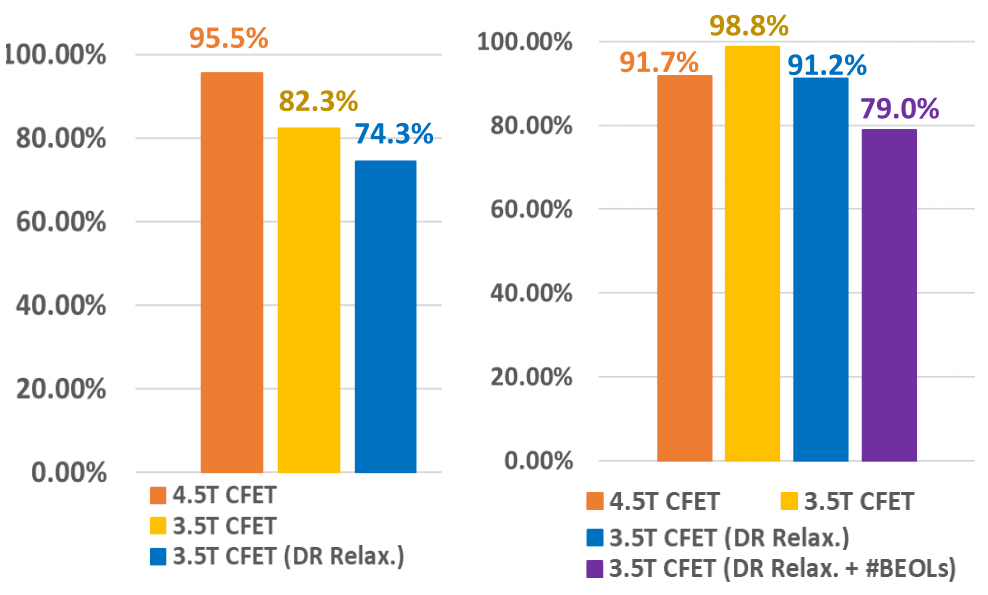

单元和模块级的面积缩放增益对比:

左为单元面积变化;右为模块级面积变化

研究团队通过实验发现与传统晶体管结构相比,微缩至3.5T高度的CFET结构的平均单元面积和金属长度分别减少了10.94%和21.27%,模块级平均面积减少了15.10%,并且大幅降低了DRV(Design Rule Violation)。

前景展望

文章介绍了沿着当前先进制程主要的三大实现路径,即:新器件结构、DCTO协同优化和系统级设计三个方向,针对CFET以及实现这一前沿新型晶体管结构性能增益必要的两大协同优化技术进行了探究。继IMEC等研究领域的排头兵提出和验证了新结构的可行性,业界已经认可了CFET的应用前景并全面跟进,包括英特尔、台积电-台湾TSRI-日本AIST、应用材料等企业和研究机构都开始着手布局相关的研究和技术储备,在常规的晶体管尺寸微缩越来越难以获得理想的性能增益的情况下,每一次集成电路工艺的进步都凝聚着产业链上下各个环节的研究成果,我们也期待着CFET等新技术的研发成功和应用落地那一天尽快到来。

原文标题:科研前线 | 未来会来吗?摩尔定律大杀器CFET研究又有新成果

文章出处:【微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

多值电场型电压选择晶体管结构2025-04-15 10373

-

c类放大器晶体管耐压多少2024-08-01 1330

-

什么是光电晶体管?光电晶体管的工作原理和结构2024-07-01 6149

-

晶体管电流的流动方向分析2023-07-06 7612

-

晶体管的结构特点和伏安特性2023-06-03 3995

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2553

-

芯片里面100多亿晶体管是如何实现的2020-07-07 3646

-

IGBT绝缘栅双极晶体管的基本结构与特点2019-03-27 2433

-

晶体管的开关作用有哪些?2018-10-25 4247

-

双极晶体管的基本结构2018-03-05 27950

-

晶体管的结构特性2013-08-17 3817

-

用棉线也能制作晶体管?2012-01-02 1190

-

双极晶体管的基础知识2010-08-29 1293

-

晶体管的结构及性能特点有哪些?2006-05-25 23454

全部0条评论

快来发表一下你的评论吧 !