简述烧写FPGA程序配置

描述

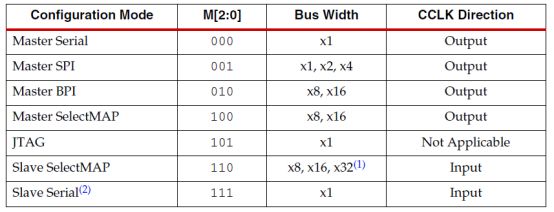

1. Master Modes

自动下载FPGA程序在本地的非易失性存储器,而且主模式的时钟来自内部晶振。

2. Slave Modes

外部控制下载FPGA配置模式,通常称为从模式,有串行和并行两种模式。在从模式中,控制程序下载可以是一个处理器,MCU,DSP处理器或者测试镜像。从模式的程序可以存放在整个系统的任意地方,比如flash,CPB板,以及主机处理器代码,磁盘或者一个网络连接设备中。

从模式中需要一个外部输入CCLK。

3. PUDC

当PUDC为低时,内部的上拉电阻使能在每一个SelectIO引脚。当PUDC为高时,不使能时则不使用内部上拉电阻。

4. 注意

1. 在设计电路图时,为选择最优的FPGA配置方案,需主要考虑以下4个方面:总体设置,下载速率,成本,配置灵活性。

2. 在主模式下,FPGA自动加载配置文件数据,该配置文件数据存储于板载ROM里;从模式下,通过外部MCU/处理器将配置文件数据加载到FPGA中。

3. 用作配置FPGA的专用管脚在配置完成后不能够被用作普通IO管脚,而非专用管脚在配置完毕后即被释放,可用作普通IO管脚。

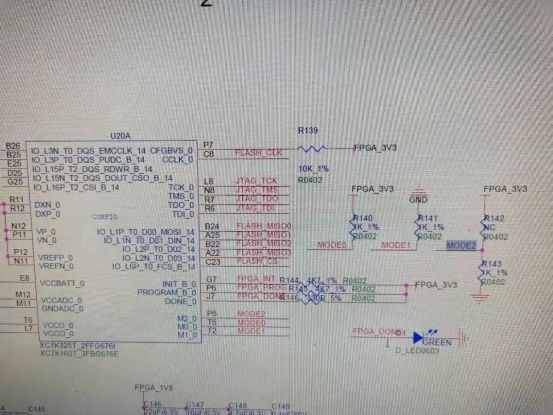

4. 电路设计时,一定要对M1M0管脚进行正确的电平设定。为了今后扩展需要或者暂时不确定为FPGA选择何种配置模式,可为M1M0管脚同时预留上拉和下拉电阻,便于灵活选择。

配置模式硬件选择,还是很经典的。

如下图,当采用JTAG的方式下载程序,M=[101],硬件上M[2]上拉

当采用SPI下载程序时候,M=[001],硬件上M[2]下拉

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

串口烧写FPGA程序2018-05-15 3463

-

51程序烧写软件2014-01-14 700

-

AVR单片机烧写程序progisp1722016-03-23 1952

-

STC板程序手动烧写(下装)软件2016-12-29 835

-

单片机程序烧写软件2017-01-07 1371

-

FPGA配置– 使用JTAG是如何烧写SPI/BPI Flash的?2017-02-08 10618

-

开发板烧写程序2017-10-14 8068

-

51单片机怎么用usb烧写程序2017-11-16 60617

-

51单片机烧写程序的方法2020-04-04 25421

-

stm32使用flymcu烧写程序2021-10-26 1717

-

PIC OTP 单片机程序烧写方法2021-11-16 1124

-

STM32:程序烧写方式2021-12-07 2553

-

ADE芯片程序烧写工具2022-09-26 902

-

使用 Uart 串口烧写程序到 RA 芯片2021-11-03 4235

全部0条评论

快来发表一下你的评论吧 !