浅谈条件语句的可综合性

电子说

描述

条件语句的可综合性

HDL语言的条件语句与算法语言的条件语句,最大的差异在于:

1.不管条件:当前输入条件没有对应的描述,则该条件为不管条件(Don’t Care)。对应不管条件的信号称为不管信号

2.不选条件:多个条件分支中,未获得当前输入条件指向的分析,称为不选条件(Don’t Select)。对应的信号称为不选信号。

不管不选发生时,HDL的综合器,将尽量维持原值,并且得到额外的生成结构。若无法用生成结构维持原值,则直接报错。根据行为语句的开节点ON/闭节点CN描述;部分条件PC/全部条件FC;以及条件分支的输出是否具有同名信号(线与WAND)或不同名信号(非线与Not_WAND),综合器将得到不同的处理结果。

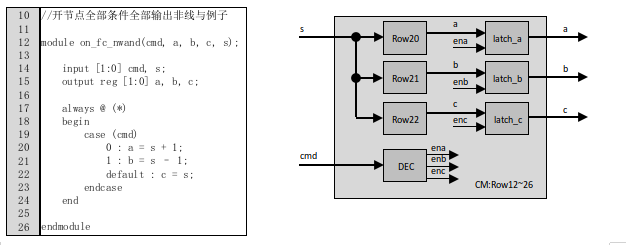

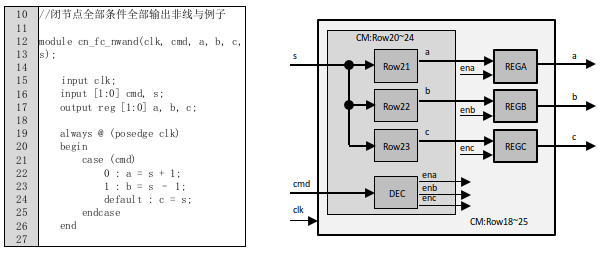

开节点全部条件全部分支非线与描述

此时,全条件描述导致没有不管条件和不管信号。但全部分支非线与(即每一个条件分支语句输出不同名信号),将导致不选信号。对于不选条件不选信号,EDA将维持原值。生成结构为锁存器。

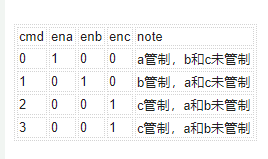

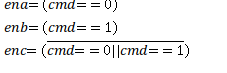

条件译码逻辑:

RTL视图:(QuartusII)

这里的译码逻辑为:

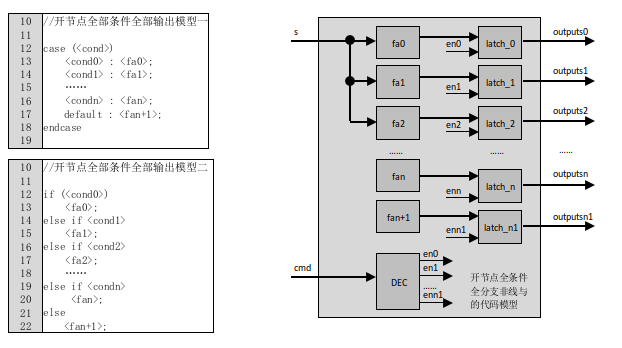

一般性的代码模型分析:

左侧为代码块,全条件描述不存在不管条件,全部分支非线与存在不选条件和不选信号,EDA需要为这些不选信号生成锁存器,用于维持原值。右侧为其代码模型:

结论:开节点全部条件全部输出非线与的HDL描述,将得到

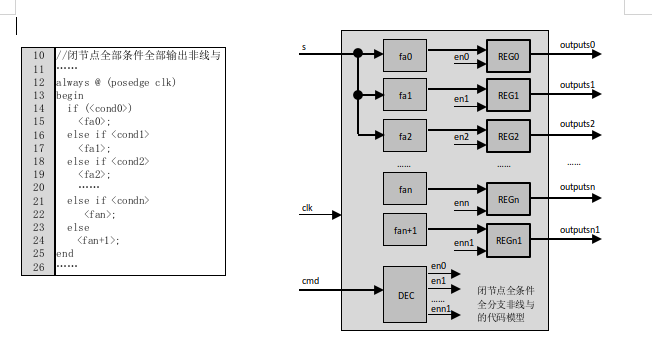

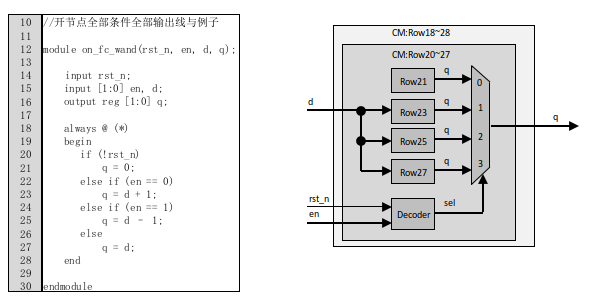

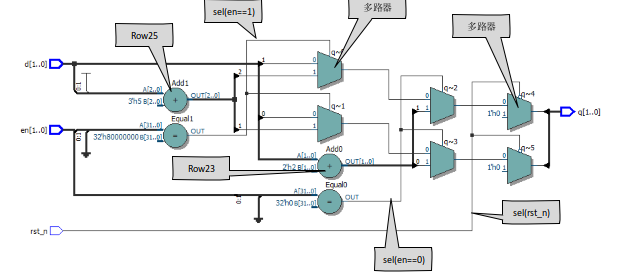

闭节点全部条件全部分支非线与描述

综合分析:

1.闭节点描述将导致生成寄存器

2.全部条件描述,使得此时不存在不管条件

3.全部分支输出非线与,将导致不选条件/不选信号。这些不选信号需要维持原值。

4.由于此时已经输出末端已经得到有记忆的寄存器,因此综合器此时将使用这些生成寄存器维持原值(不选信号)

例如:

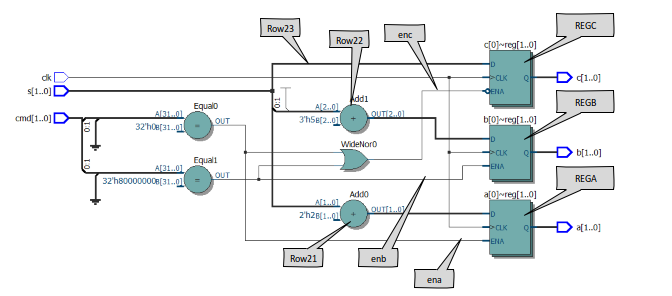

RTL视图(QuartusII):

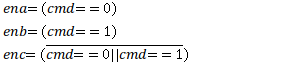

这里译码逻辑为:

关于使用寄存器维持原值(不选信号/不管信号):

寄存器维持原值需要遵循两个互相矛盾的综合原则:

1.优化原则:寄存器使用其使能端维持原值,将导致时钟信号的路由产生逻辑,或者说时钟信号被加工,最终导致时钟偏斜参数的恶化,影响系统的最高速度。因此,综合器将尽量避免寄存器使用使能端。

2.原创原则:综合器根据代码模型分析,和实际的物理实现,必然需要对已经的描述的代码进行加工和修改,最典型的例子就是生成结构(生成锁存器,生成寄存器)。但过多的生成结构,将导致最终实现的电路可能与设计者的愿望相悖。因此,综合器将尽量避免生成结构。

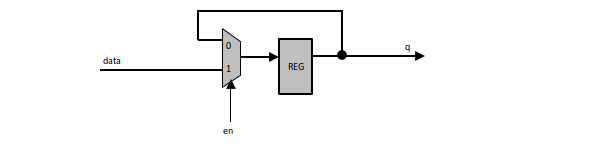

除了使用使能端维持寄存器原值,另一个产生生成结构的方法则是多路器闭环:

一般性的代码模型分析:

结论:闭节点全部条件全部分支输出非线与描述,将得到

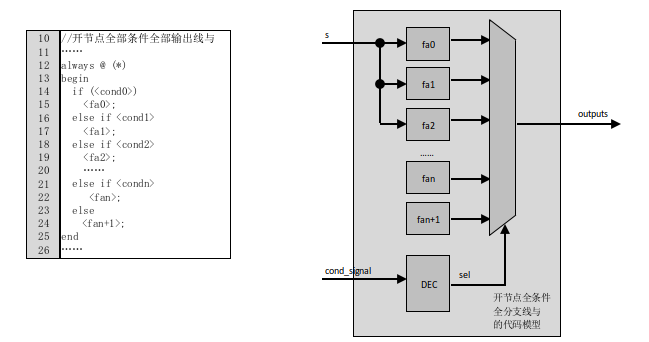

5.3开节点全部条件全部分支线与描述

综合分析:

1.全部条件避免了不管条件

2.全部分支线与(所以分支输出同名信号),综合器为了避免短路,将生产多路器。

注意此时没有生成锁存器。

RTL视图:

一般性代码模型分析:

结论:开节点全部条件全部输出线与描述,将得到<多路器输出>结构。

注意这里没有锁存器,虽然有不选信号,但这些不选信号被多路器屏蔽。

编辑:jq

-

Python条件和条件语句2023-09-12 1357

-

详解Verilog赋值语句、块语句、条件语句2023-07-02 9175

-

verilog语言的可综合性和仿真特性2023-06-28 3929

-

详解Python条件语句2023-04-19 1535

-

条件判断语句(if语句)2023-02-21 5056

-

综合性CPLD/FPGA软件Quartus 13.0下载2021-09-12 2218

-

简述HDL中循环语句的可综合性2021-05-12 3048

-

Verilog可综合的循环语句2019-10-13 20476

-

Verilog HDL的语句及可综合性的详细资料简介2019-08-01 1019

-

基于STM32的基础实验,进阶应用,硬件描述和综合性实验2018-09-04 1987

-

求51单片机综合性编程题2013-11-04 1834

-

verilog HDL 可综合模型的结构2012-10-20 2758

-

译码器及其综合性设计性实验2009-07-15 1002

-

VHDL中Loop动态条件的可综合转化2009-04-16 357

全部0条评论

快来发表一下你的评论吧 !