简述阻塞赋值和非阻塞赋值的可综合性

电子说

描述

阻塞赋值和非阻塞赋值的可综合性

Blocking Assignment阻塞赋值和NonBlocking Assignment非阻塞赋值,原本是软件进程管理的术语。由于Verilog团队是从C语言发展,所以基于的C的术语和概念出现在EDA中,原本是一个“误打误撞”,但历史造成的现实则是:必须理解和正确掌握它们的用法。

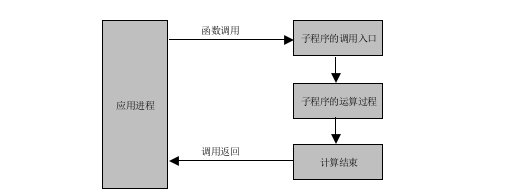

软件中阻塞进程,是指调用返回之前,应用进程一直等待:

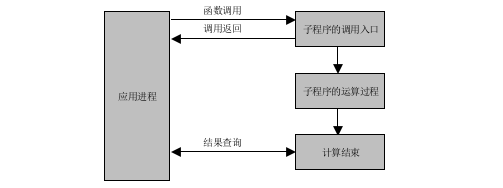

为了保证应用进程的效率,不至于被子程序的运算过程“挂起”。非阻塞进程得到应用:

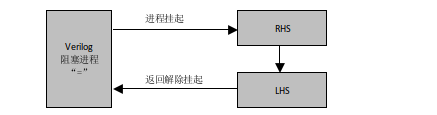

在非阻塞赋值进程中,无论子程序是否返回,不影响应用进程的正常运行。C语言的阻塞和非阻塞概念被Verilog团队引用,Verilog的阻塞赋值:

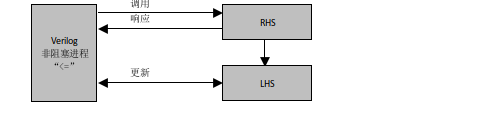

Verilog的非阻塞赋值:

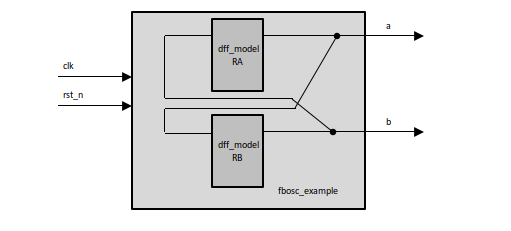

关于阻塞和非阻塞争议中,有一个辩论双方都引用的电路模型:反馈震荡器:

其中,复位信号rst_n初始化RA(a)为0, RB(b)为1。观察其物理连接,在时钟沿作用下,两个寄存器将互相交换数据。(同时交换)

为以上电路模型进行验证,在循环行为体并分别使用阻塞赋值和非阻塞赋值。并验证其前仿和后仿,观察对比真实性。

应该得到的结论:

使用阻塞赋值:前仿不真实(没有发生两个寄存器的交换),后仿真实(发生交换)

使用非阻塞赋值:前仿真实(交换),后仿真实(交换)

基于以上结论:

“倒阻派”认为,没有使用阻塞赋值的必要,必须在行为语句赋值中全部使用非阻塞。

“挺阻派”认为,基于电平敏感赋值用阻塞,沿敏感赋值用非阻塞,阻塞语句是必要的。

2000年以后,进入从“综合为王”进入“验证为王”的时代。同样的Verilog代码需要回到电脑中,用于非综合目的。验证代码中的赋值驱动与软件编写概念相同,带来非常大的便利。这就是“阻塞”赋值的反转。

编辑:jq

-

Verilog中阻塞赋值和非阻塞赋值的正确使用2018-07-03 3551

-

【技巧分享】FPGA至简设计-阻塞赋值与非阻塞赋值2020-04-24 1905

-

FPGA学习系列:5.阻塞赋值与非阻塞赋值2018-05-31 7594

-

阻塞赋值和非阻塞赋值的用法一篇文章就够了2020-01-30 22911

-

verilog中阻塞赋值和非阻塞赋值到底有什么区别2020-04-25 1262

-

IEEE Verilog阻塞赋值和非阻塞赋值的区别2020-06-17 12299

-

VerilogHDL语言:清阻塞赋值和非阻塞赋值2020-11-19 1676

-

Verilog语言中阻塞和非阻塞赋值的不同2021-08-17 7345

-

时序逻辑中的阻塞和非阻塞2022-03-15 3945

-

verilog中阻塞赋值和非阻塞赋值的区别2022-12-19 10055

-

Verilog中阻塞和非阻塞赋值金规2023-06-01 3109

-

一文了解阻塞赋值与非阻塞赋值2023-07-07 3268

-

阻塞赋值与非阻塞赋值2023-09-12 2029

-

verilog同步和异步的区别 verilog阻塞赋值和非阻塞赋值的区别2024-02-22 3151

-

在testbench中如何使用阻塞赋值和非阻塞赋值2025-04-15 1369

全部0条评论

快来发表一下你的评论吧 !