FPGA学习之安全行为和非安全行为

电子说

1.4w人已加入

描述

安全行为和非安全行为

由于条件语句的描述在很多情况下,导致生成锁存器。这些锁存器将上游的毛刺传输至下游,并且锁存器的使能信号(源自组合电路)也带有毛刺,引起的冒险竞争,导致下游逻辑出现错误的捕获,这种现象称为非安全行为。

一旦非安全行为发生错误,典型的特征是:前仿正确,后仿不正确,下板不正确,而且很难以找到问题所在。

因此,现代EDA,要求写安全行为的HDL,一旦出现非安全行为,大多数工具直接给出警告。又由于非安全行为的根源在锁存器,因此,“消灭锁存器”为EDA综合编译和时序收敛过程一个必然步骤。也就是说,一旦生锁,将给出警告。

安全行为的编码原则:

1.开节点输出的信号,必须满足:“全条件”+“全线与”

2.闭节点输出的信号,这些信号中的条件译码信号,必须写“全条件”+“全线与

安全行为编码例子:摩尔流水灯

设计需求

开发板的4个led灯,轮流点亮

每一个灯亮200ms,然后熄灭50ms

任何时候,按下start_n,流水灯开始运行

任何时候,按下stop_n,流水灯停止运行,全部熄灭

二段摩尔状态机

工作时钟clk频率为100KHz(10us)

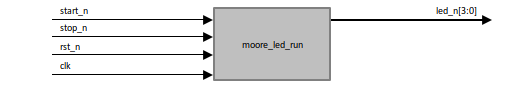

顶层框图

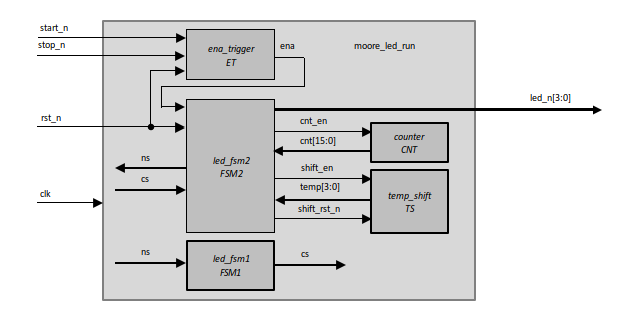

顶层架构

ET:使能信号触发器,在start_n为真时触发ena为真,在stop_n为真时触发ena为假。复位rst_n为真触发ena为假。

CNT:cnt_en为假,cnt清零;cnt_en为真,cnt加一计数

TS:shift_rst_n为真,给出temp的初始值4’b1110;shift_en为真,temp左移一次

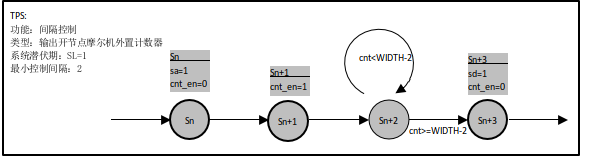

引用TPS:

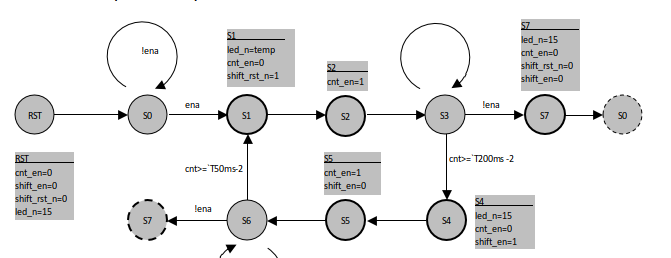

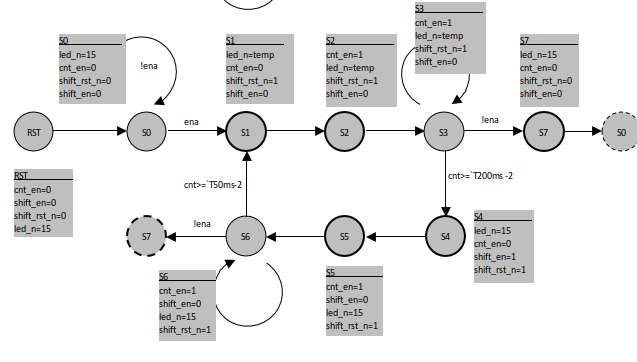

状态转移图(非安全行为)

状态转移图(安全行为)

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

【FPGA参赛作品】HDUSec-网络行为分析监控系统2012-06-01 3554

-

2021年安全员-C证-专职安全生产管理人员(广东省)报名考试相关资料分享2021-07-09 1268

-

车辆安全行驶状态判别模型及其应用研究2009-06-26 570

-

实现强大的车载智能安全行驶仪设计2015-10-06 1156

-

AI在安全行业具体的进展2017-12-26 5617

-

智能网联汽车应用于安全行驶技术2019-08-25 2765

-

现代安全管理发展方向和电网企业安全生产特点2020-06-24 3306

-

预计几年网络安全行业增长率较低,将如何反应2020-08-20 1057

-

探讨分析当前网络安全行业的问题,展望未来网络安全行业的发展趋势2020-10-10 6049

-

安装与调试24V安全行灯的线路2021-01-31 4745

-

2022年数据安全行业调研报告2023-03-30 649

-

英码智慧工地AI行为识别方案,提高工地的安全性和管理效率2023-05-09 1368

-

创新AI算法解密智慧矿山猴车安全之解法2023-10-30 1041

-

2021全球及中国FPGA安全行业研究报告.zip2023-01-13 497

-

芯盾时代连续十次入选安全牛《中国网络安全行业全景图》2024-04-15 1258

全部0条评论

快来发表一下你的评论吧 !