Vivado中电路结构的网表描述

描述

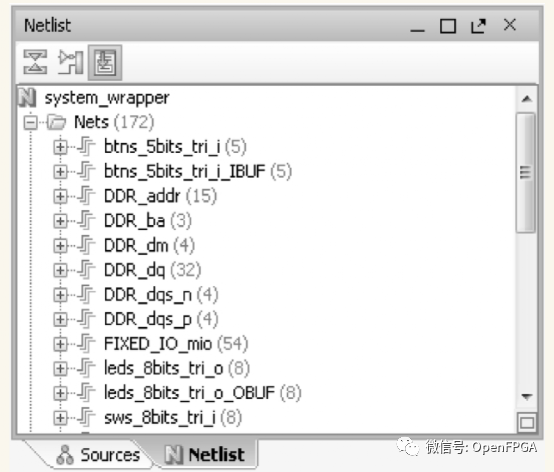

我们都知道FPGA的实现过程分为2步:分析综合与布局布线后就可以产生目标文件,这两个步骤中间有个非常重要的文件,那就是-网表。 下图是Vivado中网表列表示例:

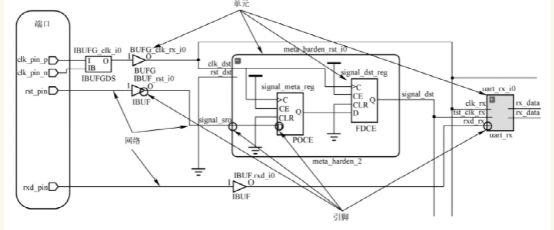

Vivado中网表列表示例 在vivado集成环境中,网表时对设计的描述,如网表由单元(cell)、引脚(pin)、端口(port)和网络(Net)构成。下图是一个电路的网表结构:

电路的网表结构

(1)单元是设计单元

1、设计模块(Verilog HDL)/实体(VHDL)。

2、元件库中的基本元素(Basic Elements ,BLEs)实例。如LUT、FF、DSP、RAM等。

3、硬件功能的类属表示。

4、黑盒。

(2)引脚是单元上的连接点

(3)端口是设计的顶层端口

(4)网络用于实现引脚之间,以及引脚到端口的连接。

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

在Vivado中实现ECO功能2023-05-05 4487

-

Vivado使用技巧-支持的Verilog语法2022-12-29 7896

-

VIVADO从此开始高亚军编著2020-10-21 6032

-

VHDL概述及在描述数字电路时的结构2020-07-21 3330

-

数字设计FPGA应用:硬件描述语言与VIVADO2019-12-05 3020

-

Vivado项目描述字段怎么添加2019-04-19 1107

-

运行Vivado 2017.1时出现没有结构来源无法打开结构网表请问是为什么2018-10-31 4072

-

在Vivado下利用Tcl脚本对综合后的网表进行编辑过程2017-11-18 8532

-

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?2016-09-07 15565

-

AD7606中文电路描述2016-05-05 1377

-

PSPICE中的电路元器件类型描述2007-11-16 8804

全部0条评论

快来发表一下你的评论吧 !