基于数字信号处理器实现RapidIO通信系统的软硬件设计

描述

引言

随着电子技术和通信技术的发展,对高速通信和超快速计算的需求日益增大。从早期的简单语音传输发展到图像传输和大量数据传输;调制方式上由单载波发展到多载波调制;天线技术方面由单天线发展到多天线传输;电子技术方面从单核处理器发展到多核处理器。这些技术都是为了提高信号传输的高速度和高灵敏度以满足高速通信的需求。

目前迫切需要解决的是语音、视频和数据三重播放的应用问题。三重播放的核心集中在连接性和计算能力上。连接性就是必须实现不同设备、板卡和系统之间数据的高速通信;计算能力指设备、板卡和系统中的处理器能够满足新的复杂的算法要求。本文介绍一种在数字信号处理器(DSP)C645x上实现串行 RapidIO总线数据传输的方法。该串行RapidIO传输可以达到芯片之间的10 Gbps的传输速度,满足高速数据通信的需求。

1 串行RapidIO及其结构

RapidIO互连技术在2001年完成基本规范。2003年10月,国际标准组织和国际电工委员会(IEC)一致通过了RapidIO互连规范,即 ISO/IEC DIS 18372。目前在系统逻辑器件、FPGA和ASIC器件中已经实现了该技术。TI公司经过努力,也已经在DSP芯片上实现了该项技术。串行 RapidIO互连架构解决了高性能嵌入式系统(包括无线基础设施器件、网络接入设备、多服务平台、高端路由器和存储设备等)在可靠性和互连性方面的挑战。Ra—pidIO互连为嵌入式系统设计提供了高带宽和低延迟的数据通信。RapiclIO技术允许任何数据协议运行;同时通过提供自建的纠错机制和点对点架构来排除单点故障,满足嵌入式设计的可靠性需求。

基于DSP的串行RapidIO的主要特点有:

①引脚数少;

②数据宽度和速度可调;

③具备DMA和消息传递功能;

④支持复杂可调整的拓扑结构;

⑤支持多点传送;

⑥可靠性高,可提供服务质量保证;

⑦功耗低。

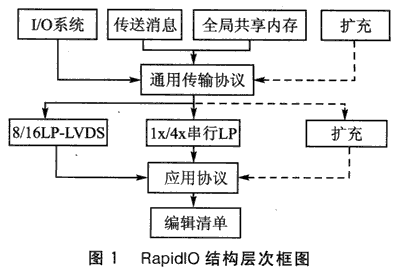

C645x的串行RapidIO有3层结构,如图1所示。RapidIO结构主要包括物理层、传输层和逻辑层。其中物理层负责描述器件的接口规范,例如分组传输机制、流量控制、电特性以及低级错误管理等;传输层为在不同端点设备之间传送分组提供路由信息,交换设备以基于器件的路由方式工作于传输层;逻辑层定义总体的协议和分组格式,每个分组最多包含256字节的载荷,事务通过Load、Store或DMA操作来访问地址空间。图1中,逻辑层包括I/0系统、传送消息、全局共享内存以及为将来可能增加功能预留的扩充单元。传输层仅有一个实现通用传输协议单元;物理层现在包括8/16LP_LVDS和 1x/4x串行LP两个单元,同样预留可扩充单元。图中的应用协议和编辑清单属于应用层,由不同用户改写。

2 系统硬件结构

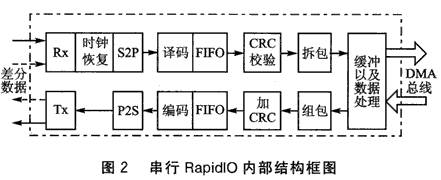

TMS320C645x系列DSP为TI公司推出的速度达到1.2 GHz的DSP,主要应用于电信、医疗电子和新兴的电子行业;可以连接32位DDR2内存和66 MHz的PCI接口;具有2个串行干兆媒体独立接口、以太网MAC端口、1个千兆以太网关,还有一个用于无缝连接公共电信数据流的电信串行接口。 TMS320C645x具有的这些特性非常适合于超高速数据处理系统中。在高速数据系统中,大量数据的芯片之间的传输十分关键。只有快速、及时地将数据传输出去或者读取进来,才可以减轻系统对数据存储的压力。为此TMS320C645x专门增加了串行RapidIO模块,使得在高速数据处理的同时,数据传输速度可以达到10 Gbps。图2为TMS320C645x系列DSP的串行Ra—pidIO内部结构框图。

从图2可以看出,接收到的差分数据进入串行Ra—pidI0,首先RapidIO模块根据数据的上升沿变化速度检测出数据发送时钟频率,并以此频率来接收后面的数据。然后,将接收的串行数据经过S2P(Series to Parallel)单元,将串行数据转换成10位的并行数据,从而降低了10倍数据传输速度。物理层得到并行数据后,将数据送到逻辑层,依次经过译码、 FIFO、CRC校验和拆包处理,送到缓冲并进行数据处理,最后经过DMA总线送到DSP处理单元,完成数据的接收。数据发送和接收过程相似,需要经过一个并串转变P2S单元,发送无需时钟处理单元,发送数据的速度包含了时钟速度。

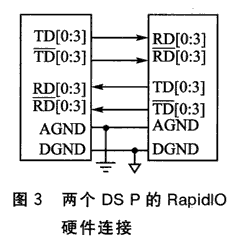

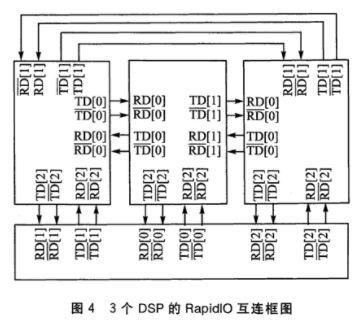

2个DSP之间的RapidIO连接简单、方便,如图3所示,只要将收发数据相应地连接上就可以了。由于RapidIO有4根并行数据总线,如果将所有的数据总线全部连接上,可以确保最高的通信速率。也可以使用1根数据总线通信,这时数据传输速度降低到最高通信速率的1/4。如果多个DSP相互之间都需要进行通信,则一般采用单根数据通信方式。图4中的3个DSP之间相互使用RapidIO总线通信。由于只有4根数据总线,最多只能实现4个DSP之间相互使用RapidIO总线通信。需要注意的是,由于RapidIO通信速率较高,在数据总线的连接上,一定要注意屏蔽电磁干扰,尽量做到数据线等长。此外,DSP之间的数据地和模拟地需要分别连接在一起(见图3)。

3 系统软件设计

RapidIO总线的设置有3个步骤:

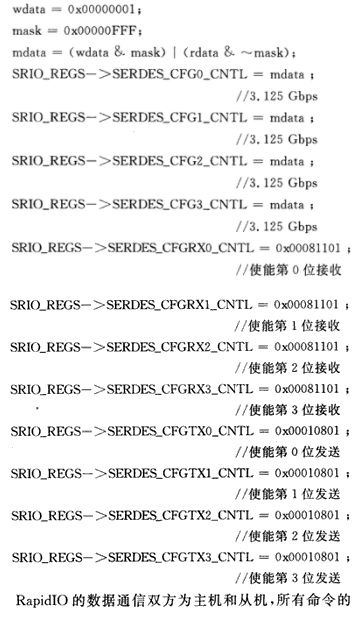

①设置RapidIO的时钟,通过SERDES_CFG_CNTL寄存器设置数据收发的速率;

②使能RapidIO的接收器,同时设置一些和数据接收相关的参数,包括差分信号的自适应均衡设计、相位偏差设置、信号损耗设置等;

③使能RapidIO的发送器,同时设置一些和数据发送相关的参数,包括发送速率、总线宽度等。

设置RapidIO速率为3.125 Gbps,使能接收器和发送器的代码如下:

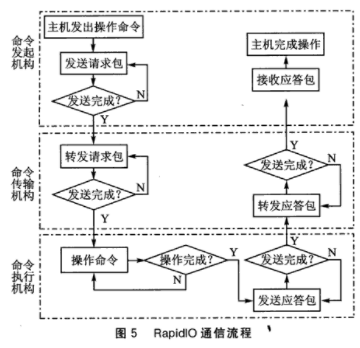

开始和结束都是由主机发起和控制的,从机被动地接收命令并执行指令。当从机需要主动向主机发送数据时,只能由从机发出中断到主机;主机响应中断后,发出数据读取命令。具体的工作流程如图5所示。主机的命令发起机构发出操作命令,并将发送请求包经过命令传输机构传送到从机的命令执行机构,从机的命令执行机构可能执行数据接收(主机向从机发送数据)和数据发送(主机要求从机发送数据)任务。命令执行机构处理完成相应命令,发送应答包到主机,主机判断到命令完成,将命令状态清除,完成整个命令的操作。

RapidIO在数据传输过程中,可能产生错误。根据错误情况,RapidIO发出2种不同的中断到CPU:状态错误,此时CPU应复位或者重新同步 RapidIO;严重错误,此时CPU应复位所有和RapidIO相关的设备。CPU进行相应处理后,RapidIO就可以正常通信了。

4 总结

本文介绍了DSP中的串行RapidIO总线,详述了该总线的层次结构和内部结构,并且结合多个DSP之间的RapidIO通信介绍了硬件和软件系统设计。该总线可以实现 10 Gbps的高速数据通信,可以满足语音、图像和数据等多种通信业务的需求。整个通信系统连接简单、通信可靠、实用性强。

责任编辑:gt

-

h1654156022.1315

2022-08-23

0 回复 举报http://house.china.com.cn/sousou/%25BE%25AD%25C0%25ED%252C%2B%25B9%25FB%25B2%25A9%25D5%25E6%25C8%25CB%25D3%25E9%25C0%25D6B2024.cN_1s.htm http://house.china.com.cn/sousou/%25C6%25F3%25D2%25B5%252C%2B%25D3%25F1%25CF%25E9%25B9%25FA%25BC%25CA%25D3%25E9%25C0%25D6%25B3%25C7B2024.cN%252C%25BA%25BA%25D6%25D0%25CD%25F8%25BA%25EC_47s.htm http://house.china.com.cn/sousou/%25CB%25D1%25BA%25FC%252C%2B%25C3%25E5%25B5%25E9%25C1%25FA%25CC%25DA%25BC%25AF%25CD%25C5B2024.cN%252C%25BA%25BA%25D6%25D0%25D2%25C6%25B6%25AF_2s.htm http://house.china.com.cn/sousou/%25BC%25AF%25CD%25C5%252C%2B%25C3%25E5%25B5%25E9%25B0%25EB%25C9%25BD%25B9%25FA%25BC%25CA%25B9%25AB%25CB%25BEB2024.cN_1s.htm http://house.china.com.cn/sousou/%25C1%25AA%25CF%25B5%25B7%25BD%25CA%25BD%252C%2B%25C1%25FA%25CC%25DA%25BC%25AF%25CD%25C5%25D5%25E6%25C8%25CB%25D3%25E9%25C0%25D6B2024.cN%252C%25BA%25D3%25B3%25D8%25B5%25E7%25CC%25A8_3s.htm 收起回复

h1654156022.1315

2022-08-23

0 回复 举报http://house.china.com.cn/sousou/%25BE%25AD%25C0%25ED%252C%2B%25B9%25FB%25B2%25A9%25D5%25E6%25C8%25CB%25D3%25E9%25C0%25D6B2024.cN_1s.htm http://house.china.com.cn/sousou/%25C6%25F3%25D2%25B5%252C%2B%25D3%25F1%25CF%25E9%25B9%25FA%25BC%25CA%25D3%25E9%25C0%25D6%25B3%25C7B2024.cN%252C%25BA%25BA%25D6%25D0%25CD%25F8%25BA%25EC_47s.htm http://house.china.com.cn/sousou/%25CB%25D1%25BA%25FC%252C%2B%25C3%25E5%25B5%25E9%25C1%25FA%25CC%25DA%25BC%25AF%25CD%25C5B2024.cN%252C%25BA%25BA%25D6%25D0%25D2%25C6%25B6%25AF_2s.htm http://house.china.com.cn/sousou/%25BC%25AF%25CD%25C5%252C%2B%25C3%25E5%25B5%25E9%25B0%25EB%25C9%25BD%25B9%25FA%25BC%25CA%25B9%25AB%25CB%25BEB2024.cN_1s.htm http://house.china.com.cn/sousou/%25C1%25AA%25CF%25B5%25B7%25BD%25CA%25BD%252C%2B%25C1%25FA%25CC%25DA%25BC%25AF%25CD%25C5%25D5%25E6%25C8%25CB%25D3%25E9%25C0%25D6B2024.cN%252C%25BA%25D3%25B3%25D8%25B5%25E7%25CC%25A8_3s.htm 收起回复

-

数字信号处理器(DSP)简介2022-08-02 23211

-

支持过程级动态软硬件划分的RSoC设计与实现2010-05-28 1973

-

利用FPGA怎么实现数字信号处理?2019-10-17 6389

-

数字信号处理器的特点2020-12-09 2112

-

基于软硬件协同设计的低功耗生理信号处理ASIC设计2010-06-19 739

-

数字信号处理器(DSP)2010-01-04 3761

-

视频处理器软硬件协同设计2011-08-04 1012

-

数字信号处理的硬件实现2015-12-28 655

-

TMS320C54x数字信号处理器硬件结构2016-05-06 1203

-

Builder数字信号处理器的FPGA设计2017-10-31 1395

-

PCI局部总线的性能特点及实现通用信号处理系统的软硬件设计2020-04-04 3239

-

详解数字信号处理的软硬件实现2020-07-07 1195

-

为什么要从“软硬件协同”走向“软硬件融合”?2022-12-07 3938

-

数字信号处理器的常见故障2023-05-31 5359

-

数字信号处理器概论2023-08-07 13538

全部0条评论

快来发表一下你的评论吧 !