基于MPC8245处理器和BCM56500芯片实现交换型路由器的设计

描述

作者:陈向荣;肖军;黄义雄;卢海军;郭炜

随着用户需求和网络技术的发展,高速率高端口密度的多层IP路由交换功能的应用已经越来越广泛了。由于实现三层以上路由功能的判据较为复杂,传统的路由器采用软件实现路由功能,由高性能的CPU同时实现控制平台和数据通道。

自从三层交换的概念提出以来,主要的技术可以分为两类:路由型交换机和交换型路由器。路由型交换机通过各种技术来发现、建立和缓存路由捷径来实现路由加速功能。一般情况下路由型交换机不实现大型动态路由协议,主要应用在基于ATM的多协议交换技术中。交换型路由器可以用来实现类似OSPF、EIGRP等的动态路由协议,采用RISC CPU加ASIC专用交换芯片分离控制平台和数据通道。由于数据通道单独由ASIC实现,可以达到端口线速。本文介绍了一个使用Freescale公司的MPC8245高性能RISC CPU和Broadcom公司的BCM56500高速交换芯片,来实现应用在网络接入系统中的24个千兆端口的三层交换的解决方案。由于本数据交换板是用于宽带接入系统,测试结果表明该设计方案的高性能、高端口密度和硬件实现的稳定性能够充分满足系统的需求。

MPC8245和BCM56500简介

MPC8245是基于MPC603e核的高性能低功耗的32位嵌入式RISC处理器,带有DUART接口、双通道DMA控制器和标准I2C控制器等通用模块。MPC8245支持PCI总线2.2标准,可以同时工作在PCI主设备和从设备状态。

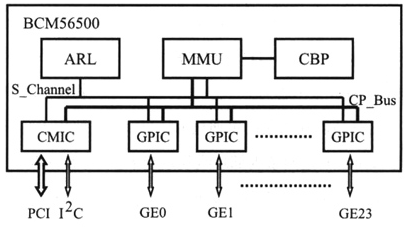

BCM56500是多层交换芯片,集成了24个千兆位以太网端口,同时支持IPv4和IPv6协议,支持硬件处理的二层交换,三层路由以及二到七层数据包的分类和过滤功能,芯片内部集成2MB数据包缓冲内存。BCM56500支持PCI总线2.2标准,系统设计中通常使用RISC CPU通过PCI总线对BCM56500进行初始化、配置管理和实现三层交换功能。BCM56500的结构框图如图1所示。

图1 BCM56500结构框图

由图1可以看出,BCM56500芯片由以下一些主要功能模块组成。

(1)千兆接口控制器(GPIC):用于提供千兆接口与交换逻辑之间的接口。

(2)CPU管理接口(CMIC):主要提供CPU与BCM56500设备不同功能块之间的接口,同时也用于诸如MIIM、I2C和指示灯的处理等功能。该模块通过PCI总线接口与CPU相连,可使CPU访问和控制BCM56500。

(3)地址解析逻辑(ARL):该逻辑功能模块可在数据包的基础上确定该数据包的转发策略。它利用二层表(L2_TABLE)、二层组播表(L2_MCTABLE)、三层表(L3_TABLE)、三层最长前缀匹配表(DEF_IP_HI和DEF_IP_LO)、三层接口表(L3_INTF)、IP组播表(L3_IPMC)、VLAN表(VLAN)以及生成树表(VLAN_STAG)来决定如何转发数据包。

(4)公共缓冲池(CBP):公共缓冲池实际上是2MB共享的包缓冲区,由8192个单元组成,每个单元256字节。设备里的每个数据包消耗一至多个单元。

(5)内存管理单元(MMU):BCM56500有一个单独的内存管理单元,每个内存管理单元与设备的功能块(GPIC)等相关联。内存管理单元负责数据包的缓冲和调度,它首先接收数据包,然后再将数据包缓冲,并在发送时加以调度,同时它还管理交换单元的流控特性,概括来说,就是缓冲逻辑、调度逻辑、流控逻辑。缓冲逻辑从CP-BUS接收包并存放在公共缓冲池,同样也从公共缓冲池获取包并将它们发送到CP-BUS。包的发送顺序由调度逻辑根据包的优先级别确定。流控逻辑包括Head-of-Line(HOL)阻塞预防和Backpressure两种方式。

这些功能模块之间可通过CP-Bus和S-Channel这两条内部总线联系起来。其中CP-Bus用于芯片内数据包的高速传输,它支持所有端口的同时线速转发。而S-Channel Bus则有两个作用,第一是用于内存管理单元到其他功能块的流控;第二是通过CPU管理接口由CPU控制访问内部寄存器和表,以及通过过滤器选送特殊数据包到CPU并由CPU发送特定数据包到端口以实现三层功能。

板级高端口密度LAN Switch硬件设计

图2 交换板硬件结构图

图2是LAN switch交换板的硬件结构,其硬件电路由CPU控制单元(子卡)、交换单元、物理层芯片单元、RJ45/光接口单元、CPU连接器单元、时钟单元、电源单元组成。

在设计中采用了一片BCM56500实现24个千兆数据端口,采用一片BCM5464物理层芯片和一片BCM5461 物理层芯片来提供不同类型的数据端口。使用BCM5464接出4个千兆电接口(SGMII接口)接入前面板,使用BCM5461接出1路千兆电接口(SGMII接口)作为板内使用。使用BCM56500的SERDES接口接出2路千兆光接口接入前面板,另外使用1路SERDES接口也作为板内使用,其余16路千兆端口使用SERDES接口接入系统背板,供系统其他板卡上联作为星型数据总线。BCM5464是BroadCom公司的4端口千兆物理层芯片,BCM5461是BroadCom公司的单端口千兆物理层芯片。

在硬件设计中,交换单元选用了BCM56500,通过PCI接口与CPU控制单元相连,以实现对交换芯片的配置管理和快速通信。设计中的实际连接如图3所示。其中由于系统中只有1个PCI从设备,设备号采用PCI_AD[31]线上的信号来选中,因此实际连线中CPU的IDSEL直接连接PCI_AD[31]即可。在PCI驱动软件中,要保证使用硬件相应的设备号进行选中和配置。

图3 系统PCI连接图

LAN Switch的软件启动和硬件初始化过程

LAN Switch采用WindRiver公司VxWorks操作系统。在CPU最小系统(CPU+SDRAM+Flash+串口)完成启动后,需要通过PCI总线对LAN Switch交换部分进行初始化,主要步骤如下。

(1)由于BCM56500工作在little endian模式,而MPC8245工作在big endian模式,因此需要对头模式进行设置(可以使用字节位移指令或者对CONFIG_ADDR和CONFIG_DATA在访问前进行字节交换);

(2)根据硬件连接选择PCI设备的设备号,配置交换芯片BCM56500的PCI基地址和窗口大小;

(3)通过PCI总线使用交换芯片BCM56500的CPU管理接口确定交换芯片的型号,然后根据不同的芯片类型进行初始化和DMA通道的配置;

(4)挂接交换芯片的驱动程序和各种API,完成LAN switch的初始化过程。

其中第三、第四步骤需要Broadcom公司的软件开发支持包(SDK)支持,直接从程序中调用Boradcom的初始化程序,可以保证正常完成初始化和加载驱动程序。

以下对PCI驱动的设计配置和SDK做进一步的说明。

前面已经说明了对于BCM56500的IDSEL信号已经确定,设计中使用VxWorks的标准PCI驱动程序,对于BCM56500的PCI挂接例程如下。

(1)在bootROM中用sysHwInit()调用sysPciAutoConfig(),对PCI_SYSTEM结构进行实例化;

(2)同样在sysHwInit()中,使用pciConfigOutLong()对BCM56500的基地址和窗口大小进行配置,然后使用pciConfigOutByte()挂接BCM56500的中断至CPU的外部中断向量表;

(3)至此,PCI配置完成。通过BCM56500的S_Channel可以配置BCM56500中的各个寄存器和表项。S_Channel的消息传递有特殊的格式和规范,一般通过Broadcom公司提供的软件开发支持包(SDK)中自带的标准函数来进行配置。

本设计使用Broadcom公司5.2.3版的SDK。SDK的设计严格分层,自下而上分成操作系统(RTOS)、操作系统适配层(SAL)、芯片系统层(SOC)、分发层(Dispatch)和BCM的应用接口层(API层)。由于SDK支持Broadcom公司的几乎所有交换芯片,因此在使用SDK的时候,在使用API之前需要进行芯片查询,按照搜索到的芯片挂接相对应的API。整个的芯片查询和挂接API的过程,使用SDK实现相当方便。初始化SDK的API的过程如下。

(1)SDK软件初始化:diag_shell(),sysconf_int();

(2)在本地的PCI总线上查询Broadcom设备:sysconf_prob();

(3)根据查询到的设备进行相对应的驱动程序挂接:sysconf_attached();

(4)应用正确的驱动程序对交换芯片进行初始化:system_init();

(5)芯片基本的初始化后,进入正常的工作状态,此时可以进行应用程序的初始化了:bcm_init(),应用程序和协议栈入口。

交换性能测试结果和三层功能实现

设计定型后的LAN Switch经过SmartBits测试,每个端口都可以达到线速转发,稳定性测试表明可以达到48小时千兆线速无丢帧性能。所得的结果如图4所示。

图4 千兆光接口48小时性能测试结果

由于这个设计方案使用CPU+ASIC方案,三层的IP路由转发功能由交换芯片的三层转发表(L3_Table)实现线速转发。其他的三层协议栈功能应用交换芯片中过滤器实现。在本设计中,根据需求完成了OSPF、RIP-2、DHCP、DHCP relay、IGMP、IGMP relay等常用IP协议栈,实现了基于PCI总线的板级高端口密度三层交换机的设计要求。

责任编辑:gt

-

路由器处理器有什么用2023-08-27 2965

-

BCM4707/4708/4709处理器英文手册2023-07-24 1135

-

路由器和交换机的区别2022-03-17 7743

-

RK3399处理器与AR9201处理器有哪些不同之处呢2022-02-21 3536

-

freescale的mpc563处理器开发流程2021-08-18 1343

-

mt7628处理器2021-07-30 3172

-

MT7628处理器是什么2021-07-22 2320

-

麒麟9000处理器和高通骁龙875处理器相比如何?2020-11-03 7136

-

苹果a6处理器怎么样_a6处理器参数2012-09-13 26709

-

信元交换路由器(CSR),信元交换路由器(CSR)是什么意思2010-04-03 1956

-

基于MPC8260处理器和FPGA的DMA接口设计2010-02-08 1597

-

路由器处理器2010-01-06 715

-

交换机和路由器2009-01-08 4544

-

MPC8245/XPC8245LZU266B pdf dat2008-08-29 1103

全部0条评论

快来发表一下你的评论吧 !