如何将两个PSI2C控制器通过EMIO接口互连起来?

电子说

描述

I2C 总线的两根信号线 SCL 和 SDA 需要上拉才能正常工作,当板卡上没有合适的硬件设置或者没有合适的 I2Cslave 设备,我们就无法进行 I2C 软件测试。那么是否可以将两个 PSI2C 控制器通过 EMIO 接口互连起来呢?

因为在 PL 内部无法设置信号线上拉,所以不能直接将 I2Cmaster 控制器的 scl_o/sda_o 连接到 I2C slave 控制器的 scl_i/sda_i。有另一种方法来实现上拉的效果,就是通过在顶层 wrapper 里 scl_T 和 sda_T 的组合逻辑来模拟 scl_i 和 sda_i,具体逻辑如下,

assign i2c0_scl_i = i2c1_scl_t && i2c0_scl_t;

assign i2c0_sda_i = i2c1_sda_t && i2c0_sda_t;

assign i2c1_scl_i = i2c0_scl_t && i2c1_scl_t;

assign i2c1_sda_i = i2c0_sda_t && i2c1_sda_t;

这些信号都是两个 PS I2C 控制器的 emio 信号从 block design 导出到顶层 wrapper,其中四个 emio 信号在从 block design 导出到顶层 wrapper 之前需要做逻辑反相。

i2c0_scl_t、i2c0_sda_tn、i2c1_scl_t、i2c1_sda_tn

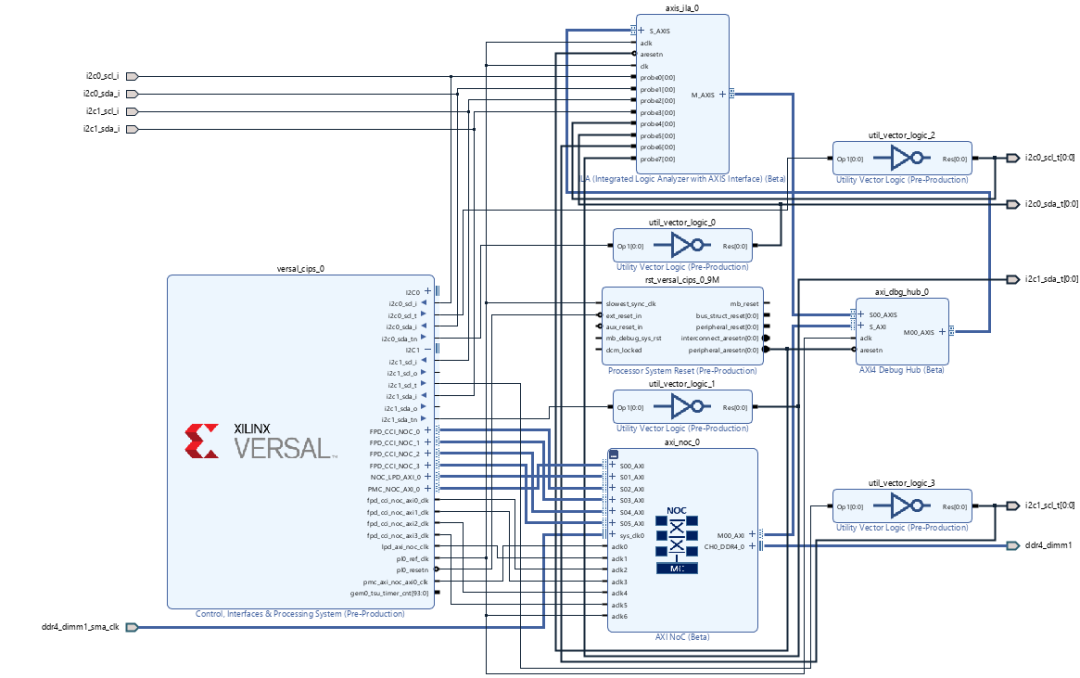

反相操作如图中 util_vector_logic_0~3所示,

附件是个例子工程 (附件可点击阅读原文 输入0513获取),基于 vck190 es1 board 和 Vivado2020.2。里面包含 block design tcl脚本、顶层 wrapper、prebuilt xsa 文件和 vitis application 源码。Vitis application 把i2c0 配置为 master、i2c1 为 slave,然后做读写校验测试。可以通过串口输出信息来判断是否测试成功,block design 里也介入了 ila,可以在 hardware manager 里检查相关信号。下面是 i2c0_scl_i/i2c0_sda_i/i2c1_scl_i/i2c1_sda_i 波形 :

原文标题:开发者分享 | 如何在 Versal 平台实现两个 PS I2C 控制器的回环

文章出处:【微信公众号:XILINX技术社区】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

有没有办法使用两个ADS8556,12个通道连起来使用?2025-01-02 253

-

两单片间的通信那个串口怎么连起来啊?2013-02-04 3269

-

FPGA边界扫描模式可以串接两个FPGA吗2014-03-24 2617

-

基于labview的振动信号测试系统设计,两个仿真都差不多了,就差连起来了,可实在有些问题2017-05-10 1885

-

为什么这两个不能连起来啊?2017-05-12 3939

-

这块敷铜为什么会出错?敷过铜的焊盘之间也要用线连起来吗?2018-01-30 5404

-

请问有直接可以和C6455DSK的EMIF接口连起来的高速ADC采集板吗?2018-07-25 2157

-

请问F28335的两个GPIO口能直接用导线连起来吗?2018-09-04 1370

-

GSM跟板子直接串口连起来不能通2019-01-23 1601

-

c文件怎样与emWin工程连起来使用?2020-08-13 898

-

如何将MCP2515CAN总线控制器与Arduino接口2019-07-30 22665

-

两个PS I2C控制器的回环测试2022-04-13 3169

-

如何在Versal平台实现两个PS I2C控制器的回环2022-08-02 1029

-

如何将两个16*2 LCD与arduino连接在一起2023-06-30 510

-

PCB中的GND一定要都连起来吗?PCB的GND需要怎么弄?2023-09-22 15677

全部0条评论

快来发表一下你的评论吧 !