基于EP2C35 FPGA和扩频编码技术实现井下通信系统的应用方案

描述

扩频技术是一种信息传输处理技术。通过扩频使信号功率相当均匀的分布在很宽的频率范围内,具有类似于白噪声的统计特性,使得该系统有很强的抗干扰性能、高保密性、低截获概率性及良好的码分多址通信性能。扩频系统的这些优良性能,使得它在很多对信道带宽利用率要求不高的场合得到广泛的应用,本文就是一个关于深井通信的实现系统。

设计背景

根据扩频码控制的调制参数不同,扩频方式可分为:直接序列扩频(DS-SS),跳频扩频(FH-SS)和跳时扩频(TH-SS)。本文介绍的系统采用的就是直接扩频,直接序列扩频通信是通过在发送端将数据信号和更高数据速率的位序列或填充码组合而实现的。填充码是冗余位组合,其可根据扩展率将用户数据分段。当该位信号发送时,可以增加信号抗干扰的能力。如果在这种组合中有一个或多个位在传输过程中发生错误,那么由于发送的冗余性,原始数据也可以被恢复出来。图1为直扩系统的组成原理框图。由信源输出的信号a(t)是码元持续时间为Ta的信息流,伪随机码产生器产生的伪随机码为c(t),每一伪随机码宽度或者切普(Chip)宽度为Tc。将信码a(t)与伪随机码c(t) 进行模二加,产生一速率与伪随机码速率相同的扩频序列,然后再用扩频序列去调制载波,这样就得到已扩频调制的射频信号。

在接收端,接收到的扩频信号经高放和混频后,用于发端同步的伪随机序列对中频的扩频调制信号进行相关解扩,将信号的频带恢复为信息序列a(t)的频带,为中频调制信号。然后再进行解调,恢复出所传输的信息a(t),从而完成信息的传输。对于干扰信号和噪声而言,由于与伪随机序列不相关,在相关解扩器的作用下,相当于进行了一次扩频。干扰信号和噪声频谱被扩展后,其谱密度减低,这样就大大降低了进入信号通频带内的干扰功率,使解调器的输入信噪比和输出信噪比提高,从而提高了系统的抗干扰能力。

本文介绍的是一个井下通信系统。煤矿井下巷道和采掘工作面空间狭窄,大都呈隧道状,采煤工作面长可达几百米,而矿井巷道长可达数千米甚至十几千米,宽、高仅为几米。作业点分散,人员流动性大,环境中存在着大量的有爆炸危险的一氧化碳,瓦斯及煤尘等空气混合体,事故隐患极大。因此,建立完善的煤矿井下无线和移动通信系统对于提高矿井现代化生产、安全和管理水平有着非常重要的意义。

目前我国煤矿井下移动通信的主要方式有动力线载波通信、感应通信、漏泄通信以及中低频无线电。动力线载波通信在传输距离,通话清晰度和抗干扰能力上都无法适应现代化矿井的需要。感应通信目前在我国部分煤矿得到使用,但通话质量和通信距离都不够理想。漏泄通信不能覆盖到井下的每个地方。

为了减少地质条件对无线通信信号的衰减,通常采用低频通信直至超低频通信。中低频通信穿透能力强,如用超低频信号可穿透岩层几百米,可在大面积范围内对深处的坑道实施指挥与控制,加上它对电离层扰动不敏感,即使发生大爆炸也不会严重干扰它,这使它在极端恶劣环境条件下成为提供大面积应急指挥控制通信的一种重要手段,在紧急情况发生时,能够迅速有效地与井下的工作人员进行通讯。所以本系统就是采用这种通信方式,中频信号仅22Hz。

系统原理框图

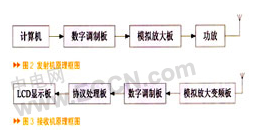

图2和图3分别为发射机原理框图和接收机原理框图,信号首先从计算机发出,通过数字调制板扩频编码后转换为模拟信号,模拟信号放大后送到天线发射出去。接收机是发射机的逆过程,模拟信号从天线接收下来后先进行放大,然后送入数字解调板转换为数字信号后解扩,解扩后的信号送入协议处理板,协议处理板用于实现选呼,群呼及广播协议的实现,图中LCD显示板用于信息的显示。数字调制板和数字解调板是整个系统的核心,分别进行扩频调制和解调,解调是调制的逆过程,二者结构相似,硬件电路也大同小异,只是输入和输出互换,所以本文主要介绍数字调制板。

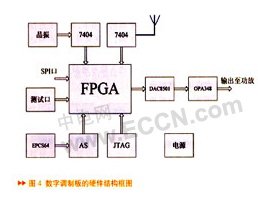

数字调制板的硬件结构框图 数字调制板的硬件结构框图如图4所示。

数字调制板从计算机接收数据并接收来自天线的状态信息,主要完成对信号的扩频编码调制,调制后的信号经数模转换和放大滤波后送入下一级功放电路。计算机和调制器间采用SPI口进行数据传输,扩频编码调制采用turbo码,来自天线的状态信息用于指示天线的短路或断路等通信状态。 该模块的核心部分是FPGA,对数据的处理都是在此芯片内完成。数据从计算机的SPI口输入,处理后经DAC8501变为模拟信号,再经OPA348放大后输出。FPGA配置了JTAG下载口,用于调试程序时使用。AS下载口是在程序调试完成后,通过该口将程序写入FPGA的专用配置芯片EPCS64中,EPCS64中的内容掉电后不会丢失,以后上电后程序就会自动下载进FPGA中。晶振提供系统时钟,为了增强驱动能力,所以加了片7404。

主要模块的电路设计

系统的核心芯片FPGA依据编写程序所需资源适当选取,本系统选用EP2C35,EP2C35是ALTERA公司cyclone‖系列FPGA。CycloneII FPGA采用TSMC 90nm Low-K工艺,1.2V内核电压,比cyclone系列成本降低30%,逻辑容量多三倍,成本大约是相竞争的低成本FPGA的一半,而速度快50%以上。EP2C35的逻辑单元为33216个,M4K RAM块105个,RAM480K,嵌入式18×18乘法器35个,锁相环4个,可以满足设计需要。

SPI是串行外围设备接口,是一种高速的、全双工、同步串行外设接口。它可以使MCU与各种外围设备以串行方式进行通信以交换信息。该接口一般使用4条线:串行时钟线SCK,主机输入/从机输出数据线MISO,主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS。由于SPI系统总线接口简单,可以节省很多常规电路中的接口器件和I/O口线,提高设计的可靠性。所以当传输速度要求不是太高时,使用SPI总线可以简化电路设计,提高系统的性能。图5 给出了SPI接口电路原理图。

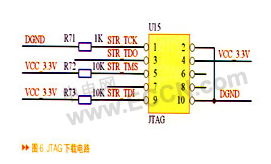

JTAG是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件如DSP、FPGA器件等都支持JTAG协议。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。JTAG编程方式是在线编程,方便调试,从而大大加快工程进度。JTAG下载电路如图6所示。

AS是主动串行编程模式,在AS模式下,POF数据流直接下载到基于Flash的串行设备中。因为FPGA是基于SRAM架构的,掉电以后,所有存储在SRAM中的配置数据都会丢失,所以每次上电必须重新加载,很不方便。EPCS64本质上是一块专用flash,用于保存FPGA的配置信息,它在掉电后,里面内容不会丢失,在FPGA上电的时候,自动从配置芯片 里面读出配置内容,这样上电后即可使用。所以当设计完成后通常将程序通过AS口固化到片外配置芯片,以后每次上电后程序就会自动下载进FPGA中,图7给出了连接电路。

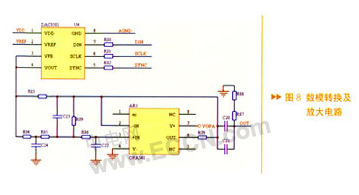

数模转换器和运算放大器分别选 用TI公司的DAC8501和OPA348。DAC8501是16比特串行输入数模转换器,带宽350KHZ,工作电压2.7V~5.5V,只有8 个管脚,体积很小,非常适合本次 设计要求。OPA348是一种具有极低功耗的放大器,供电电流只有45 A,带宽1MHZ,工作电压2.1V~5.5V,SOT23-8封装,外围电路简单,调试方便。电路原理图如图8所示。

总结

本文介绍了一个采用扩频编码技术的井下通信系统,并对其调制器部分的硬件电路做了简单介绍。其实这可以看作是一个简单的通信系统模型,发送端进行编码调制,接收端进行译码,利用编码来扩展待传输的信号带宽,以换取信噪比上的好处,从而可以在较低的信噪比下正确地传送信息。该系统模型完全可以移植到其它设计上去,基本结构不变,只是数模转换器和模数转换器及放大器要依据新系统的带宽等要求来选择,FPGA也应依据新系统所需资源来选择合适的型号,编码也可以选用BCH码或LDPC码等其它码,还可以视系统需要而加入RS232接口或USB接口等其它接口电路。

责任编辑:gt

-

基于EP2c35 FPGA和NiosII 软核实现视频监控系统的设计2020-12-30 1475

-

基于FPGA的扩频系统设计2022-10-31 2781

-

扩频通信技术教程2009-05-22 11401

-

基于FPGA实现CDMA扩频通信中的同步系统毕业设计2015-10-16 4132

-

基于FPGA的扩频系统设计(附代码)2023-08-23 1976

-

基FPGA Cyclone II_EP2C5 EP2C8的频2008-11-30 1056

-

FPGA在多进制正交扩频通信系统中的应用2009-06-20 1400

-

基于FPGA的CMI编码系统设计2011-01-15 1109

-

基于FPGA的高炉TRT顶压控制系统的研究2012-10-16 790

-

基于EP2C35的DSP阵列板通信接口设计与实现2017-10-19 1018

-

EP2C35A用户手册V1(一版)2017-10-28 1632

-

直接扩频通信同步系统的xilinx FPGA设计原理分析2017-11-24 1799

-

基于FPGA解决方案的SOPC技术实现二维条码识别系统的设计2020-07-21 2871

-

基于FPGA实现扩频通信模块的设计方案与仿真2021-07-05 4088

-

基于FPGA的直接序列扩频和差错控制码编码系统的实现2023-11-06 528

全部0条评论

快来发表一下你的评论吧 !