基于FPGA和双GA3816处理器实现数字通用信号处理系统的设计

描述

引言

当前信号处理的发展趋势是可重构、可扩展的通用信号处理系统。即通过灵活的软件编程来适应处理问题的变化和算法的发展,通过简单的硬件扩展来适应规模处理的变化,以提高信号处理系统的可编程能力和升级能力。而采用具备强大处理能力的ADSP-TS201S芯片可以对大量的数据作实时处理。TS201S可在600 MHz的内核时钟下完成每秒48亿次乘累加(MAC)运算和每秒36亿次浮点运算(FLOP),具有比同类处理器高出50%~100%的处理能力。它内部集成了24 MB的存储器,其片内大存储量与高达33.6 Gb/s的内部带宽是提高性能的关键。TS201S的外部64位数据总线和32位地址总线时钟最高可达125 MHz。

本文通过GA3816、FPGA和DSP构建了一个高速、通用、可扩展的多功能信号处理平台,该信号处理平台经过动态配置GA3816处理芯片可实现一些信号处理领域常用的运算,也可以通过对DSP、FPGA芯片的编程来实现一些其它算法,所以该平台能够广泛的应用于信号处理等领域。

1 系统设计

1.1 系统硬件结构

本通用信号处理平台主要由双TS201、双stratix系列FPGA和双GA3816处理器构成,同时使用了一些RAM、FLASH和SDRAM器件来存储系统中的数据和程序。系统与外部进行通信的接口主要采用CPCI总线接口。本设计采用DSP结合FPGA的方式。这种方式最大的优点就是结构灵活,有较强的通用性,适合模块化设计,并能够提高效率,同时,其开发周期较短,系统容易维护和扩展,所以,这种结构目前比较流行。图1是该系统的结构框图。

1.2 系统功能

此信号处理板的体系结构可以概括为三个处理阵列、两条板级接口总线和一条板内总线。三个处理阵列指的是GA3816处理阵列、DSP处理阵列和FPGA处理阵列。两条板级接口总线是指CP-CI总线和用户自定义总线。一条板内总线是指DSP总线。

用户自定义总线可由两个DSP处理器的两个链路口和一组由FPGA引出的备份信号线构成,包括时钟线、控制线和数据线。该总线可以针对不同应用环境,由用户自己根据需要加以定义。DSP和FPGA通过自定义总线与外部系统进行通信,而DSP通过链路口可以与外部系统实现程序加载以及数据互传,FPGA则通过备份信号线实现与外部系统的数据传输。

DSP总线主要是为DSP处理阵列提供一条内部互联和与FPGA处理阵列互联的通道。通过这条总线,DSP1和DSP2可以相互共享存储空间,并且二者可通过此总线共享板上的FLASH存储器和SDRAM,并分别将二者作为自己的程序存储器和内存扩展。系统复位后,DSP通过FLASH进行程序加载。

目前,PCI总线接口的设计有两种方法,一种是利用专用的PCI接口芯片来设计。另一种是利用FPGA可编程器件进行设计。由于用FPGA比较复杂,开发难度较大。为此,本系统将PCI控制器软核嵌入到FPGA中,从而控制本板对外的CPCI总线。本板则通过CPCI总线或自定义总线接收待处理的数据,并在FPGA巾对将待处理数据分配给GA3816处理通道和DSP处理通道。当这两个处理通道的处理结果反送到FPGA后,义在FP-GA中进行数据交换或者通过CPCI总线作为本板级处理器的输出。此外,两片FPGA中也有大量的硬件资源,可以针对不同应用场合,通过固件编程使其成为专用处理器,或组成FPGA处理阵列。而两个FPGA器件之间的64位双向信号线则可以使两个FPGA器件之间的数据传输更为方便和快捷。

系统中的两个RAM器件可分别直接和两个FPGA器件进行通信,并可通过FPGA分别作为两个GA3816处理阵列的片外存储器,也可作为板上的程序或者数据缓存。因为对于一般的运算来说,GA3816的处理速度要高于TS201的处理速度(对于1024点的复数FFT运算来说,GA3816的速度为12.8μs,而主频为300 MHz的TS201则为32.78μs),所以在系统所需实现的功能中,如果GA3816芯片可以实现就直接用它来实现(如FFT、FIR等),GA3816不能实现的功能则可根据需要在TS201和FPGA中编程实现。在FPGA中对GA3816芯片进行配置可以实现GA3816的不同处理功能以及运算模式,从而满足不同应用场合中GA3816芯片的不同数据处理功能。

1.3 时钟模块

ADSP TS201S的系统输入时钟SCLK同时也是TS201S的外部接口时钟,为与外部器件兼容,SCLK不应取得太高。一般可取内核时fCCLK为fSCLK与SCLKRAT的积,P-BUS的工作时钟fSOCCLK为fCCLK/2,链路口时钟fLxCLK为fCCLK/CR(CR为LCTLxREGlSTER的设置值),若SPD位设置为100,则取fLxCLK=fCCLK/4。这样,将时钟信号再经过时钟驱动后分别送入两个FPGA,再由FPGA的锁相环进行倍频或者分频就可得到DSP、SDRAM、GA3816和RAM所需要的时钟信号。

GA3816和RAM的时钟信号可由FPGA直接提供,DSP和SDRAM的时钟信号则由FPGA提供的时钟通过一个时钟驱动器来供给。设计时应尽可能的使时钟线等长的到达器件,这样可以减少时钟偏移,从而使DSP和SDRAM之间能够更好的通信。因为时钟信号是非常敏感的信号,所以要尽量的减少反射和串扰。在时钟信号线上串接适当的匹配电阻可以有效的减少反射,而减少串扰则需要在时钟走线周围留出额外的空间,或者把时钟线单独放在两个地平面层中间的一层,这样可以使时钟的信号完整性得到有效的改善。

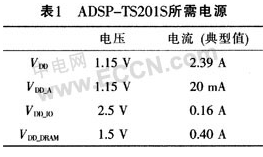

1.4 电源模块

stratix和GA3816的核电源电压分别为1.5 V和1.8 V,3.3 V为I/O电源,ADSP-TS201S的三种电源如表1所列。本设计中所需的四种电压都是从外部输入的5 V电源转换而成的,转换芯片选用TI公司的TPS54350器件。

由于电源层无法单独消除线路噪音,所以通常需要借助旁路电容来进行滤波。一般情况下,将1~10μF电容放置在电路板的电源输入端可滤除板外产生的低频信号;而将0.01~0.1μF电容放置在电路板的每个有源器件的电源引脚和接地引脚上,则可滤除电路板上有源器件产生的高频率的噪声谐波。但是,任何一种电容的滤波频率范围都是有限的,所以通常采用大小电容并联的方式来扩展其有效的滤波频率范围。

1.5 复位模块

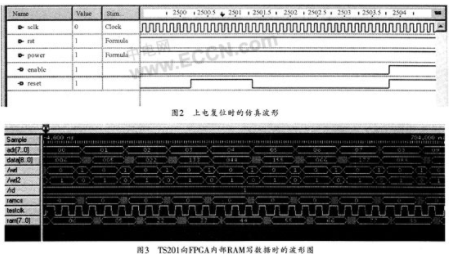

ADSP TS201S的复位信号较ADSP TS101S更简单,它可以采用较简单的上电复位方式,即要求电源正常后保持RST_IN为低2 ms以上,并在RST_IN有效之前使SCLK运行2 ms。上电复位相对于正常复位来说要复杂一些。在FPGA中实现TS201的复位和时序控制,可使TS201正常工作。图2为TS201上电复位稳定后的仿真波形。图中,sclk为8 MHz时钟(由TS201的SCLK时钟分频得到),rst为正常复位信号,power为上电复位信号,enable为复位后系统稳定的输出信号,reset为TS200的复位输出信号。

2 调试结果

图3为调试过程中通过逻辑分析仪采集到的TS201向FPGA内部双口RAM写数据时的波形图,采用双口RAM是由于雷达信号总是以帧的方式进行处理,在处理第一帧的数据时,输出前一帧的数据,这样的数据访问方式可避免发生冲突。为了能够正确的读写双口RAM,这里的DSP访问双口RAM采用的是慢速协议,即当内部RAM的片选信号和TS201的写信号都为低时,将TS201内部的数据正确的写入到FPGA的内部双口RAM里。由于测试针的数目有限,所以,图中只显示了TS201的低8位地址线和低9位数据线,而RAM则只显示了低8位的数据线。

3 结束语

本文介绍了基于TS201的高速信号处理系统的硬件设计以及实现方法,着重考虑了系统的高速、实时和通用性,同时充分发挥了GA3816处理器的优势。由于结合了DSP和FPGA的强大可编程和处理能力,因此,该信号处理系统能够广泛的应用于语音及图像处理、通信、雷达、导航、电子对抗等信号处理领域。

责任编辑:gt

-

基于DSP的图像处理系统的应用研究2012-12-19 9683

-

SEP3203处理器的FPGA数据通信接口设计2018-12-05 2138

-

SEP3203处理器实现FPGA数据通信接口设计2019-04-26 2115

-

利用FPGA怎么实现数字信号处理?2019-10-17 6381

-

数字信号处理器的特点2020-12-09 2106

-

ARM Cortex-M85处理器技术参考手册2023-08-09 956

-

ARM Cortex-M85处理器软件优化指南2023-08-10 754

-

TS201在数字信号处理设计中的应用2009-03-07 515

-

Intel 64位处理器,Intel 64位处理器结构原理2010-03-26 3617

-

雷达通用信号处理系统的实现与应用2011-12-15 1023

-

苹果a6处理器怎么样_a6处理器参数2012-09-13 26708

-

基于FPGA的雷达信号处理系统设计2015-10-30 1122

-

基于FPGA的通用传感器信号处理系统设计_李辉2017-03-19 802

-

基于双TMS320VC5416处理器的实时图像搜索跟踪处理系统设计2017-10-23 1468

-

Builder数字信号处理器的FPGA设计2017-10-31 1387

全部0条评论

快来发表一下你的评论吧 !