高速串行数据通信CY7B923芯片的性能特点及设计实例

描述

1 概述

CY7B923是CYPRESS半导体公司推出的一种用于点对点之间高速串行数据通信的发送芯片。CY7B923采用的是基带传输通信方式,并支持带电插拔(热接插)。其内部电路主要包括时钟产生器、输入寄存器、编码器、移位寄存器、三对差分PECL输出对以及测试逻辑等。该芯片外转帐电路比较简单,不需单片机或微机控制,并且内置有自测试电路,因此使用比较方便。CY7B923的最大传输速率可达400Mbps,有三种传输速率的器件可供选择:标准系列的器件有CY7B923-JC、CY7V923-JI、 CY7B923-SC及CY7B923-LMB四种型号,它们的传输速率为160~330Mbps;高速系列器件有CY7B923-400JC和CY7B923-400JI两种型号,传输速率可达160~400Mbps;对一些传输速率要求不高的场合,可采用较低价格的CY7B923-155JC或CY7V923-155JI,其传输速率为150~160Mbps。CY7B923采用单一的+5V电源供电,功耗仅 350mW。可兼容光纤、IBM ESCON、DVB-ASI及SMPTE-259M等多种传输协议,适用于光纤、同轴电缆和双绞线等传输媒介。

2 引脚功能及内部结构

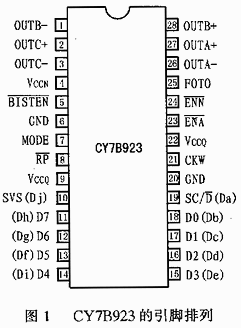

CY7B923有28脚SOIC、PLCC和LCC三种封装形式,采用 0.8μBiCMOS工艺,其此脚排列如图1所示(SOIC封装),引脚功能如表1所列。

CY7B923的内部结构如图2所示,其内部主要包括时钟产生器、输入寄存器、编码器、移位寄存器、三对差分PECL输出对(OUTA±、OUTB±及OUTC±)及测试逻辑等电路。

输入寄存器的数据输入时序和标准FIFO的数据输出时序相一致,因而不需外加逻辑电路,便可知同步FIFO芯片或异步FIFO芯片直接连接并将FIFO芯片中的数据读入到输入寄存器中,然后再发送出去。在BIST方式下,借助于内部逻辑电路,并行输入寄存器又可作为线性反馈移位寄存器,用于产生一串511字节的包含有数据、特定的有效字符码以及设定的违例码等一串伪随机序列。

编码器用于将保存在输入寄存器的数据转换为适合串行口输出的数据形式。由SC/D的输入状态来决定其编码方式:SC/D=1(高电平)时,按控制码表转换输入的数据为控制码;SC/D=0(低电平)时,按数据码表转换输入的8位数据为10位数据码。当设定MODE为高电平时,可将编码器的8B/10B编码功率屏蔽掉。

CY7B923的OUTA±和OUTB±受FOTO控制,OUTC±则不受FOTO影响,OUTC±能连续输出数据流,适用于系统进行自环测试。为减少功耗,不用的输出端均应接VCC(+5V电源),以禁止相应的输出电路工作。

3 工作原理及操作方式

3.1 工作原理

CY7B923作为点对点串行通讯中的发送芯片,其数据传输速率可达33M字节/秒(对CY7B923-400系列的芯片可达40M字节/秒)。当ENA或ENN有效(低电平)时,在CKW的上升沿,用户的8位数据或协议信息将读入发送器的输入寄存器中。然后由编码器编码后送到移位寄存器,最后在位时钟的控制下通过三对差分PECL对串行输出。

3.2 操作方式

CY7B923的发送操作方式有两种:正常使用操作方式和测试方式。正常使用操作方式又分为编码方式和直通方式(非编码方式)。测试方式用于芯片的测试、发送电路的测试和整个系统的测试。测试方式也分为内置自测试方式(BIST方式)和工厂测试方式(芯片测试方式)。下面分别给以介绍。

a.编码操作方式

在这种方式下,允许用户发送8位的数据和控制字符。译码器根据输入的8位数据(D0~D7)、数据类型控制码(SC/D)及系统测试输入位(SVS)的状态等对输入数据进行译码,若数据的内容为正常的数据码,则SC/D为低电平,且应该使用有效数据码表中的数据字符寿终正寝组来对输入数据进行编码。若输入数据的内容为控制码或协议信息,则SC/D应为高电平,且应按照有效特殊字符码和码系列等表中的字符码或码组来对输入的数据编码。

测试字符和测试码系列中包含有测试光纤通路连接的码组,这些码组也可用于测试系统连接在传输误码与定时之间的响应关系。违例字符也可以作为用户数据包的一部分发送出去(例如:发送C0.7,D7~0=11100000,SC/D),或者由外部系统通过改变SVS输入电平(SVS置为低电平)来发送违例字符。测试时,无需对系统的传输接口电路作任何改动即可使其产生传输误码,因而允许系统测试逻辑按照确定的方式来评估系统的误码率。

b.直通操作方式

在此方式下,输入的数据是已译码的10位数据即D0~9(Db-h)、(Da)、和SVS(Dj)等数据,SC/D和SVS分别作为Da和Dj的数据输入脚。这10位数据经直接串行化后即可发送出去。数据译码方式的选择可由设计者决定,对数据的译码也可通过外加电路来实现。需要注意的是:所选择的译码方式必须保证译码后数据位之间有适当的变化,以使接收器中的锁相环电路能与输入数据同步(至少每10位必须有一个数据位是变化的),但这种方式并不常用。

4 CY7B923构成发送电路设计实例

图3为由CY7B923构成的一个实际的发送应用电路。该电路主要由CY7B923发送芯片、IDT7200(FIFO)芯片、阻抗变换匹配线圈及相关的电阻和电容等组成。FIFO芯片的读信号由CY7B923的RP脚提供。CY7B923的发送控制由外部提供的ENAC和FIFO芯片的SEF信号来共同完成。通过设置拔码开关U7的相关位置可以将CY7B923发送芯片的工作方式设置在正常发送方式或内置测试方式。具体的操作方法如下;

(1)SBIST=0时,设置为内置自测试方式

此时,若ENA=1,发送器开始发送…1010…交替变化的位系列。如果用示波器测试输出端,则可看到一个近似的正弦波。

若ENA=0,则发送器开始重复发送一组测试系列码。在每一个BIST测试循环中,RP脚都将产生一个负脉冲。因而可由外部计数器或示波器来监测发送测试码组的循环次数。

(2)SBIST=1时,设置为正常使用方式

在正常使用方式时,ENA应和ENAU相连接。其工作过程为:首先用户将需要发送的一帧数据(包括用户协议和用户数据信息)写入FIFO芯片,然后再启动发送器CY7B923并由CY7B923发送出去。CY7B923在从FIFO芯片中读出数据后,先进行串-并转换,然后才将数据发送出去。当一帧数据发送完毕后,由FIFO芯片中的EP信号自动控制CY7V923,以使其停止读取FIFO芯片中的数据。此时用户可通过测试TENAS端的状态来了解FIFO芯片中的数据是否已发送完毕。若发送完毕,则可将下一帧数据写入FIFO芯片,再启动另一次发送过程。

CY7V923的应用比较简单,其发送数据率也比较高。可广泛应用于工作站、服务器、大存储器之间的互连或视频传输等领域。

责任编辑:gt

-

数据收发器CY7B923/933的性能特点和应用范围2020-08-10 3818

-

基于USB2.0芯片CY7C68013的高速数据通信接口设计2011-09-21 1534

-

基于CY7C68013的高速数据通信接口设计2011-09-08 1005

-

单片机串行数据通信2010-02-23 924

-

基于CY68013的数据通信系统设计2010-01-06 636

-

基于Matlab环境的串行数据通信2009-09-03 794

-

连接CY7B923和CY7B933(HOTlink器件)至定2009-06-16 1291

-

CY7B923用作ECL时钟源2009-06-15 973

-

MATLAB环境下的串行数据通信系统设计2009-06-12 575

-

双口RAM CY7C025 实现DSP间的高速数据通信2009-05-13 1328

-

高速串行数据通信发送芯片CY7B923的原理及应用2009-04-27 1035

全部0条评论

快来发表一下你的评论吧 !