搭建链路实现FPGA到PC的数据传输使用以太网实现信息传输

描述

问题情景:为了得到连续时间内ADC采集的数据,并在PC上对数据进行分析,需要搭建链路实现FPGA到PC的数据传输。考虑到ADC采样频率较高(10M-100Mb/s),串口通信的速率远远达不到要求,考虑使用以太网来实现信息传输。

物理链路:14位ADC;开发板使用Xilinx Spartan-6 黑金开发板AX545;超五类或六类网线;由于程序只支持千兆以太网传输,并且考虑到部分笔记本不携带网口,因此使用了USB3.0-千兆网口的网卡;装有wireshark的电脑。

FPGA部分:采用存储转发的思想,即先对ADC采集的数据进行缓存,等到采集的数据满足一帧的数据长度,再对数据包封装成帧发送,采用UDP格式进行发送。考虑到ADC时钟与UDP时钟不同步,因此先对ADC采集的数据进行一级缓存;由于以太网每次只能发送8位数据,而ADC采集的数据为14位,因此还需要对ADC缓存数据进行转换,转换得到的数据进行二级缓存;等到二级缓存达到发送数据的长度,使能UDP传输,加入帧头后发送。

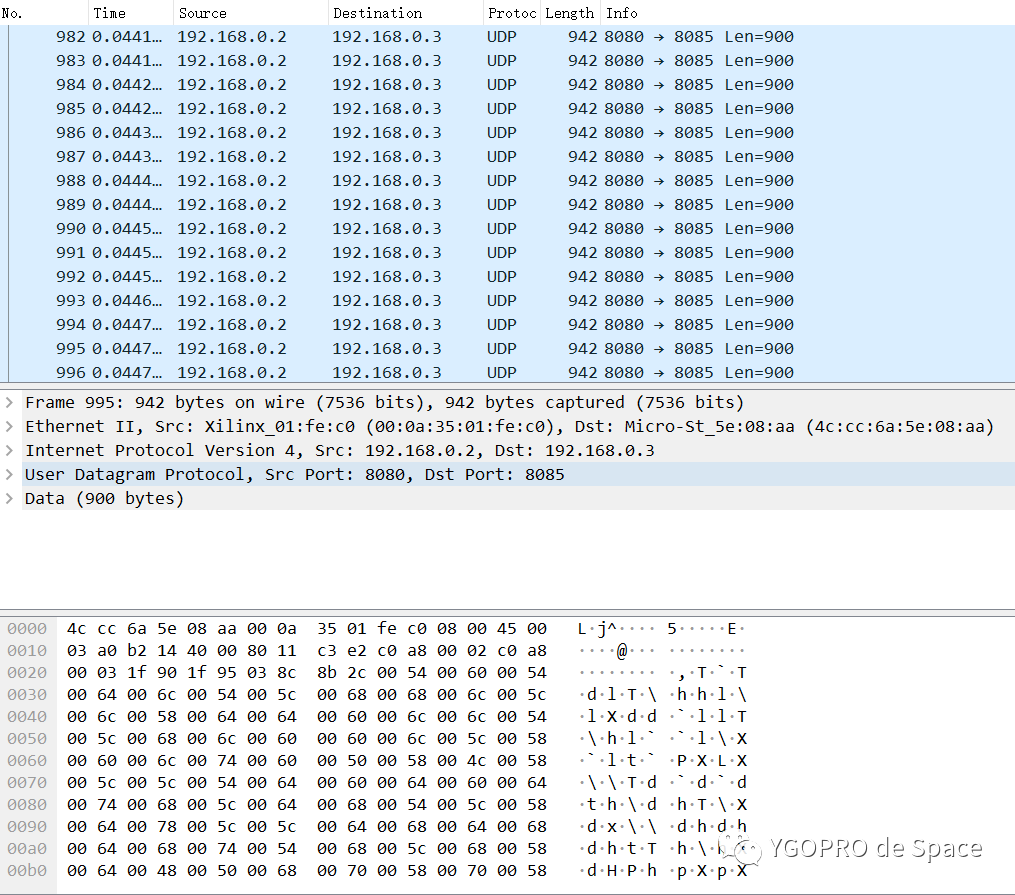

PC端接收:PC端数据接收采用wireshark实现,使用wireshark捕获UDP包。由于传输速率过快,连续时间接收的UDP包过多,因此完成采集后先对采集的数据进行存储,存为pcap格式为后续处理做准备。存储的文件较大,达到百兆到G级别。

数据恢复(未找到很好的实现方法):数据保存在UDP包的数据帧部分,格式为十六进制或二进制,需要将数据部分和其他帧结构分离。方法一:利用网络调试助手(上位机),在wireshark接收UDP包的同时打开上位机,就可以得到不含帧头部的数据流,而且可以进行保存(此处使用的NetAssist),一个致命的问题是,当数据传输速率过快时,利用上位机保存下来的帧并不是连续的,会导致恢复的波形不连续。方法二:wireshark提供追踪UDP流的功能,可以将所有帧中的数据流进行打印,但问题是得到的pcap文件中帧数据量过大,处理非常慢(严重影响使用)。方法三(考虑但未实现):利用MATLAB直接读取pcap文件,下载pcap2matlab开源文件,利用这一文件解析pcap文件;利用python dpkt包解析pcap文件。如果有合适的解决方法,欢迎交流!

原文标题:FPGA-PC以太网通信

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

MSP430实现以太网高速数据传输2013-11-07 3267

-

FPGA以太网数据传输2016-09-25 5641

-

基于FPGA和W5500的以太网传输系统实现2018-08-07 8180

-

以太网接口的设计及其数据传输的实现过程介绍2019-06-05 3942

-

如何实现FPGA和PC之间的数据传输?2019-07-31 3107

-

从工业网到以太网工业数据传输与发布的解决方案The Solu2009-06-06 600

-

基于千兆以太网的高速数据传输系统设计2012-03-09 1045

-

基于W5300的以太网数据传输系统的设计2012-05-28 2116

-

基于FPGA和W5300的以太网数据传输系统的设计与实现2012-05-29 2793

-

一种基于FPGA的以太网高速传输平台2016-02-25 876

-

以太网数据传输系统的设计与应用介绍2017-11-16 1244

-

基于FPGA的千兆以太网CMOS图像数据传输系统设计2018-04-03 1347

-

光纤接口转为以太网接口数据传输系统的实现方法2022-02-09 7701

-

基于W5300的以太网数据传输系统的设计与实现2023-10-24 561

-

以太网接口的数据传输原理详解2024-05-29 4313

全部0条评论

快来发表一下你的评论吧 !