基于模数转换器实现宽带接收机的设计及参数分析

描述

宽带接收机设计需要采用外差体系结构,以便在有干扰或者阻塞信号的情况下获得最佳灵敏度。以蜂窝cdma2000?多载波接收机设计为例,本文讨论某些影响模数转换器(ADC)选择的重要参数—IF频率、接收机模拟功率增益、信号带宽和ADC采样时钟频率等参数。通过这一设计实例,还讨论了以下ADC参数:满量程(FS)功率、小信号噪声底(SSNF)、信噪比(SNR)和无杂散动态范围(SFDR)。16位、80Msps MAX19586 ADC在当今所有的ADC中具有最低的噪声底,在接收机设计中不需要降低增益或采用自动增益控制(AGC)。MAX19586优异的噪声性能以及SFDR性能能够满足甚至由于此类应用对ADC的要求。

外差接收机包括一级混频器(LO1),将RF波形转换为第一中频(IF)信号(图1)。可以对这一IF信号进行数字化处理或送入第二级混频器(LO2),将其转换为频率更低的IF。把信号转换到更低IF利用了ADC良好的噪声和线性性能,这些性能一般在低频输入时才能够获得。采用欠采样技术数字化真实的带通信号,其采样速率在信号带宽内符合Nyquist定律,而不针对其绝对频率。使用这一方法,ADC对真实信号进行数字化,然后利用数字信号处理(DSP)技术,在数字域将其转换为合成分量。这种方法的优势在于能够降低硬件的复杂性和成本,因为欠采样技术承担了部分下变频任务。但是,这种体系结构需要时钟速率较高的ADC,以及较宽的动态范围(即低噪声和高线性)。欠采样技术除了这些优点之外,一个重要的缺点是噪声混叠,如果输入信号没有进行充分的带宽限制,将对带内的混叠噪声进行数字化处理并和有用信号一起转换成基带信号,噪声混叠将导致ADC的SNR下降。

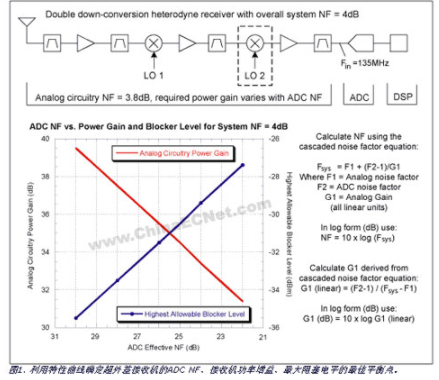

图1所示框图是蜂窝基站系统采用的典型二次下变频接收机,这类接收机一般包含两个相同的接收通道,提供分集接收。如果取消第二级混频器,则可得到一次变频架构。假设ADC需要量化三个相邻的cdma2000载波,每个载波的带宽约为1.23MHz。这些载波信号转换后将通过数字信号处理器(DSP)进行滤波。例如,ADC的时钟速率为cdma2000载波码率1.2288Msps的64倍,即78.64Msps。对于欠采样接收机,时钟速率决定了奈奎斯特带宽(fCLK/2),该指标是计算ADC等效噪声系数(NF)的重要参数。

假定系统噪声系数(NF)的设计目标是4dB,模拟电路部分提供的噪声系数为3.8dB。在忽略阻塞干扰的情况下,为了满足系统接收灵敏度的要求,只允许ADC为系统增加0.2dB的噪声系数。需要注意的是4dB的噪声系数远远优于3GPP2 cdma2000标准的要求,但它代表了众多蜂窝基站制造商的设计目标,以便与最低要求相比留出足够的裕量。图1给出了在满足系统噪声系数设计目标的条件下,模拟功率增益和ADC NF与天线端所能容许的带内干扰(阻塞)的对应关系曲线(没有使用自动增益控制)。对模拟电路功率增益的要求取决于ADC的等效噪声系数,而等效噪声系数是由已知的满量程功率电平(以dBm为单位)、SSNF、转换速率计算得到的。

图2表示没有滤除的噪声混叠到有用信号频带的过程,这将提高ADC的SSNF,降低信噪比(SNR)。上述示例中,三个cdma2000射频载波信号下变频至135MHz、带宽为5MHz,并送入ADC的输入端。输入信号经ADC产生的2次与3次谐波不会混叠到有用信号频带内,可以忽略不计。图2仅给出了5个奈奎斯特频段,实际上直到16倍奈奎斯特频率的信号都会混叠到有用信号带宽内,这里假定ADC的满功率输入带宽达到了600MHz。这些混叠信号如果不进行适当衰减,将会降低ADC的噪声性能。

假定采样频率为78.64Msps,有用信号带宽为5MHz,混叠频带从DC至629.12MHz (8 x fCLK),中心频率分别为22.28MHz、56.36MHz、100.92MHz、179.56MHz……,606.84MHz。3次和5次混叠频带的中心频率分别偏离奈奎斯特频率边缘f1和f2。总的来说,除了在135MHz存在有用信号外,另外还有15个混叠信号,如果只有一个混叠信号进入ADC的输入端口,将使ADC噪声系数NF增大10 x log(2) ,或3dB。如果带内所有噪声均进入ADC,理论上ADC的有效噪声系数(NF)将会增大10 x log(15),或11.8dB,此时假定ADC对有用信号和各混叠噪声信号的量化效果相同。

为了滤除混叠频带内的噪声,靠近高边混叠(》177.06MHz)和低边混叠(《103.42MHz)频带的衰减量应该不低于16dB,以便使混叠信号对ADC噪声系数的影响低于0.2dB。更高的衰减量可以更大程度地降低混叠信号对ADC噪声系数(NF)的影响。

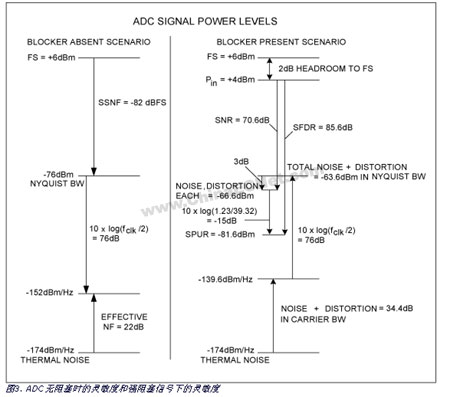

以cdma2000为例,图3给出了在以下两个条件下对ADC性能的要求:a)不存在阻塞时的接收灵敏度;b)存在阻塞时指标降低后的接收灵敏度。

为了计算以上两种情况下ADC的等效噪声系数,假定ADC输入等效匹配电阻为200,计算其满量程(FS)功率电平。如果满量程输入电压峰值为2.56VP-P,对应的满量程输入功率为+6dBm (RMS)。不存在阻塞信号时,假定ADC的SSNF为-82dBFS,对于78.64Msps的采样频率,奈奎斯特带宽内的ADC噪声基底电平为-76dBm。折合到1Hz带宽内,其基底噪声电平为-152dBm;与常温下-174dBm/Hz的热噪声基底相比较,ADC的等效噪声系数为22dB,此时假定在奈奎斯特频带内所有频率的噪声频谱保持平坦。由此看来,达到这一噪声系数指标非常困难,但是,MAX19586完全能够满足该设计要求。

从图1可以看出,当ADC等效噪声系数为22dB时,为了使系统的噪声系数达到4dB,模拟电路必须提供31.4dB的功率增益。考虑到这些因素,在不采用自动增益控制的前提下,系统可容许的最高有效值阻塞功率为-27.4dBm,如图3中给出的功率电平所示:

FS - 余量 - 增益 = +6dBm - 2dB - 31.4dB = -27.4dBm

在很多接收机中,如果存在较高电平的阻塞,则需使用自动增益控制电路,以便存在较强阻塞信号时降低接收机的模拟增益。然而,降低增益会导致整个接收机噪声系数的增加,从而降低所要达到的接收灵敏度。多载波接收机中,强阻塞信号条件下,降低灵敏度对弱载波信号提取非常不利。如果ADC有非常低的噪声基底(如MAX19586),则在达到同样灵敏度的条件下对射频前端的增益要求较低,从而使接收机可以在不使用AGC的情况下容许更强的阻塞信号。

当带内阻塞信号和cdma2000载波同时出现在天线端口时,3GPP2标准允许接收灵敏度降低3dB。该指标的降低考虑到了模拟电路以及ADC电路的噪声+失真的提高。假定分配1dB给模拟电路,2dB给ADC,系统的噪声系数(考虑失真)将从4dB提高到7dB,增益仍然为31.4dB;模拟电路的噪声系数(考虑失真)为4.8dB。由此,可以计算出系统噪声系数为7dB时,ADC的噪声系数(包括失真)为34.4dB,或-139.6dB/Hz (图3所示)。在奈奎斯特频带内,等效噪声(包括失真)电平为-63.6dBm。

假定ADC的噪声和杂散功率对整个ADC噪声系数的影响为3dB,即在奈奎斯特频带内的噪声功率为-66.6dBm。将此功率电平与在ADC输入端口的4dBm阻塞信号相比较,可以得到其信噪比要求,70.6dB。有用信号频带内噪声功率的计算可以采用如下方式,将cdma2000信号带宽除以整个奈奎斯特带宽即可。这种情况下,载波频带内的噪声功率比-66.6dBm低10 x log (1.23MHz / 39.32MHz)或-15dB (即-81.6dBm)。因为假定噪声和失真功率相等,杂散功率同样为-81.6dBm,因此ADC的SFDR指标为-85.6dB,如图3所示。

综上所述,本文讨论了欠采样接收机中最重要的系统级参数,并给出了计算FS、SSNF、SNR、SFDR的方法,为合理选择ADC提供参考。Maxim的MAX19586是以上欠采样接收机设计中的最佳选择。

责任编辑:gt

-

模数转换器的技术参数详解2024-05-21 3454

-

14位模数转换器SC1252在多模式数字接收机的应用2023-07-13 1280

-

模数转换器SC2245-10在宽带通信接收机中的应用优势2023-04-04 945

-

AD9691BCPZ-1250模数转换器2019-05-15 758

-

AD9627ABCPZ-105模数转换器现货2018-11-14 1615

-

AD9691BCPZ-1250模数转换器现货2018-11-09 1513

-

AD6645ASVZ-105模数转换器2018-11-02 1905

-

AD9444BSVZ-80模数转换器2018-11-01 1338

-

AD9445BSVZ-105模数转换器2018-10-31 1954

-

AD9690BCPZ-500模数转换器(ADC)2018-06-05 1890

-

数模和模数转换器2009-09-16 7942

全部0条评论

快来发表一下你的评论吧 !